基于FPGA与谐波合成信号发生器的实现

张新+吴凤云+王帆

摘 要: 提出一种结合傅里叶级数展开和DDS原理产生任意波形信号发生器的实现方法。利用FPGA设计了15个DDS模块,将一周期正弦波的样值写入DDS模块的ROM表。对目标信号进行傅里叶变换得到信号各次谐波的频率和幅值,取其1~15次谐波的频率作为每个DDS模块的频率控制字,将各个DDS模块输出的样值与输入该模块的频率对应谐波幅值的乘积进行累加,经低通滤波器输出最终所需波形。测试表明,利用该实现方法得到的信号发生器输出波形稳定、频率转换速度快、精度在0.002 79 Hz以内。

关键词: FPGA; DDS; 谐波合成; 信号发生器; ROM; 频率转换速度

中图分类号: TN911.7?34; TN741 文献标识码: A 文章编号: 1004?373X(2018)02?0174?05

Abstract: An implementation method of the signal generator which can generate the arbitrary waveform by combining Fourier series expansion and DDS principles is proposed. The FPGA is used to design 15 DDS modules, and write the sample values of a periodic sine wave into the ROM list of DDS modules. The Fourier transform is performed for the target signal to get the frequency and amplitude of the signals each harmonic. The frequencies of 1?15 harmonics are taken as the frequency control words of each DDS module. The sample values output by each DDS module and the product of harmonic amplitudes corresponding to the frequency input into this module are accumulated. The analog signal is output through the low?pass filter to get the desired waveform. The test results show that the signal generator implemented with the method has stable output waveform and fast frequency conversion speed, and its accuracy is within 0.002 79 Hz.

Keywords: FPGA; DDS; harmonic synthesis; signal generator; ROM; frequency conversion speed

0 引 言

传统的波形发生器只能产生一些常规的信号如正弦波、方波、脉冲波、三角波等。随着科学实验研究的需求不断发展,传统的波形发生器在一些特定的场合已经不能满足要求,许多应用研究领域需要一些不规则的信号用于系统特性的研究,这就需要能产生现场所需波形的任意信号发生器。

任意信号发生器的实现方案主要有可变时钟计数器寻址[1],DMA输出和直接数字频率合成(DDS)[2]等多种方式。目前任意信号发生器的研制主要是基于FPGA编程技术以及DDS原理,采用上位机软件编辑任意波形时域数据,通过改写FPGA中波形ROM的数据,从而生成所需的各种任意波形[2?4]。但是,对于只读存储器(ROM)数据的改写必须每次通过程序初始化波形ROM,写入的数据必须是一整周期的时域波形数据,不易操作。为了能够更加简洁的改写波形存储器的数据,把存放波形量化表的ROM换成了可以改写的RAM,这样通过与RAM的接口可以改变存放在波形RAM中的数据从而实现任意波形发生器[5?8]。然而,RAM作为一种随机读写存储器,在仪器掉电或重启后,RAM中数据就会丢失,因此,这种方法在每次使用时都要重写RAM数据。为了能够稳定地产生波形数据,在信号波形输出的算法中,采用一种在硬件设计中改进的DDS技术,通过使用多个参考频率源和动态生成的波形数据方法以改进稳定性和减少输出波形的失真[9]。另一种被广泛采用的解决方案是使用DDS芯片产生正弦波,然后使用放大器、比较器、组合电阻器和电容器将正弦波转换为矩形波和三角波等其他的波形[10]。但这种方案只能产生特定的波形,在任意波形实现方面具有局限性,芯片功耗较大,生产成本高。

考虑到实际应用中的信号的主要能量集中在1~15次谐波,故本文采用一种新的方法,通过对DDS进行理论分析。详细介绍了利用FPGA芯片设计15个DDS模块,每个模块的波形ROM均存入一个周期正弦波样值。正弦波形的样值数据无需更改并且防止在掉电时丢失数据,因此,在波形数据的存储设计上采用ROM存储方式,定制ROM的文件(.mif)由Matlab生成[11]。将信号最多15次谐波的频率及其对应幅值作为FPGA的输入信号,FPGA中完成不同频率正弦波的叠加输出。测试表明,本文采用的实现方法在输出波形参数写入、删除、修改等方面更加灵活,操作简单,输出波形的频率精度能够满足设计要求。

1 理论分析

现将整个周期的相位分成M份,则最小的相位增量为,若每次的相位增量选择为最小相位增量的K倍,完成一整周正弦波的输出需要经过个参考时钟周期,则输出信号的频率计算如下:endprint

式中:一般取,N为正整数,表示相位累加器输出字长;K为频率控制字;为时钟频率,相位累加器在时钟的控制下以步长K为累加,输出N位二进制码为波形ROM的地址,对波形ROM寻址,波形ROM输出的幅值经数/模转换器转换成模拟信号后再经低通滤波器输出。

DDS原理图如图1所示。

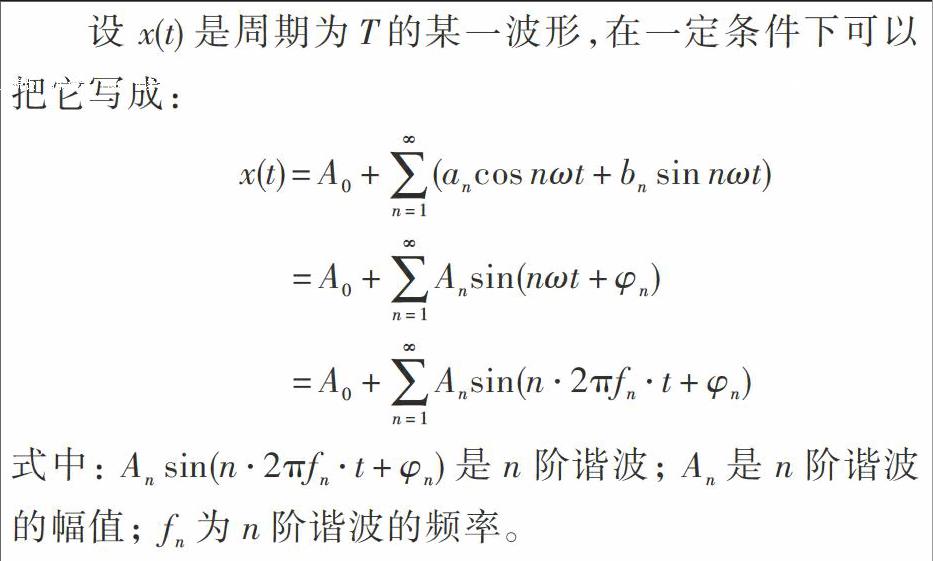

在物理学中,最基本的波形是谐波(正弦波),它是形如,其中A是振幅,是角频率,是初相位。对于矩形波、锯齿波等任意波形都可以用一系列谐波的叠加表示。

设是周期为T的某一波形,在一定条件下可以把它写成:

2 波形合成系统的总体设计

本系统在控制方面采用NXP公司推出的基于ARM Cortex?M3 内核的微控制器LPC1768,FPGA内实现信号发生器的数字电路部分。整个系统主要由LPC1768微处理器、FPGA模块、DAC转换单元、低通滤波器(LP),USB通信端口、LCD显示模块和按键控制等部分组成,其系统设计框图如图2所示。

2.1 微控制器设计

嵌入式软件是在一个精简的小型实时性操作系统的基础上实现信号的可编程输出。微控制器(MCU)内部FLASH存储区为波形数据分配了32 kB的存储空间(0x010000~0x017FFF),每种波形数据占4 kB的空间,因此在FLASH中可存储8种波形。对波形数据的写入和删除操作是通过配置控制器USB虚拟的串口来接收PC端的写入和删除命令来完成,在写入文件过程中,首先是将所需合成波形的15种谐波频率(Freq0~Freq14)以及每个频率对应的幅度参数(ACAmp0~ACAmp14)组合为一个文本文件,然后在PC端通过串口助手将该文件的波形数据写入到对应的FLASH存储区。程序运行过程中,通过按键选择某一波形作为输出波形,微控制器将最多15种谐波的频率转换为频率控制字以及将幅度参数(4 V范围内)转化为16位二进制的表示方式,然后通过SPI的方式写入到FPGA各个对应的寄存器中,FPGA启动DDS模块转换,最终产生所需的合成波形。同时,微控制器运行的操作系统还需要处理各种中断(包括USB的中断,按键的中断)以及LCD的显示等操作。

2.2 FPGA部分设计

FPGA主要实现以下两部分功能:第一,系统的按键扫描由FPGA来完成,FPGA实时监控是否有按键按下,当发现有按键输入时,将去抖后的按键值保存,再以中断的方式发送至MCU单元;第二,利用FPGA实现DDS原理,单个DDS模块的RTL视图如图3所示,其中Freq[31:0]为频率控制字K,该频率控制字即为FPGA存储的15种频率控制字的一种,加法器ADDER与32位的相位寄存器构成相位累加器,相位寄存器的输出Phase[31:0]又反馈到加法器的输入端进行下个时钟周期的累积,截取相位寄存器Phase[29:20]位作为正弦波ROM的地址RomAddr[9:0],因此,地址的可变范围为1~1 023,调用IP 核形成波形存储器时需要加载ROM 初始化数据文件(SinRom.mif 文件)即为对一个周期正弦波1 024点的量化存储。

本系统FPGA部分设计了15个DDS模块,能够同时进行最多15种频率的合成,对于一些幅值为零的谐波,通过程序控制失能(Enable=0)其DDS模块转换,只进行部分谐波的合成,各个模块的输出分别为DDS0_DataOut~DDS14_DataOut。

将DDS0_DataOut~DDS14_DataOut乘以其对应的幅值Reg30_OUT0~Reg3E_OUT0(保存ACAmp0~

ACAmp14的二进制值),再将所得结果输入加法器进行累加,最后輸出所需波形幅值量化数据。其FPGA实现幅值叠加如图4所示。

这里使用DDS0和DDS1作为示意原理图,其余模块的实现采用相同的原理进行叠加,因此,在FPGA能够实现15个模块同时叠加。FPGA采用32 bit宽度的频率控制字,时钟为12 MHz,其输出信号频率为:

频率精度为:

2.3 DAC电路设计

由FPGA输出的数字幅度值是一串数字序列,最终要经过D/A 转换器才能转换成相应的模拟波形。为了保证数据处理结果的准确性,DAC转换器必须有足够的转换精度,同时为了能够在较高频率下工作,它必须有足够快的转换速度。此外还要考虑 DAC 的非线性和噪声特性,综合了各方面的因素之后,本设计采用16 bit并行DACDAC8820作为数/模转换芯片。经FPGA单元计算之后的数字波形数据由DAC1_D0~DAC_D15输入DAC单元进行转换,转换之后模拟信号经一阶放大电路,最终由DAC1_OUT输出,具体电路设计如图5所示。

2.4 滤波电路设计

由于运算放大器具有近似理想的特性,且可以省去电感,得到接近理论预测的频率响应特性,构成有源滤波电路后还具有一定的电压放大和缓冲作用,并能减小体积。综合考虑,系统采用运算放大器构成二阶低通滤波器,电路原理图设计如图6所示。

通过选择高精密度超低噪声运放、精心设计包含低通滤波器在内的模拟加法电路以及合理PCB的设计,能够有效地降低噪声。

3 测试分析

3.1 输出波形测试

首先,通过Matlab软件仿真出所需合成的波形,得到合成波形的频率及幅值参数;然后,将仿真所使用的参数写入到该信号发生器;最后,使用示波器截取最终的合成波形与仿真波形进行对比分析。

矩形波、锯齿波、任意波形Matlab仿真如图7a)~图9a)所示,从3幅可以得出所需合成的波形峰峰值为2,波形的周期T为1,对应的频率。

上述3种波形的示波器观测波形如图7b)~图9b)所示,示波器垂直方向的方格表示输出波形幅值,每个方格代表500 mV,从图中能够直观地看出上述3种波形在垂直方向上均占了4个方格,因此峰峰为2 V。水平方向的方格表示波形频率值,每个方格代表200 ms,一个周期的该波形占了5个水平方格,因此,波形的输出频率为1 Hz。endprint

由此,可以得出实测输出波形的幅值及频率数据与Matlab仿真波形的数据完全吻合,并且,实测波形与仿真的波形的形状也十分接近。

3.2 频率稳定度测试

矩形波、锯齿波、任意波形的频率测试值如表1~表3所示,由表中数据可以看出,每种波形在不同频率下3次测量值都比较稳定,无较大波动。频率变化量的最大值为 0.002 1,在0.002 79以内,满足设计要求,并且频率稳定随频率变化无明显变化规律,在可达范围内相对频率稳定。

4 结 论

本文系统实现了基于FPGA合成谐波的信号发生器设计,在任意波形的实现过程中,只需在PC端更改最多15种谐波频率值及其对应幅值,即可实现任意所需波形输出。操作更加灵活,而且更加高效。测试表明,通过仪器合成的最终波形无论是波形形状,还是输出波形的幅值及频率值都与Matalb仿真波形十分接近。

输出波形的频率值比较稳定,频率精度在0.002 79以内,满足设计的要求。然而,对于矩形波和锯齿波等这些比较特殊的波形,由于所有FPGA芯片内存以及设计工艺的限制,不能输出幅值比较平滑的波形,但是足以满足对于幅值要求不是很苛刻的实验室以及工程应用的需求。

参考文献

[1] 白居宪.直接数字频率合成[M].西安:西安交通大学出版社,2007.

BAI Juxian. Direct digital frequency synthesis [M]. Xian: Xian Jiaotong University Press, 2007.

[2] 周登荣,周玉荣.一种任意波形信号发生器的实现方法[J].重庆师范大学学报,2014(1):84?88.

ZHOU Dengrong, ZHOU Yurong. An implementation method of arbitrary waveform signal generator [J]. Journal of Chongqing Normal University, 2014(1): 84?88.

[3] 韩旭,郑磊.基于FPGA的任意波形发生器的设计与实现[J].电子测量技术,2013(7):62?66.

HAN Xu, ZHENG Lei. Design and implementation of arbitrary waveform generator based on FPGA [J]. Electronic measurement technology, 2013(7): 62?66.

[4] RAVITEJA REDDY B, RAJU V S G N. Development of FPGA for custom waveform generator based on direct digital synthesizer [J]. International journal of engineering research and applications, 2013, 3(4): 2597?2602.

[5] 张严,洪远泉.基于FPGA的任意波形发生器设计与研究[J].现代电子技术,2011,34(10):157?159.

ZHANG Yan, HONG Yuanquan. Design and research of arbitrary waveform generator based on FPGA [J]. Modern electronics technique, 2011, 34(10): 157?159.

[6] FERNANDEZ?JARAMILLO A A, ROMERO?TRONCOSO R D J, DUARTE?GALVAN C, et al. FPGA?based chlorophy II fluorescence measurement system with arbitrary light stimulation waveform using direct digital synthesis [J]. Measurement, 2015, 75: 12?22.

[7] MAFFRAND C, ZARATE D, AON M A, et al. Arbitrary waveform generator using FPGA for applications in ultrafast scan voltammetry [C]// Proceedings of 2014 IEEE Conference on Programmable Logic. Buenos Aires: IEEE, 2014: 1?6.

[8] ZHANG Hongfei, LUO Chunli, TANG Pengyi, et al. High?speed arbitrary waveform generator based on FPGA [C]// Proceedings of 2013 IEEE Nuclear Science Symposium and Medical Imaging Conference. Seoul: IEEE, 2013: 1?5.

[9] WEI Peng, GAO Tingjin. Arbitrary waveform generator based on improved DDS technology [J]. Applied mechanics and materials, 2013, 338: 1587?1592.

[10] XU Min, HU Jingyu, GAO Yinyin. FPGA?based design and implementation of arbitrary waveform generator [C]// Proceedings of 2011 International Conference on Control, Automation and Systems Engineering. Singapore: IEEE, 2011: 1?4.

[11] 张博君.DDS任意波形发生器研究[J].现代电子技术,2012,35(14):100?102.

ZHANG Bojun. Research on arbitrary waveform generator of DDS [J]. Modern electronics technique, 2012, 35(14): 100?102.endprint