一种分布式半实物仿真测试前端系统的研究

苏宇,孔璐,张弢,王金波,周珊

(中国科学院空间应用工程与技术中心,北京100094)

随着载人航天工程步入交会对接阶段,航天器复杂度越来越高,有效载荷的种类越来越多,且具有接口多、技术指标高、数据速率高、数据类型多的特点。同时在整个飞行任务中,软件扮演的角色越来越重。随着DSP以及FPGA的大量使用,个别载荷模块可能同时包含1553B总线接口、CAN总线接口、RS422总线接口、低电压差分信号(Low-Voltage Differential Signaling,LVDS)接口等,软件规模庞大,这都在客观上加大了整个飞行任务的风险。因此在做载人航天高可靠软件测试时,单个仿真测试前端由于受硬件资源的限制无法全部实现对以上接口的仿真,而常见的商业化分布式仿真平台往往因对外接口单调、应用软件操作界面较为复杂[1]、价格昂贵、体积庞大等因素难以融入到现有的测试环境中。

综上所述,文中在对分布式仿真测试技术以及半实物仿真测试技术简单分析的基础上,由配置项级的航天嵌入式软件第三方评测中的具体测试需求出发,以上述部分典型通信接口为例,设计并实现了分布式半实物仿真测试系统前端,再通过测试监控终端、测试服务器以及被测设备等设备组成分布式半实物仿真测试系统。

1 分布式和半实物仿真测试系统简介

1.1 分布式仿真测试技术

分布式仿真技术通常用网络连接各个仿真系统,以此来完成各系统间信息的交互,扩大仿真的规模[2]。分布式仿真技术的出现完美的解决了不同仿真平台之间信息的交互,被广泛应用于各类系统的设计和测试中,将网络模拟技术的应用提升了一个层次。分布式系统没有标准的统一时间或时间基准,但是分布式系统对时钟同步有更高的要求[3]。

常用的网络时钟同步技术有网络时钟同步协议NTP(Network Time Protocol)以及 IEEE1588 精准时钟同步协议。NTP同步技术虽然开放、安全,但是同步精度不够高,在局域网内的同步精度为1毫秒[4];2002 年出现的 IEEE1588(Precision Time Protocol,PTP)[5]是一种精密时钟同步协议[6]。PTP协议可以在不增加硬件成本的条件下[7],为网络上亚微秒级的同步精度的设备提供一个标准方法。IEEE1588精准时钟同步协议的实现方式有纯硬件方式和纯软件方式。前者采用硬件实现的时,在MAC层获取并发送时间戳,能够达到纳秒级的同步精度[8];后者采用PTPd(开源IEEE1588协议代码)实现,在应用层获取时间戳,同步精度为微秒级,但前者的开发难度较大。

IEEE1588精准时钟同步协议采用主、从的方式在网络内进行时间同步。IEEE 1588定义了4种时钟报文类型:同步报文、同步跟随报文、延迟请求报文和延迟请求响应报文[9]。

1.2 半实物仿真测试技术

半实物仿真(Semi-physical Simulation)又称硬件在回路仿真(HITL:Hardware-In-the-Loop Simulation)[10],它由仿真技术发展到一定阶段的产物。这种半实物仿真系统的行为特点为对规律比较清楚的部分建立数学模型,并在计算机上实现[11],如伺服电机系统或传感器等;对比较复杂的部分或被测设备采用实物取代数学模型,以此来获得更真实的测试或仿真结果。由于在仿真回路中接入了实物,因此硬件在仿真系统中必须是实时运行[12]。实时性在这里主要体现为采用实时化的嵌入式Linux对测试前端测试任务实时调度。

标准Linux内核实时化的方法有打Xenomai实时补丁、RTLinux实时补丁或RT-Preempt补丁(Linux官方推出)等方式。Xenomai是Linux内核的强实时扩展框架,它能无缝地集成到Linux环境中[13],能够提供微秒级实时精度[14];RTLinux也是一种双内核的且能为Linux内核提供硬实时性能的解决方案,该方案在被Windriver收购后停止发展。前两种方法对Linux内核源码的修改量大,开发难度大,且难以保证系统的稳定性[15];再加上实际工程应用中,实时内核中的进程无法直接访问标准Linux内核提供的服务且实时任务数量不多,大部分工作由非实时内核完成;实时抢占补丁(RT-Preempt)是由Ingo Molnar和Thomas Gleixner更新维护,和其他微内核中通过增加实时抢占方法不同[16],RT-Preempt对标准Linux内核进行修改,使其满足软实时性能,可以应用于一些对实时性能要求不是很高的场合。

综上所述,分布式系统时钟的同步能力和实时性是分布式半实物仿真测试系统的两个重要指标。

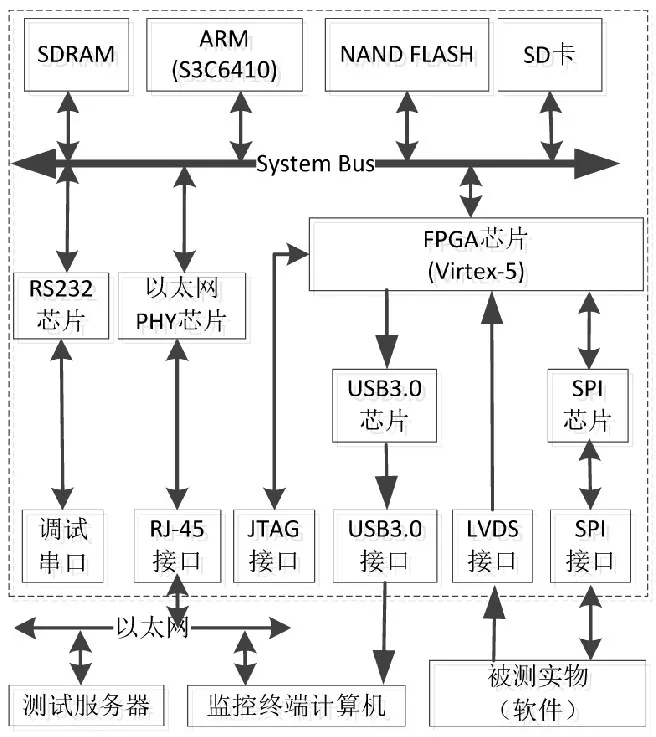

2 系统硬件设计

本文以LVDS高速数据的接收、转发以及SPI指令帧的收发处理前端为例,设计并实现半实物仿真测试前端。为了使设计更具通用性,本设计采用具有ARM+FPGA通用架构的核心板辅以对外接口的底板组成。底板由电源、调试串口、以太网以及SD卡等组成的通用接口和由SPI、LVDS等组成的专用接口构成。测试前端的硬件结构框图如图1所示。

图1 系统硬件结构框图

2.1 ARM处理器和FPGA芯片

分布式半实物仿真测试前端的微处理器作为前端的控制核心,采用的是三星公司的S3C6410(ARM11),该款处理器最高主频可达667 MHz,内部资源丰富,并支持多种外部设备;作为前端中时序和数据处理的核心,FPGA芯片采用的是Xilinx公司的Virtex5系列的XC5VLX110T芯片,与ARM处理器之间采用三态总线相连。

2.2 USB3.0芯片

在USB3.0标准中,最大传输速度达到了5.0 Gbps,几乎是传统USB2.0传输速度的10倍。在本文中,USB3.0控制器采用的是CYPRESS公司的FX3系列CYUSB3014-BZX款芯片,该芯片集成了200MHZ的ARM9控制器,512 kB字节的RAM以及USB3.0的物理层,具有可编程的100 MHz的GPIF II接口。由于该款芯片具有一个可进行配置的通用可编程接口GPIF II,因此本设计中采用CYUSB3014与FPGA芯片进行直连。

2.3 其他接口芯片

在本设计中,RS232芯片采用的是MAX202E,是一款通用的RS232协议芯片;NAND Flash芯片采用一片三星公司容量大小为1 GB的Flash芯片,型号为K9G8G08U0A;SRAM采用2片三星公司每片容量为128 MB,型号为K4X51163PC的芯片。

3 系统软件设计

分布式半实物仿真测试系统由测试监控终端、测试服务器、分布式半实物仿真测试前端、被测设备(软件)等组成。

在这里,监控终端用于测试指令序列建模、参数配置、发送、测试结果数据的观测及判读等;测试服务器的作用是存储测试序列以及测试原始结果数据,本文采用的是大型关系型数据库——IBM DB2,该数据库具有稳定,高效,操作简单等特点;分布式半实物仿真前端用于仿真被测设备的外部交联设备,实现测试任务的调度、测试指令序列以及测试反馈数据的处理

在本设计中,要求前端能够实时处理测试监控终端发送的测试指令序列,还要求能够实时接收并显示数据量不是很大的测试结果序列,同时对于数据量较大、速率较快的LVDS下行数据包,应能实时将其通过FPGA芯片经由USB3.0接口存入测试监控终端或测试服务器的硬盘中,供测试人员分析。因此在分布式半实物仿真测试前端的ARM上移植经过改造的嵌入式Linux操作系统,根据具体的测试需求,建立相应优先级的任务序列,嵌入式操作系统只需根据优先级对测试任务进行调度处理。

3.1 Linux操作系统的改造与移植

在Linux内核官网下载内核源码及与内核版本相匹配的RT-Preempt补丁,并给标准Linux内核打上RT-Preempt补丁,并在配置内核时启用CONFIG_PREEMPT_RT内核选项、启用“Thread Softirqs”和“Thread Hardirqs”内核选项(如果有),同时禁用所有电源管理选项如ACPI或APM。保存内核配置、编译内核并生成内核映像文件。

RT-Preempt补丁针对标准Linux内核的改变主要有:

1)把中断处理器变为可被抢占的内核线程;

2)细化内核时钟的颗粒度;

3)将影响内核实时性的内核自旋锁用rtmutexes实现;

4)为内核里的自旋锁和信号量实现优先级继承。

由于默认状态下,该款嵌入式Linux与外设通信的位宽为8 bits,为了提高系统的通信能力,将UBoot中Board/Samsung/smdk6410路径下smdk6410.c文件中函数DM9000_pre_init()中的宏SROM_BC4_REG和SROM_BC5_REG的值修改为0x22032200,编译并生成uboot.bin文件,这样嵌入式Linux与外设通信的位宽由BYTE变为了WORD,通信效率提升了一倍。

将编译好的uboot.bin文件、内核映像文件以及文件系统YAFFS2存放在已经处理好的SD卡中,通过SD将嵌入式Linux烧写到分布式测试前端中。

3.2 分布式系统时钟同步的实现

文中采用纯软件的方式——PTPd实现的PTP协议来完成测试前端之间的时钟同步。PTPd程序由C语言开发,在用户空间获取并发送时间戳,主要由IEEE1588协议引擎、最佳主时钟算法、时钟伺服系统、数据包处理、网络服务、时间戳模块、启动初始化、定时器以及其他模块组成。

在同一个分布式系统内选取一个测试前端作为分布式测试系统的主时钟,则其他前端均视为从时钟。在PC机上采用交叉编译器编译PTPd1.1.0代码,生产可执行目标文件,下载至各个分布式测试前端板中再通过应用程序按照先后顺序启动系统内的主、从时钟同步程序。在本设计中,分布式仿真测试前端板的时间为嵌入式Linux的上电开机时间,即为2000年1月1日零点零分。主从时钟的晶振都27 MHz。

3.3 嵌入式Linux驱动程序设计

所谓设备驱动程序就是控制与管理设备数据收发的软件,是应用程序与硬件设备沟通的桥梁。驱动程序屏蔽了硬件的细节,把设备映射为一个特殊的设备文件,用户程序可以像对其他文件一样对此设备文件进行操作。Linux内核中已经集成了常见芯片的驱动程序,如CAN总线驱动、RS485驱动以及以太网驱动等。但在本设计中,FPGA芯片作为外设挂在系统总线上,但嵌入式Linux内核中并未包含其驱动程序,因此需要开发针对FPGA的驱动。

在这里,将FPGA作为文件进行处理,通过open()和close()系统调用函数完成对设备的打开和关闭处理;通过__init fdev_init(void)函数为设备进行注册设备号、开辟内存堆栈空间;通过__exit fdev_exit(void)函数实现注销设备以及回收内存堆栈空间;通过read()、write()、ioctl()等常规的文件操作对目标设备进行操作。

驱动程序可以直接编译进Linux内核代码中,在Linux启动时加载;也可以采用内核模块的方式,待系统启动后动态加载到内核中。在本设计中采用驱动模块动态加载的方式,便于修改和调试。

3.4 嵌入式Linux应用程序设计

根据具体的测试需求,可以将测试任务分为直接任务、定时任务以及同步任务,直接任务即测试前端收到测试指令后直接执行;定时任务即同一个测试前端收到多个按照一定时间顺序执行的测试指令序列;同步任务即不同测试前端分别收到一个或多个按照一定时间顺序执行的测试指令序列。本文中用户的应用程序典型框架如图2所示。

图2 系统软件结构框图

系统上电后,首先对测试任务进行建模,继而通过测试监控终端配置测试指令序列参数并发送测试指令序列,测试前端系统解析该指令并转发至被测设备;接着通过监显终端实时观测测试前端系统转发的测试指令序列的执行情况以及测试结果的正确性。

3.5 应用FPGA软件设计

3.5.1 SPI通信功能

SPI通信功能的实现如图3所示。其中,控制器写时序模块实现与ARM处理器之间的写时序,并将写入的数据缓存至配置信息接收模块的RAM中;配置信息接收模块读取RAM区中的配置信息,并将配置信息发送至SPI发送时序模块和SPI接收时序模块;SPI发送时序模块将并行数据包转换为串行数据,并按“发送方式”、“时间间隔”、“发送次数”、“通信协议类型”等配置信息发送至通信设备;SPI接收时序模块按配置的通信协议接收通信设备的串行数据,并将其转换为并行数据后发送至接收数据处理模块;接收数据处理模块将接收到的数据缓存至内部RAM区,每包数据接收完成后,发送中断信号ram_int至ARM处理器;控制器读时序模块实现与ARM处理器之间的读时序,将接收数据处理模块的RAM中的数据回传至控制器。

图3 SPI通信功能实现框图

3.5.2 高速异步LVDS数据通信功能

高速异步LVDS数据通信功能的实现如图4所示。对于LVDS数据发送功能,由控制器接口处理模块、配置信息接收模块、数据生成模块、8b/10b编码模块和并串转换模块组成。其中,控制器接口处理模块实现与ARM处理器之间的写时序,并将写入的数据缓存至配置信息接收模块的RAM中;配置信息接收模块读取RAM区中的配置信息,并将配置信息发送到数据生成模块和并串转换模块;数据生成模块根据数据配置信息的内容产生符合业务协议的数据帧;8b/10b编码模块将数据生成模块送来的数据进行8b/10b转换,本模块调用标准IP核来实现8b/10b编码;并串转换模块依次将编码完成的10bit数据进行并串转换,然后生成LVDS差分信号输出。

对于异步LVDS数据接收功能,主要由数据恢复模块、8b/10b解码模块和USB3.0接收模块组成。其中,数据恢复模块将接收到的LVDS差分数据转换为单端,然后使用过采样的方法进行数据恢复,生成10 bit数据。使用与LVDS数据同频率的时钟经过DCM后产生4个相位的时钟,分别为clk0、clk90、clk180和clk270;分别使用上述4个时钟对LVDS数据进行采样,同时进行采样结果分析,以确定最佳的采样点,最终确定采样值;8b/10b解码模块接收数据恢复完成的10 bit数据并解码为8 bit数据,输出给USB3.0接收模块中,最终传输到PC机上保存成数据文件。

图4 高速异步LVDS数据收发功能实现图

4 系统测试结果及分析

按照本设计的原理与步骤,依次设计其他仿真测试前端,并利用本设计、测试监控终端、测试服务器、被测设备以及其他测试前端组建一套分布式半实物仿真测试系统,以此验证分布式前端间的时钟同步功能以及本设计前端功能的正确性。

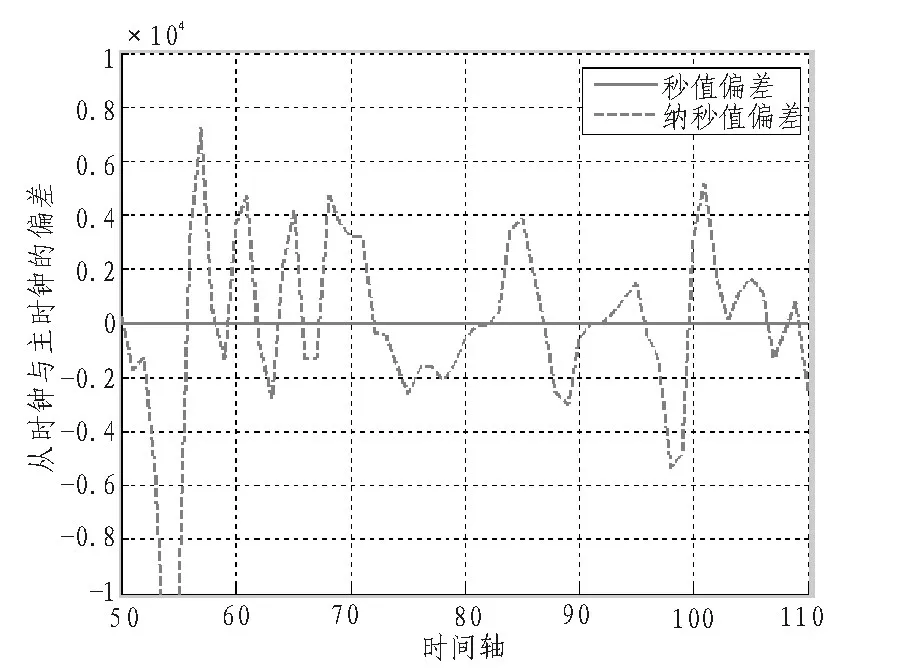

4.1 分布式前端间时钟同步的测试

利用上述构建的分布式半实物仿真测试系统,并选取其中一个前端作为主时钟,其他前端作为从时钟。PTPd的时钟伺服系统在同步过程开始后周期性计算本地从时钟与主时钟之间的时间差,并据此周期性的根据计算的时间差修正本地时钟。秒级的时间差在同步过程开始后迅速归零,纳秒级时间差在同步过程稳定后在正负10微秒之间动态波动。PTPd同步结果稳定后局部放大如图5所示。

图5 稳定后局部放大图

4.2 系统功能测试结果

为了验证本设计功能的正确性,利用Xilinx官方提供的FPGA开发工具ISE(集成软件环境)下的ChipScope工具对所设计的分布式半实物仿真测试系统前端部分进行功能的正确性验证。根据实际测试需求,对实现的SPI总线接口的收发功能以及LVDS高速下行数据的接收功能进行测试。测试结果如图6和7所示。

经过一系列的测试,本设计的测试前端能够遵循SPI总线协议,完成对目标软件的测试数据收发功能;同时也能够遵循LVDS的传输协议,完成对目标软件LVDS高速下行数据的采集和接收功能。本设计作为分布式半实物仿真测试系统的一部分,达到了设计初衷。

5 结束语

文中从航天嵌入式软件的特点以及在测试中遇到的实际问题出发,研发了这套分布式半实物仿真测试前端系统。经过一系列的测试以及工程实践的检验,本设计作为分布式半实物仿真测试系统的一部分,圆满完成了某型号航天器十余个配置项级嵌入式软件的评测工作,也为分布式半实物仿真技术在软件测试领域开辟了一条新道路。

图6 SPI总线接口功能时序图

图7 LVDS接口功能时序图

[1]王彬,张涛.基于ARM-Linux的1553B仿真测试前端系统[J].电子设计工程,2013(20):147-150.

[2]蒋元兵.基于分布式与半实物仿真技术的网络模拟系统设计与实现[D].成都:电子科技大学,2012.

[3]孙祥祥.分布式系统时钟同步协议的研究与实现[D].杭州:杭州电子科技大学,2013.

[4]苏宇,胡珩,张涛,等.基于PTPd的精准时钟同步技术研究的精准时钟同步技术研究[J].计算机技术与发展,2016(1):175-180.

[5]陈旿,孙建华,于振兴,等.基于IEEE1588的无线传感器网络时钟同步方法[J].系统工程与电子技术,2014(3):565-570.

[6]刘巍,熊浩清,石光,等.IEEE1588时钟同步系统应用分析与现场测试[J].电力自动化设备,2012(2):127-130.

[7]易胜蓝.嵌入式Linux下IEEE1588时间同步的实现[J].电讯技术,2012(5):800-803.

[8]宋升金,许永辉,姜守达.基于PTPd改进的高精密时钟同步实现[J].计算机工程与应用,2013,49(2):72-75.

[9]韩颖,牟龙华,周伟.IEEE1588协议在合并单元中的应用与实现[J].电力系统及其自动化学报,2012(3):16-21.

[10]王威.半实物仿真测试系统中软件可靠性测试[D].成都:电子科技大学,2014.

[11]张金山.基于OPC与半实物仿真技术的DCS测试系统的设计与应用[D].天津:天津理工大学,2013.

[12]YANG Jie,WANG Bo-yu ,HUANG Yu,et al.Design of Distributed Real-Time Simulation and Test System Based onVMIC Network and xPC[C]//Proceedings of the 32rd Chinese Control Conference,2014(7):26-28.

[13]陈进朝,杜承烈,黄俊江.Xenomai平台下基于以太网的实时通信方案[J].计算机工程,2014(10):86-91.

[14]苏宇,张涛,孙黎.基于Xenomai的实时Linux系统的研究[J].计算机技术与发展,2013(10):1-5.

[15]黄芳.基于S3C2440和RTAI的实时平台的设计与实现[J].组合机床与自动化加工技术,2014(2):83-86.

[16]张晓龙,郭瑞锋,陶耀东,等.Linux实时抢占补丁研究及实时性能测试[J].计算机工程,2014(10):304-307.