基于CSMC 0.5微米CMOS工艺加固版图设计及实现

李湘君

基于CSMC 0.5微米CMOS工艺加固版图设计及实现

李湘君

(中国电子科技集团公司第四十七研究所,沈阳110032)

随着CMOS电路技术的高速发展,集成密度增大,低功耗设计以及系统芯片也已普及,导致电路更容易受到空间干扰的影响,从而使整个电子系统发生故障,因此有必要对电子元器件的抗总剂量、抗闩锁等能力进行加固设计。采用华晶上华半导体有限公司的0.5微米的CMOS工艺,设计可编程计数器加固版图时,对NMOS管采用环形栅结构,消除辐射感生边缘寄生晶体管漏电效应,降低总剂量效应的影响;采用双环保护结构,降低CMOS集成电路对单粒子闩锁效应的敏感性。对流片后的芯片进行试验,试验表明,版图加固设计的可编程计数器具有一定的抗单粒子闩锁和总剂量能力。

可编程计数器;单粒子闩锁;总剂量;双环保护;加固设计;版图设计

1 引 言

随着空间技术的发展,各种电子元器件被应用在空间系统及辐照环境时,会受到总剂量效应(TID:Total Ionizing Dose)和单粒子效应(SEE:Single Event Effect)的影响,其主要表现为:电路逻辑功能发生错误、器件阈值电压漂移、电路静态和动态电流增加等,对元器件造成不同程度的破坏,从而使整个电子系统发生故障[1]。采用普通的半导体材料和电路设计方法已经不能满足一些特殊领域的需求,因此有必要对电子元器件进行抗总剂量、抗闩锁能力等方面的加固设计。

2 总剂量和单粒子闩锁效应

2.1 总剂量效应

总剂量效应通过电子和空穴对的累积效应而对半导体器件产生影响。通过电离辐射半导体中的栅氧层和场氧层会产生大量的电子空穴对,在电场的作用下,由于电子运动较快,这样会使氧化层中产生大量的空穴积累,这些正电荷有一部分将会被氧化层中的缺陷俘获,从而会使半导体电路因为寄生晶体管而发生不希望存在的导通或者阈值电压等异常现象,使器件发生逻辑错误。集成电路元器件长期处于辐射环境中时,多次粒子入射将会造成正电电荷积累,从而引起器件性能发生退化以至失效。辐射粒子穿进物质,与物质中的电子相互作用,把自身的能量传给电子,如果电子由此获得的能量大于它的结合能,电子就会脱离原子核对它的束缚成为自由电子,而原子则变成了带电离子,这一过程称为电离辐射效应。中子流、高能电子、γ 射线和X射线等均可引起电离效应,γ 射线和X射线等光子流更容易引起材料电离,γ射线的电离效应最为显著[2-3]。

2.2 单粒子闩锁效应

单粒子闩锁效应(SEL,Single Event Latch-up)是指由于单粒子入射使半导体中衬底电压分布产生变化,从而使半导体器件内部的一些寄生的NPN、PNP、电阻与NMOS、PMOS产生一个电流增益大于1的正反馈回路,不断放大VDD与GND之间的泄漏电流,直到由于电流过大使器件发生烧毁等严重后果[4]。

由于CMOS结构中固有的寄生PNPN四层可控硅结构,所以其闩锁效应不可避免。单粒子的轰击可以使得PNPN结构导通,除了触发机理不同,在辐射环境下的单粒子闩锁效应和一般的闩锁效应在其他机理上都相同[5]。所以一切抗闩锁效应的措施都可以用于抗单粒子闩锁效应。

3 可编程计数器抗总剂量和闩锁版图设计

3.1 可编程计数器

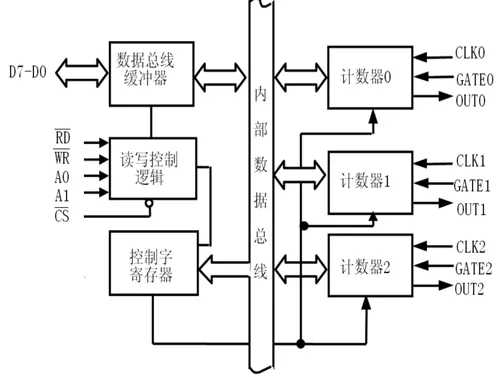

可编程计数器是一款微机接口电路,具有3个独立的16位的通用定时/计数器,每一个定时/计数器的工作方式及计数常数分别由软件编程选择,共有六种工作方式,可进行2进制或10进制计数或定时操作。

其内部的3个独立的16位的通用定时/计数器,每一个各有三根I/O线:CLK为时钟输入线,作为计数脉冲输入端;OUT为计数器输出端,当计数器减为零时,OUT输出相应的信号;GATE为门控信号,用于启动或禁止计数器的操作。控制字寄存器用来寄存操作方式控制字,每一个计数器都有一个单独的控制字寄存器,只能写入不能读出。D0~D7为双向、三态数据总线,是单片机与本电路之间的数据传输线,RD、WR为数据读、写控制线,A0、A1是地址选择线,CS是片选线[6]。其功能框图如图1所示。

图1 功能框图

可编程计数器的主要结构就是计数器,而每一个计数器都有一个单独的控制字寄存器,控制字寄存器用来寄存操作方式控制字,只能写入不能读出。针对控制寄存器中的CMOS门电路单元进行了版图加固设计,增强了可编程计数器的抗总剂量和闩锁能力。

3.2 可编程计数器门电路单元的抗总剂量和闩锁版图设计

以控制寄存器中的CMOS门电路单元中的一个与非门为例,介绍加固版图设计方法。在研制中,采用了NMOS管环形栅结构替代传统的双边结构,消除了辐射感生边缘寄生晶体管漏电效应;采用了双环保护结构,降低了CMOS集成电路对单粒子闩锁效应的敏感性。设计好的版图如图2所示。

图2 与非门电路版图

CMOS器件的失效主要是由于在氧化层中产生辐射感生电荷和在Si/SiO2界面产生辐射感生界面态,从而导致器件阈值电压漂移,沟道载流子迁移率降低,漏电流增加。电离辐射在SiO2中激发电子-空穴对,电子可以很快移出SiO2,而空穴则一部分移出SiO2,一部分会被SiO2中的空穴陷阱俘获成为正的固定空间电荷。在正偏压下,空间电荷比较多地集中在Si/SiO2界面附近,形成正空间电荷,使阈值电压向负电压方向漂移。对NMOS管在最坏偏压的情况下,晶体管导通,空穴在电场作用下向Si/SiO2界面运动,极易被界面附近的陷阱俘获;而对PMOS管最坏偏压情况下,晶体管截止,没有电场使空穴向Si/SiO2界面运动,被界面附近的陷阱俘获的几率要小很多[7],因此PMOS管具有比NMOS管强的多的抗总剂量电离辐射能力,加固设计也主要针对CMOS电路中的NMOS管进行。

在晶体管的设计中,多晶硅栅在场氧和栅氧的过渡区会产生一个寄生晶体管,这个寄生晶体管对总剂量的电离辐射极为敏感。在商用工艺线中,由于寄生晶体管不可能导通,商用工艺没有考虑这种情况。

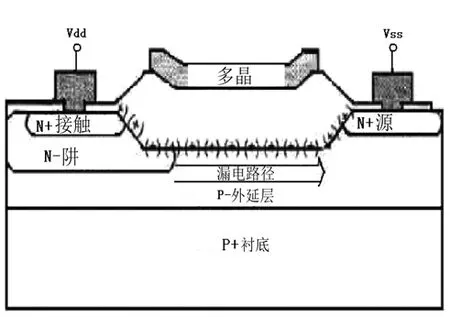

在加固版图设计时,需要把NMOS管改为环型栅,在源漏之间完全消除了薄氧到厚氧的过渡区。环形栅结构如图3所示,完全消除了辐射感生边缘寄生晶体管漏电效应,并且和商业工艺兼容。由此,器件的抗总剂量水平得以增强。

对NMOS管采用P+有源区环,能起到对场氧反型漏电沟道的截止作用。场氧本来是为相邻晶体管起绝缘作用的,但是当多晶硅连线在场氧上方通过时,就有可能形成场氧反型的漏电结构。场氧反型一般表现为芯片漏电流大大增加,总剂量辐射下,如果产生非常大的静态电源电流,就可以认为发生了场氧反型。在漏电流沟道上插入一条重掺杂的P+保护环能够有效的减轻总剂量电离辐射感生的场氧漏电效应。因为大多数工艺并不提供附加的场氧下方P+掺杂,因此必须增加一条有源区使得P+环在源漏注入时形成。这种方法大大增加了N+源漏区到阱的间距,阻断了漏电沟道的产生,如图3所示。

图3 利用P+有源环形成场氧反型

对PMOS和NMOS采用双环保护结构,版图结构如图2所示,双环保护减轻了单粒子闩锁效应的影响,P+保护环还可以起另外一个重要的作用,就是可以有效降低闩锁效应的影响,降低寄生横向NPN管增益。为了确保不发生单粒子闩锁效应,在N阱里的P管周围加一个N+保护环,降低寄生PNP管增益。

3.3 总体版图设计

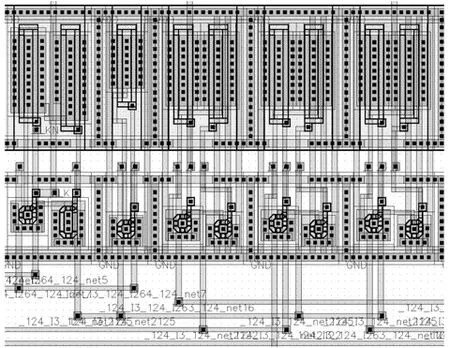

采用华晶上华半导体有限公司的0.5微米CMOS工艺,针对每一个门电路都利用如图2所示的加固方法对版图进行了加固设计,基本单元以电源和地线为边界分别对齐,在布局布线过程中形成电源网和地线网;基本单元在竖直方向预留足够的布线通道,供二次铝走线。尽量采用一次铝在单元内部连线,二次铝作为单元间走线。

整个版图的其中一部分如图4所示。

总体采用的自动布局布线方式,使用布线软件LEDIT进行版图布局布线,生成的电路内核版图,外围PAD单元采用全定制设计,手动布局[8]。同时版图设计时采取电源(VDD)和地线(VSS)的电流限制设计。金属传导电流时,电流密度有一定的极限值。如果电流大大超过导体的阈值Jth会产生电迁移现象,即金属原子会随电流迁移,金属线将越来越细,最终导致断裂。特别是用作VDD和VSS的线条。因为汇总处电流最大,所以在设计时适当加宽了电源线和地线的宽度,有效地防止了电迁移。

图4 部分版图

由于电路标准单元设计采用了环栅结构,与正常结构的MOS管模型参数会有差别,所以会对电路后仿真带来影响。为了减小这种影响,在电路设计过程中,标准单元设计尽量做到种类最少,使最终版图的后仿真结果可以贴近电路实际参数性能。

4 试验结果

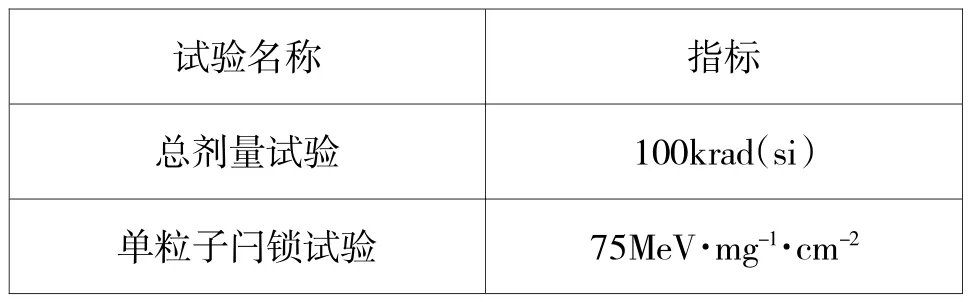

对流片后的芯片进行了总剂量和单粒子试验后,试验条件如表1所示:

表1 试验条件

总剂量试验进行“移位测试”,再进行168h加速退火并按规定进行终点电测试,测试结果符合参数指标要求。单粒子试验过程中,无电流锁定现象。试验表明,可编程计数器具有一定的抗总剂量和单粒子闩锁能力。

5 结束语

采用华晶上华半导体有限公司的0.5微米CMOS工艺,以可编程计数器的主要结构为例,介绍了版图的加固设计方法,实现了具有抗总剂量和单粒子闩锁能力的可编程计数器。且版图设计采用自建版图库进行自动布局布线,缩短了设计周期,使用标准的商业CMOS工艺进行生产,不依赖专门的加固工艺线,容易移植,保证生产延续性。

[1]范雪.一种新型反熔丝存储器的研制及其抗辐射加固方法研究[D].成都:电子科技大学,2011.Fan Xun.To Develop a New Type of the Fuse Storage and Reinforcement Methods Against Radiation[D].Chengdu:University of Electronic Scienceand Technology,2011.

[2]王刚.新型反熔丝器件及抗总剂量辐射PROM的研究与实现[D].成都:电子科技大学,2013.Wang Gang.New the Fuse Devices and Total Ionizing Dose Radiation Resistance Research and Implementation of Prom[D].Chengdu:University of Electronic Science and Technology,2013.

[3]APaccagnella.“Single Event Effects:Introductinn”[EB/OL](2013.02.05)http://sirad.pd.infn.it/scuola_legnaro_2007/Presentazioni_pdf/12_Paccagnella_ParteA.pdf

[4]Fstruresson.”Single Event Effects(SEE)Mechanismand Effects”[EB/OL](2014.11.02)http://space.epfl.ch/webdav/site/space/shared/industry_media/07%20SEE%20Effect%20F.sturesson.pdf

[5] 何伟.铁电存储器的辐射效应研究与加固设计[D].成都:电子科技大学,2014.He Wei.Radiation Effect of ferroelectric Memory Research and strengthening Design[D].Chengdu:University of Electronic Scienceand Technology,2014.

[6] 戴梅萼,史嘉权.微型计算机技术及应用:从16位到32位[M].北京:清华大学出版社,1996.2.Dai Meie,Shi Jiaquan.Micro Computer Technology and Application:From16 to32 Bits[M].Beijing:Tsinghua University Press,1996.2.

[7] 褚忠强,徐曦.现代工艺集成电路的总剂量效应及加固技术[J].现代电子技术,2010.2(313):171-174.Chu Zhongqiang,Xu Xi.Modern Technology of Integrated Circuit of Total Ionizing Dose effect and Reinforcement Technology[J].The Modern Eletronic Technology,2010.2(313):171-174.

[8] 陈春章,艾霞,王国雄.数字集成电路物理设计[M].北京:科学出版社.2008:21-23.Chen Chunzhang,Ai Xia,Wang Guoxiong.Digital Integrated Circuit Physical Design [M].Beijing:Science Press.2008:21-23.

Design and Implementation of Strengthening Layout Based on CSMC 0.5滋m CMOS Process

With the high-speed development of CMOS circuits technology,integration density increases,and the low-power design and system chip is popularized,which causes the circuits more vulnerable to the affection from space interference so as to lead the whole electronic system to malfunction,thereby it is necessary to carry out the strengthening design to the capacity of resistanting total ionizing dose and latch-up.Using 0.5μm CMOS process from CSMC-HJ,when designing strengthening layouts of programmable counters,gate-all-around structure is deployed to NMOS to eliminate the edge parasitic transistor leakage effect induced by radiation,and to depress the influence of total ionizing dose effect;double-ring guard structure is used to reduce the sensitivity of CMOS integrated circuit to single event latch-up effect.Experiment is applied to the chips after fabrication,and it shows that the programmable counters with layout strengthening design have certain capacity of resistanting single event latch-up and latch-uptotal ionizing dose.

Programmable counter;Single event latch-up;Total ionizing dose;Double-ring guard;Strengthening design;Layout design

10.3969/j.issn.1002-2279.2017.06.019

TN4

A

1002-2279-(2017)06-0082-04

李湘君(1984—),女,辽宁省沈阳市人,工程师,主研方向:集成电路设计。

2016-11-07