基于Catapult C工具递归型滤波器设计和算法优化

叶海雄,陶宁蓉,王世明

(上海海洋大学工程学院,上海201306)

基于Catapult C工具递归型滤波器设计和算法优化

叶海雄,陶宁蓉,王世明

(上海海洋大学工程学院,上海201306)

使用高层次综合方法设计超大规模集成电路是一项前瞻性的工作。其设计理念旨在保证电路性能的前提下,缩短电路开发周期,让产品更早投入到市场。然而针对高层次综合工具面对算法转换时编译能力存在局限的问题,本文以信号处理中递归型滤波器为例,针对滤波器功耗的问题,通过分析滤波算法转换以及评估高层次综合工具对滤波器的影响。实验结果表明,采用算法转换及优化的方法,能使电路面积减少58%,能耗降低25%,达到低碳化、节能环保的电路设计要求。

高层次综合;集成电路;信号处理;递归型滤波器;面积;能耗

在视频流、多媒体、图像处理、模式识别等领域设计超大规模集成电路是一项具有挑战性的工作。传统的设计方式通过使用硬件描述语言VHDL[1-2]或Verilog[3]完成数字系统的设计,其仿真时间长和程序缺乏灵活性,无法解决产品设计时间和产品性能、面积和能耗方面的矛盾。目前高层次综合[4]工具解决方案能够减少中间步骤,自动实现从高级描述抽象层面到行为级物理层面的转换。在此领域的研究相当活跃[5-7]。文献[8]描述了MMAlpha高层次综合工具使用多面体模型分析并转换循环体的能力。文献[9]描述了高层次综合工具Gaut从C语言通过编译器自动转换成硬件描述语言VHDL。文献[10-13]描述输入语言为C或C++语言的Catapult C高层次综合工具编译器自动完成接口、元器件库选择、时序安排等工作,生成RTL级VHDL或Verilog语言。其主要的优势在于,

1)电路设计速度快,迅速产生产品原型,估算电路的面积、功耗和性能。在算法中使用C或者C++语言较便捷,相比传统的手工RTL代码,IP的开发时间缩短2~3倍。同时IP可以被重用。

2)协同仿真时间短。相比RTL级的仿真,设计者能够对所设计IP进行协同仿真,即用C或C++语言对IP的抽象描述级进行测试,同时部分高层次综合工具可以识别C++语言并自动生成system C语言对输出的行为级测试,并比较两者的结果。

3)IP仿真/验证时间短。相比RTL的仿真时间,C语言的仿真速度要快10倍。利用这个特点,设计者也能够验证IP功能的准确性。

在Catapult C工具中,可以通过调整间距启动ii值的参数方式直接影响电路面积大小和速度快慢。其优势在于快速设计迅速评估电路特性;在抽象级层面和行为级层面协同仿真,保证设计功能的准确性;重用代码减少设计者重复书写代码时间。

1 递归型滤波算法及优化方法

递归型IIR滤波器[14-20]在信号处理、多媒体技术、模式识别、人工智能等方面已得到广泛应用。输入信号为x(n-k)、y(n-k)与冲击响应为ak、bk,其差分方程如下:

其系统函数为:

IIR滤波器从硬件和软件方面实现及优化较困难,其原因在于数据关联程度高,滤波器当前输出结果不仅取决于输入数据x(n-k),而且与前几次的输出结果y(n-k)相关。文本采用IIR11滤波器,其计算延时小、稳定性高、实时性强等特点非常符合数字图像的应用。IIR11的第一个1表示一个输入数据x(n),第二个1表示前一次输出数据y(n-1)。

该滤波器用于图像中平滑处理,平滑参数为α,取值范围0~1之间。当α的值为0.5时,表示图像的噪音很多;当α的值为0.8时,表示图像的噪音少;当α的值为1时,表示图像的噪音较少。在计算中,本文假设输入、输出为8位,中间计算结果为16位。从硬件角度看,上面操作完全能够用ASIC或FPGA中的VHDL语言实现。Catapult C高层次综合工具有ac_int和ac_fixed类型以实现数据长度操作。同时本文的 IIR11滤波器根据文献[21]提出的ɤ=e-α,用 2的次方形式,长度为 3位表示ɤ,即ɤ=2-1ɤ1+2-2ɤ2+2-3ɤ3。其优势是让移位操作代替乘法操作,简化后得到:

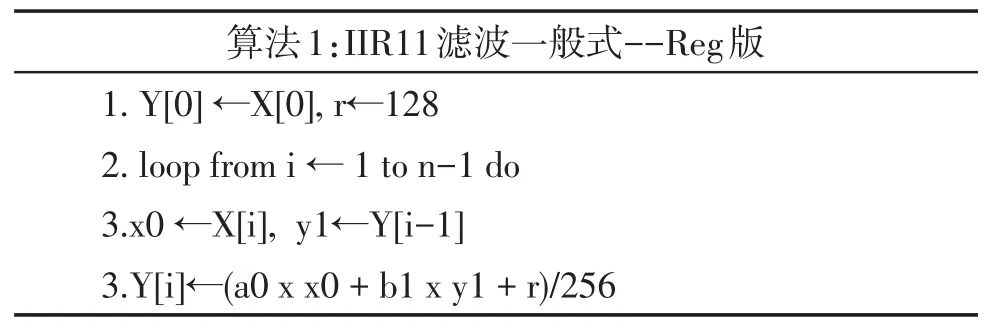

从算法的角度得到IIR11滤波器3种形式:一般式、系数式和延迟式。一般式是由2个乘法与1个加法运算组成,如式(4)。表1中需要加入纠正项r以弥补进位导致的精度损失。计算结果右移8位以保证输出结果长度为8位,用Q8表示。本文采用的滤波器计数都从i=1开始,输出信号值复制输入信号的值。读取与写入数据分别在两个不同的内存中以避免同时访问内存地址引起冲突。

表1 IIR11滤波算法一般式Reg版

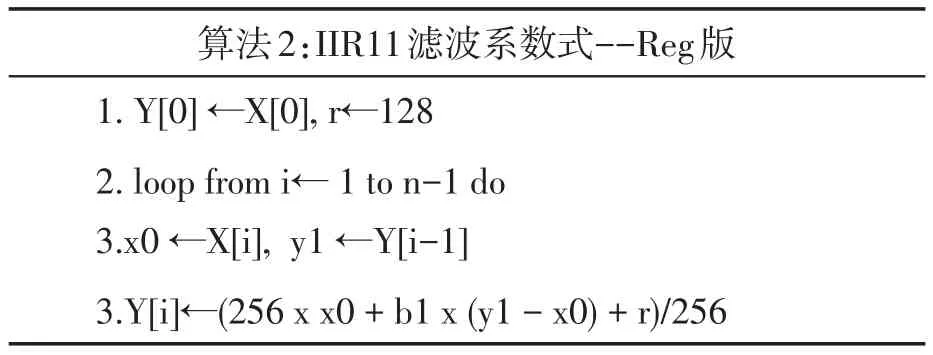

Rot版与Reg版相比,增加了移位寄存器以保存数据用于下次计算。将式(4)中的平滑系数ɤ展开,得到式(5)。式(5)乘法的个数由2个降低到1个,加法的个数为2个和1个移位操作。即在Q8定点式中需要x0乘以28,或者左移8位,如表2所示。

表2 IIR11滤波算法系数式—Reg版

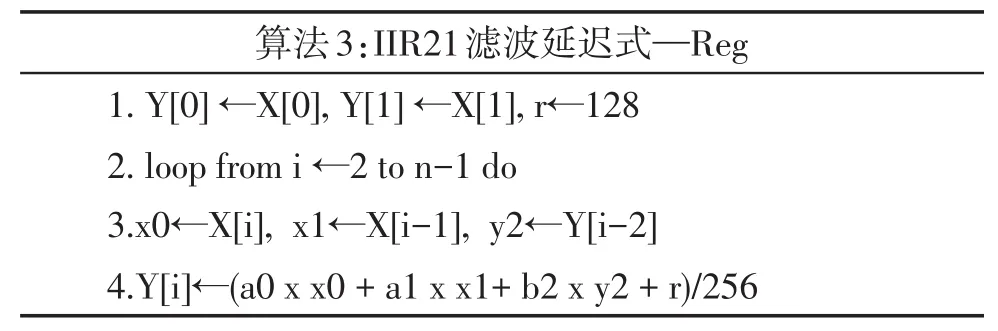

为了避免y(n)和y(n-1)相关联,本文采用y(n-2)项代替y(n-1)并代入到式(4)中,得到延迟式(6)。其计算的输出结果不仅取决于x(n)和x(n-1),还与y(n-2)有关,如表3所示。

表3 IIR21滤波算法延迟式—Reg

2 级联滤波算法及优化方法

2.1 级联递归型IIR滤波

为了进一步去除噪声,本文采用级联两个非递归型滤波器。其连接方式有3种情况:

1)在两个滤波器中间需要一个内存保存第一个滤波器所有的计算结果并用于第二个滤波的计算。本文采用内存的面积2倍大于滤波器本身,取消中间内存有利于节约硬件面积的开销。

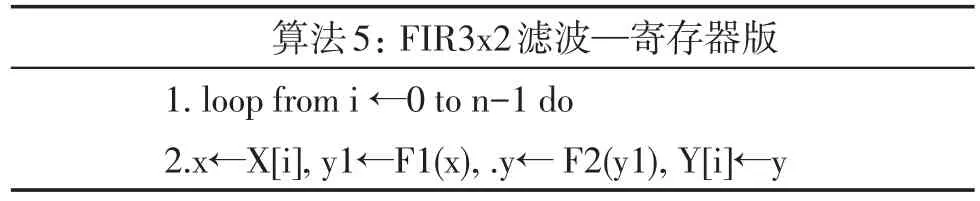

2)两个滤波器中间只需加入一个寄存器,算法如表4所示。

3)一个新的滤波器等效替代两个级联滤波器,算法如表5所示。

表4 2xIIR11滤波器+寄存器版

表5 IIR12滤波器等效替代版

同样的,对于IIR12滤波器的系统函数为:

从编译的角度,编译器能够合并多个循环体,即合并一个滤波器可以看成合并一个操作。合并的关键是为了节约中间内存的使用。根据离散卷积,两个1阶的IIR11滤波器串联,可以用1个2阶的IIR12滤波器以等效替代。

2.2 级联递归型IIR滤波算法

同样,IIR12滤波器也有一般式、系数式和延迟式3种形式。一般式是由3个乘法与2个加法运算组成,如式(8)。

一般式如下:

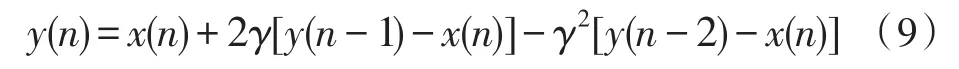

将式(8)中的平滑系数ɤ展开,得到式(9)。式(9)乘法的个数由3个降低到2个,加法的个数为4个和1个移位操作。

系数式如下:

本文采用y(n-2)和y(n-3)两项代替y(n-1)并代入到式(8)中,得到延迟式(10)。其计算的输出结果不仅取决于x(n)和x(n-1),还与y(n-2)和y(n-3)有关。

延迟式如下:

2.3 IIR12滤波器的稳定性

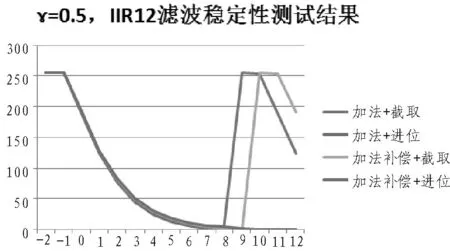

IIR12滤波器稳定性取决于滤波器的系数的大小。图1展示了4种算术表达式:加法+截取、加法+进位、加法带修正+截取和加法带修正+进位。当i<0时,x(i)=y(i)=255。当i>=0时,x(i)=0。当ɤ=0.5时,经过10次迭代后,加法+进位和加法补偿+进位的操作结果y(n)趋向于0,表示上述两个操作稳定性高;相反,加法+截取和加法补偿+进位操作,y(n)在0到255数值之间震荡,表明不稳定。其原因是IIR12滤波器的系数a2是负数导致截取操作的计算结果小于0,即越界,二进制补码给予一个正数的结果。

通过多次修改最后一个系数或者同时修改3个系数可以修正系数的总和避免浮点型系数通过截取操作转换成定点型系数可产生系数总和的错误。

图1 滤波算法4种算术表达式稳定性测试

3 实验结果与分析

本实验环境在Intel多核CPU 3.2 GHz、Solaris Sun平台上,使用ST公司的CMOS 65纳米工艺库和Design Compile工具测试不同形式IIR滤波器的优化转换方法,得到电路面积、功耗、工作频率和吞吐量等数据结果。通过计算总时间与总功耗的乘积再除以总像素点,得到单位像素点的能耗,用cpp表示。

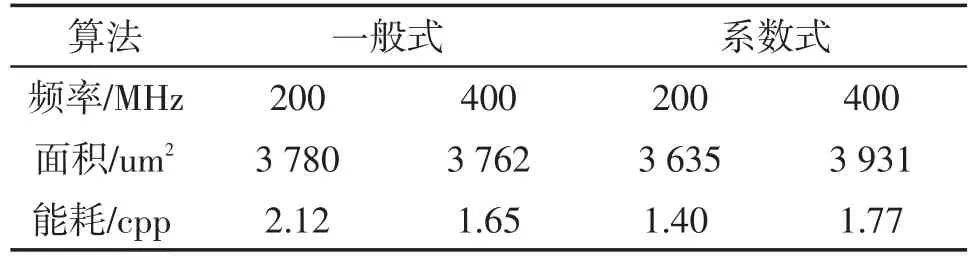

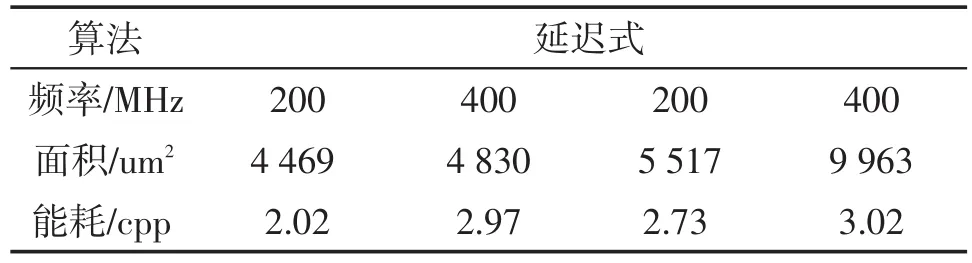

表6、7反映了3种形式算法在一定频率下,最优的面积和最佳功耗。相同频率下,延迟式的面积和能耗比一般式和系数式高20%。但是一般式和系数式最高工作频率达到400兆赫,而延迟式最高工作频率达到800兆赫。说明采用延迟式的速度比其他的形式要快2倍。从另一个方面看,采用65纳米工艺技术,延迟式的工作频率最高。

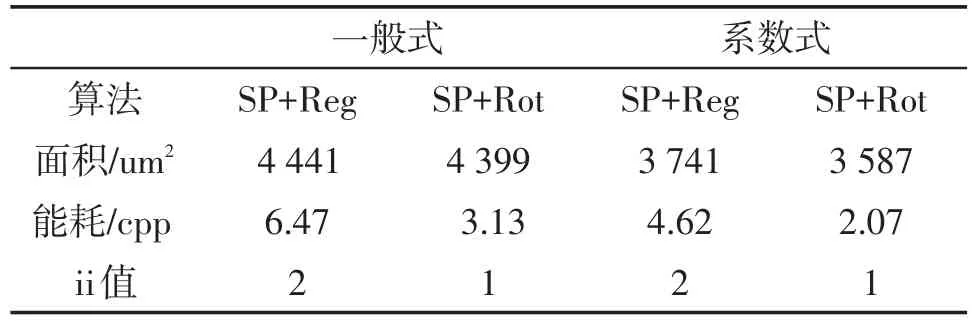

表8描述了单个IIR滤波器一般式和系数式不同版本算法的最佳面积和最优能耗。相比一般式SP+Reg版本,系数式中SP+Rot版本的面积和能耗是最低的,在面积和能耗方面节约了20%和58%,其间距启动值为1。

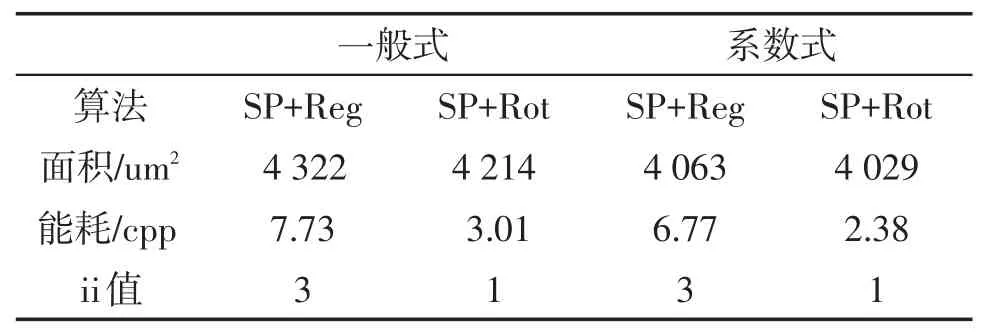

从表9、10看,在两个滤波器级联中面积和能耗方面表现最佳的版本同样为系数式的SP+Rot。2xIIR11寄存器版中,相比一般式SP+Reg版本,系数式中SP+Rot版本的面积和能耗方面节约了1.24倍和3倍;而2xIIR11寄存器版的SP+Rot在面积和能耗方面比IIR12等效替代版SP+Rot分别降低12%和14%。

从表8、9和10看,2xIIR11寄存器版的SP+Rot在面积和能耗方面比双倍的IIR11滤波的SP+Rot版减少了58%和25%。

当两个滤波器级联时,寄存器版算法不足在于重新修改代码,造成设计者额外的时间开销。而IIR12等效替代版只需要事先计算滤波器的系数就可以直接替代,方便简单。在实际工作中,设计者可以选择使用合适的方式进行电路设计。

表6 IIR12滤波一般式和系数式算法的最佳面积与最优能耗

表7 IIR12滤波延迟式算法的最佳面积与最优能耗

表8 IIR11滤波算法的最佳面积与最优能耗

表9 2xIIR11滤波算法的面积与能耗

表10 IIR12滤波算法的面积与能耗

4 结束语

本文采用Catapult C高层次综合工具,通过对递归型IIR滤波器算法的优化,分析和评估了算法转换对电路设计中面积和能耗的影响。其结果在科学方面,电路的面积减少58%,能耗降低25%,达到绿色环保目标;在经济方面,设计开发电路时间缩短2倍以上,使产品更早投入市场。下一步工作将对算法在专用微处理器STxP70和通用微处理器Neon上的能耗与面积进一步研究,以评估不同工具对IIR递归型滤波性能、面积和能耗的影响。

[1]胡宏梅.基于VHDL语言的数字钟层次化设计与实现[J].电气自动化,2016,38(1):113-115.

[2]Suresh S.Vhdl implementation of manchester encoder and decoder[J].International Journal of Electrical Electronicsamp;Data Communication,2015,293(6):96-97.

[3]董青,朱洪翔,祁晓鹏.基于FPGA视频合成系统设计与实现[J].计算机测量与控制,2016,24(4):247-249.

[4]樊宗智,周煦林,刘彬.基于高层次综合的JPEG编码器设计[J].微电子学与计算机,2015(6):32-35.

[5]Bandyopadhyay S,Sarkar D,Mandal C.Validating SPARK:high level synthesis compiler[C]//ISVLSI.2015:195-198.

[6]Nane R,Sima V M,Pilato C,et al.A survey and evaluation of FPGA high-level synthesis tools[J].IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2015:1-1.

[7]Gal B L,Casseau E.Latency-sensitive high-level synthesis for multiple word-length DSP design[J].Eurasip Journal on Advances in Signal Processing,2011,2011(1):1-11.

[8]George N,Novo D,Rompf T,et al.Making domain-specific hardware synthesis tools costefficient[M].2013.

[9]Coussy P,Heller D,Chavet C.High-Level Synthesis:On the path to ESL design[C]//IEEE International Conference on Asic.IEEE,2011:1098-1101.

[10]Damak T,Ayadi L A,Masmoudi N,et al.HLS and manual design methodology for H.264/AVC deblocking filter[C]//World Congress on Information Technology and Computer Applications Congress.2015.

[11]李杨.基于CatapultC Synthesis的图像校正算法设计[J].电子测量技术,2016,39(7):92-95.

[12]谢正,张开锋.基于Catapult C的DCT算法设计[J].信息化研究,2011,37(4):42-45.

[13]秦贵军.基于Catapult C的汽车轮胎力估计的FPGA实现[D].长春:吉林大学,2013.

[14]耶晓东.基于Matlab的IIR数字滤波器设计及DSP实现[J].电子设计工程,2011,19(9):175-177.

[15]毛军勇,陈立家,刘名果.基于结构进化的无限冲激响应数字滤波器设计方法[J].计算机应用,2015,35(5):1250-1254.

[16]郭亚琴,秦燕.IIR数字滤波器设计与实现[J].软件导刊,2015(4):84-86.

[17]赵海军,李敏,李明东,等.一种基于快速阵列算法实现的IIR数字滤波器[J].云南大学学报:自然科学版,2016,38(2):219-224.

[18]王红琳,常翠宁,李志南,等.改进教与学优化算法的IIR数字滤波器设计[J].计算机仿真,2015,32(11):259-263.

[19]毛军勇,陈立家,刘名果.基于结构进化的无限冲激响应数字滤波器设计方法[J].计算机应用,2015,35(5):1250-1254.

[20]刘鑫,王胜奎,李广良,等.基于FPGA的IIR数字滤波器实现及其量化字长效应分析[J].电子设计工程,2014(15):23-26.

[21]Demigny D,Lorca F G,Kessal L.From the architectural design to the algorithm.An example:The Deriche edge detector[J].TraitementDu Signal,1997,85(6):496-509.

Research on Catapult C tool and optimization algorithm of recursive filter

YE Hai⁃xiong,TAO Ning⁃rong,WANG Shi⁃ming

(School of Engineering Science and Technology,Shanghai Ocean University,Shanghai201306,China)

Using High-Level Synthesis(HLS)method to design Very Large Scale Integrated(VLSI)circuit is an advanced work.The design philosophy is to shorten the developing time and accelerate the time to market under guarantying the performance.However the problem limited the compiler of High-Level synthesis tool to algorithm transformation optimization,this paper based on the Infinite Impulse Response(IIR)recursive filter in signal processing as an example,we analyzed and evaluated the impacts on the algorithm optimization transformation to the HLS tool Catapult C.The experimental results showed the circuit 58%on area and 25%on energy consumption,meeting the requirements of low carbon and ecologic energy.

high level synthesis;very large scale integrated circuit;signal processing;recursive filter;area;energy consumption

TN4

A

1674-6236(2017)22-0010-05

2016-12-05稿件编号:201612023

国家自然科学基金项目(71501125);上海市青年教师高校新进教师培训及科研启动基金(ZZHY14033)

叶海雄(1982—),男,浙江象山人,博士,讲师。研究方向:信号图像处理、嵌入式系统、集成电路设计。