基于FPGA的开放式CPU实验模型设计

康磊++杨朝辉

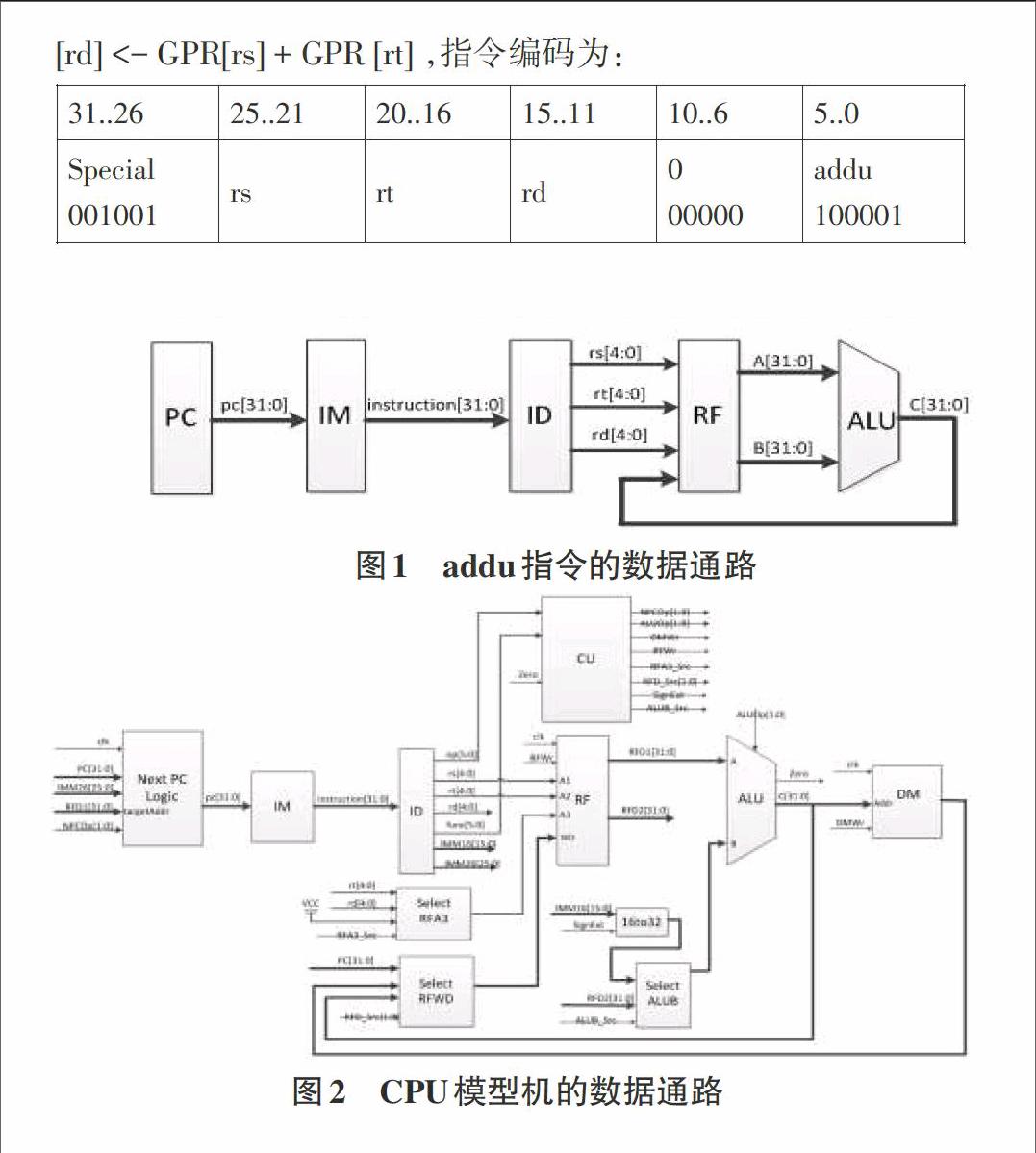

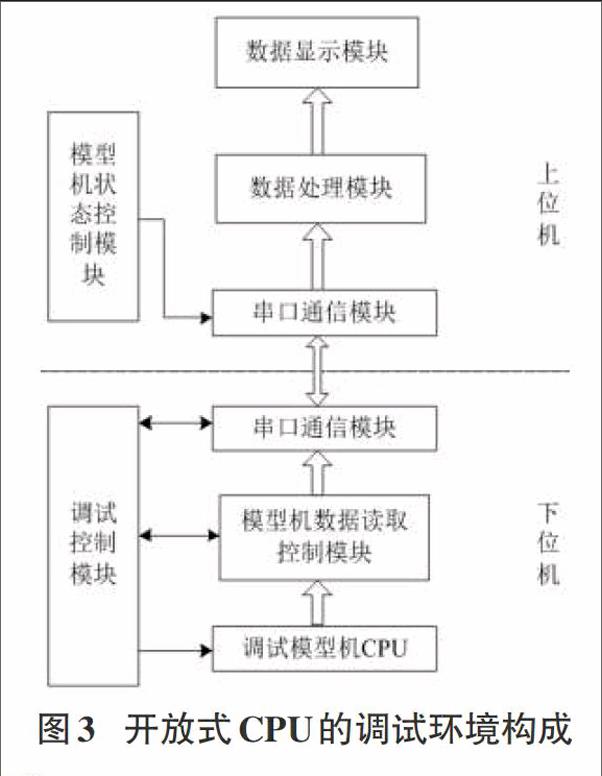

摘要:在计算机组成原理的教学中,CPU设计实验能够使学生深入理解和掌握计算机的运行和控制机制。该文提出了一种基于FPGA的CPU开放式实验平台的设计思想,该平台由上位机和硬件开发平台组成。通过开放式实验平台,学生可以根据自行选取的MIPS指令集修改模型机的数据通路和控制通路并设计控制器,通过实验平台观察运行过程和结果以确定设计的正确性。

关键词:CPU实验模型;数据通路;控制通路;MIPS指令集;FPGA

中国分类号:TP302 文献标识码:A 文章编号:1009-3044(2017)30-0235-03

Design of Open CPU Experiment Model Based on FPGA

KANG Lei,YANG Zhao-hui

(School of Computer, Xi'an University of Petroleum, Xi'an 710065, China)

Abstract: CPU design experiment in the teaching of computer composing principle can make student understand and master the mechanism of computer operation and control deeply. This paper presents a design idea of an open CPU experiment platform Based on FPGA, which is composed of the host computer and the hardware development platform. Through the open experiment platform, the students can modify the data path and control path of the model machine and design the control unit according to their own MIPS instruction set, and observe the running process and the result to ensure the correctness of the design through the experimental platform.

Key words: CPU experimental model; Datapath; Controlpath; The MIPS instruction set; FPGA

由于中央處理器(CPU Central Processing Unit)在现代计算机系统中占有核心功能,对于计算机专业的课程体系,CPU的设计开发是一个重点和难点。完成CPU的设计需要学生学习计算机的组成原理,系统结构等,并以此设计出CPU系统。而在计算机组成原理的CPU设计试验中,目前国内高校普遍使用的是教学系统或者小规模集成电路和手工布线方式,这样只能进行验证性实验,或者实验的规模有限,过于琐碎的操作耗费设计人员的精力,无法提供自住设计和发挥的平台。

本文通过研究和设计基于FPGA的32位开放式CPU试验模型,同时设计开发出相关的验证调试系统,为设计人员提供了一套开放式,可自主设计的CPU设计实验环境。设计人员通过该开放式CPU模型能直观感受CPU的工作原理和各部件的功能,根据自己的设计更新该实验模型的相关部件,并设计自己的数据通路和控制通路来实现自己的设计。通过调试系统设计人员可以监控CPU内部运行情况,对设计的CPU进行运行调试验证,完成CPU的设计和实现验证。

1 CPU功能和结构设计

1.1. CPU的指令系统

指令系统作为CPU的对上接口,定义了CPU的功能,并直接影响了CPU的实现。MIPS作为精简指令集(RISC Reduced Instruction Set Computer)的代表,有着指令定长,结构简单的特点。选择MIPS指令集可以减少指令设计难度。本文的指令基于MIPS指令集进行设计,存储系统采用哈佛结构。

MIPS指令分为立即数类型(I类型),跳转类型(J类型),和寄存器类型(R类型)三种。本文设计的模型机选取了如表1所示的10条指令。这10条指令分别属于算术逻辑运算类,访存类和跳转类,可以满足程序设计的基本要求。

表1 选取的10条指令

[类别\&指令助记符\&描述\&运算类\&addu rd, rs, rt\&GPR[rd]<-GPR[rs]+ GPR[rt]\&subu rd, rs, rt\&GPR[rd]<-GPR[rs]- GPR[rt]\&and rd, rs, rt\&GPR[rd]<-GPR[rs] AND GPR[rt]\&ori rt, rs, imm\&GPR[rt]<-GPR[rs] OR imm\&访存类\&lw rt, offset(base)\&GPR[rt]<-mem[GPR[base]+offset]\&sw rt, offset(base)\&mem[GPR[base]+offset]<-GPR[rt]\&跳转类\&beq rs, rt, offset\&if(GPR[rs]==GPR[rt]) then转移\&bne rs, rt, offset\&if(GPR[rs] ≠GPR[rt]) then转移\&jr rs \&PC <- GPR[rs]\&jal target\&PC <- PC31..28||instr_index||02

GPR[31]<-PC + 4\&]endprint