提高器件热阻仿真值与测试结果契合度的方法

赵鹤然,康锡娥,马艳艳

(中国电子科技集团公司第四十七研究所,辽宁沈阳110000)

提高器件热阻仿真值与测试结果契合度的方法

赵鹤然,康锡娥,马艳艳

(中国电子科技集团公司第四十七研究所,辽宁沈阳110000)

随着集成电路小型化、集成化、大功率化的迅猛发展,电子封装的热阻参数越来越得到用户和封装、测试工程师的关注。特别是大功率MOS器件,热管理问题直接影响其可靠性。针对一款金属封装电路,采用ANSYS 17.0数值模拟的方法,对外壳热阻进行了仿真分析,得到RTH(J-C)和RTH(J-A)的理论值。通过对比热阻测试结果与仿真结果的差异,对仿真模型和仿真方法进行了修正,得到了提高仿真结果与测试结果契合度的方法。通过进一步研究,给出了芯片制造、封装工艺中的各个元素对热阻的影响。

热阻;流片和封装;数值模拟;功率器件;方法优化

1 引言

计算机仿真模拟在国内封装设计中主要应用在工程实践和学术研究两个领域。工程实践关心的是设计成本,周期,工艺控制能力及仿真结果能否满足需求。学术研究则更深入的探究机理,寻求算法创新,他们对求解精度有更高的要求。随着IC技术的发展,工程实践和学术研究相结合的模式需求日益迫切[1-2]。在大功率MOS器件领域,电路热性能已不仅仅局限于封装工艺本身,而逐渐发展成芯片设计、芯片制造、封装工艺控制共同影响,电路热阻仿真对计算量和模型细节的要求都达到了新的高度[3-4]。

根据GJB7400对电路外壳设计的要求,研究所承接的项目,在设计定型初期就需要给出较为准确的外壳热阻参数。越来越多的软件使用者,需要在求解精度和计算效率之间寻求平衡,探索最优的仿真方法,在保证结果可信度的前提下,最大限度的提高电路外壳热阻仿真效率。

2 模型建立

2.1 基于JEDEC标准测试条件的热网络模型

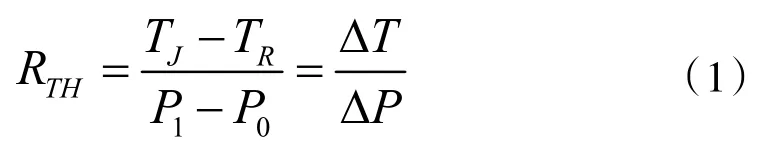

对于单一芯片的封装结构,热阻RTH计算方法比较成熟,通过选取不同的参考点,可以得到RTH(J-C)、RTH(J-B)和 RTH(J-A),如公式 1 所示:

其中,RTH为热阻值,单位为℃/W;TJ和TR分别为PN结和参考点的稳态温度,单位为℃;P1和P0分别为测量试验结束和开始稳态下芯片发热功率(后者一般取0W),单位为W;ΔT/ΔP为热流模型中温升与发热功率的比值。

从IC封装的角度出发,RTH(J-C)节-壳热阻主要由外壳和互连结构设计决定,最能直观表征产品的散热能力[5]。GJB548B方法1012对外壳热阻测量点也有相应的规定,对于正向贴装芯片的电路,较为关注TC(Bottom);而JEDEC标准关注的侧重点是外壳与散热片相连的一侧,有时可能是TC(Top)。在实际应用中,很难不破坏密封结构直接测量到芯片结温,目前,电—热结温测试方法成为了较为可行且有实际意义的封装热阻标定方法。结合本例中的MOS器件,其热阻网络如图1所示:

图1 器件热阻网络模型

2.2 封装模型建立

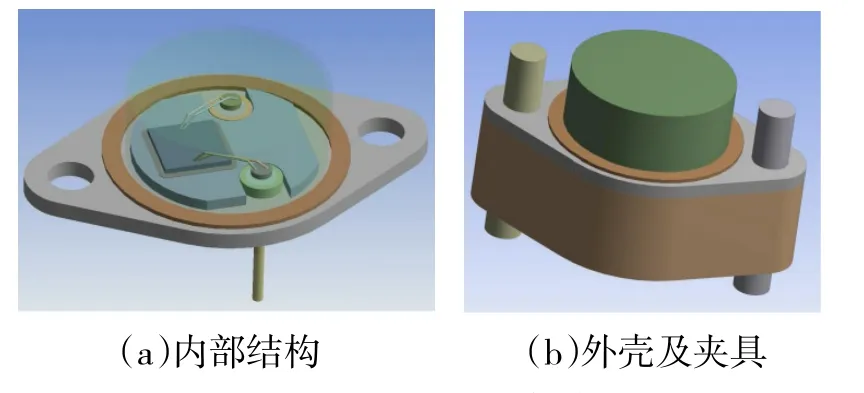

以TO-3封装结构为模型,有一颗MOSFET芯片,采用不导电胶和引线键合的方式与外壳互连,热阻的测试和仿真均使用电路专用夹具,几何模型如图2所示。

图2 封装的几何模型

环境温度取室温25℃。模型的总网格数为573万(网格数增加到876万,计算值变化量在1%以下)。模型的主要材料和参数如表1所示:

表1 主要材料和参数

3 仿真方法的修正和优化

3.1 基于封装工艺的精细化建模

以往有限元仿真计算常常使用简化模型。随着软件的更新换代和服务器求解能力的提升,研究人员发现,模型的细节对计算结果的影响很大,不应直接忽略。在此基础上,需要根据封装工艺的具体情况,进行精细化建模。

例如对于多引线键合的电路,Wire_Bond在计算中被忽略后,得到的计算结果误差就很大了[6]。在分析一个问题时,需要综合考虑理想精度、工作量、设计成本以及计算机硬件条件,从而在计算效率和精度之间确定一个平衡点。

3.2 基于芯片加工工艺的精细化建模

热阻模型应充分考虑芯片选型和制造工艺,不能泛泛按照整体热源来处理。以图3中MOSFET为例,源、漏极导通后,电流通过芯片横向的区域,可以等效为芯片发热的热源。硅基晶圆在生长氧化层之后,SiO2热导率比Si小的多[7]。同时,由于氧化层很薄,热源位置实际很靠近芯片上表面。热阻测试时,热量是经过芯片内部传导到芯片外边界的,直接忽略芯片内部材料差异会对计算结果会产生很大影响。将热源分块建模,可以有效解决上述问题。

图3 芯片加工工艺对热源条件的影响

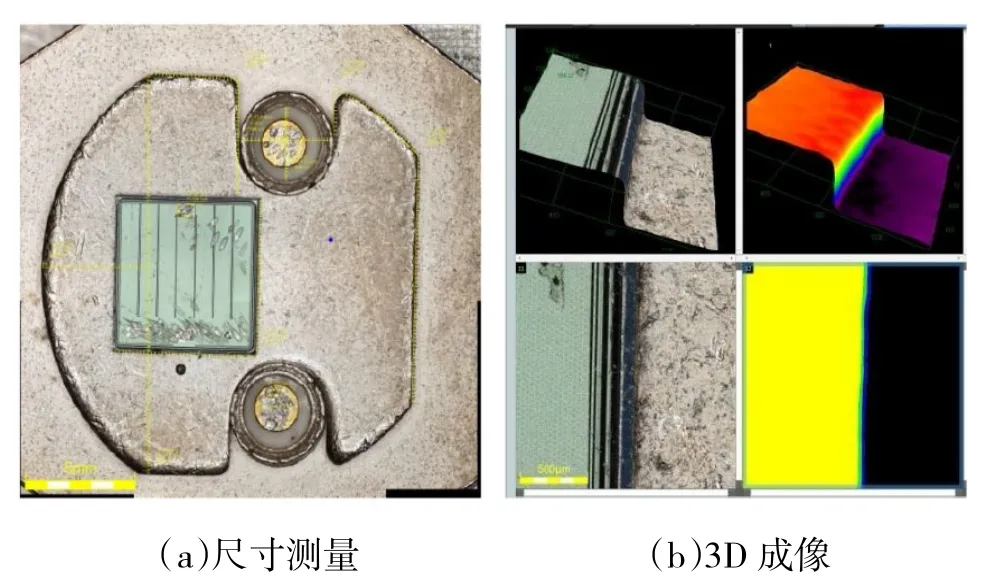

3.3 基于形貌分析仪的3D尺寸测量

实际生产中,工程师将实体模型转化为有限元模型的过程往往会丢失很多有用的信息。特别是模型关键部位的尺寸,若是误差较大,必然导致结果失真。借助立体显微镜对封装后的半成品电路进行3D观察,可以找回遗失的必要信息,是实现精细化建模的有效辅助手段。图4为使用Olympus公司DSX形貌分析仪实现的3D成像和尺寸测量示例:

图4 封装结构尺寸的3D测量

3.4 基于精密组装中心的产品一致性控制

从某种意义上说,测试是产品性能的抽样评价,仿真是对产品的普遍性能的评估。而产品一致性就是连接普遍性和抽样样品的纽带。只有保证了一致性,才能确保抽样测试结果对批量产品的代表性,进而通过仿真完成产品性能的预评估。

多项研究表明,Die_Attach是影响封装热阻的最关键因素之一,主要体现在粘接层空洞率、厚度和固化效果的控制上[8]。使用T-6000精密组装中心,在固晶过程中应用图像分析手段,可以实现芯片精确对准,保证高精度着片。同时,控制聚合物(焊料)用量、固化压力以及固化温度,是提高Die_Attach一致性,降低焊料热阻的有效手段。

3.5 网格无关性验证

有限元求解的方法,网格划分的越密集,求解的结果越接近实际值。不过,即使网格再密,数量也是有限的。这时,需要做网格无关性验证。对网格进行加密后(特别是保证边界层网格质量),如果得到的结果与加密之前的结果差别在工程师认可的范围内,即可认为当前网格划分与计算结果无关,这是有限元分析的前提。

3.6 求解模型对结果的影响

一般认为,在较低温升下,热辐射对热源散热的影响并不明显。但实践中发现,热量确实越过了芯片与测量点之间的空气,直接辐射到测量介质上。通过测试结果与仿真结果的对比可以看出,不考虑辐射的情况下,仿真结果通常比测试结果高。因此,为了修正仿真结果,需要反复修正模型的辐射系数。同时,也应尽量选取较高的求解方程阶数。

3.7 规范测试流程减小测试误差

实测值是评定仿真准确性的标准,但任何测试都存在误差。尤其是封装热阻的测试,受人员、环境、设备等因素影响较大[9]。参考点的定位、环境介质和固定热偶的导热胶材质等,都是影响测量准确性的关键因素,建议由专业测试工程师多次测量求平均值。

4 仿真结果及分析

4.1 求解方法与结果对比

对于BGA、PGA和一些标准引线框架形式的封装,使用Cadence公式的SIP和PowerDC模块可快速实现热阻参数的提取。TO管壳结构较为特殊,可采用ANSYS完成封装热阻的仿真。一般塑封和灌封器件可以按照传热学,可先求解出气体和固体介质之间的热对流系数,使用steady-state Thermal模块按热传导的理论计算;对于储能焊和平行缝焊的器件,由于管壳内存在气体介质,也可考虑对流和辐射。

以一款所内封装的电路为例,按照2.1-2.7提出的方法,对仿真和测试过程进行了双向优化,热分布云图如图5所示。仿真过程首先建立了简化的基础模型,然后做了网格的优化,在此基础上又进行了精细化建模,最后完成求解方法的优化,由此得到了四个对比模型。图6是RTH(J-C)的仿真结果和测试结果对比,图7是RTH(J-A)测的仿真结果和测试结果对比:

图5 封装热阻模型的热分布情况

图6 RTH(J-C)仿真结果与测试结果对比

由结果可以看出,RTH(J-C)对于模型精度的依赖较高,优化模型可以大幅提高仿真值与测试结果的契合度。这是因为,结、壳之间的温度传播以热传导为主,其热阻值的主要决定因素是封装材料和封装工艺,精细化建模可以充分模拟出芯片到外壳参考点的各个热通路的热分布情况,计算准确度也就大大提高了。同时,RTH(J-A)的仿真值准确度主要取决于网格和算法。这是因为,RTH(J-A)的主要计算量集中在封装外壳和环境气体之间,也就是说,固体外边界条件,特别是对流换热系数,是计算的重点。边界网格质量、气体模型和求解方程的阶数是直接影响RTH(J-A)计算准确度的关键因素。

图7 RTH(J-A)仿真结果与测试结果对比

4.2 精细化建模对仿真结果的影响

精细化建模的目的,就是使仿真计算的有限元模型与实际器件的芯片制造、封装工艺高度一致。为了探讨精细化建模对对仿真结果的影响,我们以热载荷加载位置、固晶材料、焊接空洞、Die_Attach厚度、Wire_Bond模型、关键材料选型等条件为变量,分别进行仿真,得到的结果与初始模型的仿真结果相比较,给出了精细化建模中各个元素对仿真模拟值影响的大小,对比结果如表2。

表2 模型中各个元素对RTH(J-C)和RTH(J-A)的影响Tab.2 Effect of refined modeling to simulation results

由模型01可以看出,对于引线数量很少的电路,Wire_Bond模型对 RTH(J-C)和 RTH(J-A)的影响均微乎其微。从模型00-04看出,芯片加工工艺(热源的位置)和封装工艺(焊料情况)对RTH(J-C)的仿真结果影响很大。因此,用于计算热阻参数的有限元模型应能够充分体现出芯片真实发热情况,这是保证仿真、测试结果的匹配的前提。从模型05-06看出,焊料空洞率的波动对RTH(J-C)的仿真和测试结果产生了很大的干扰。提高产品的一致性,将产品空洞率控制在5%以内,能有效提高仿真结果和测试结果的契合度。另外,外壳材料,固晶材料对RTH(J-C)和RTH(J-A)都有很大影响。综上,精细化建模提高对RTH(J-C)的模拟准确度起到关键作用。

5 结束语

利用ANSYS旗下的有限元软件,以TO-3管壳为模型,讨论提高热阻仿真值与测试值契合度的方法,指出了精细化建模和求解方法优化对提高RTH(J-C)模拟准确度起到了关键的作用;同时,指出了提高网格质量和提高求解算法的精度可以增加RTH(J-A)仿真值的准确度。

通过对精细化建模的进一步对比分析,给出了基于芯片制造、封装工艺的各个元素对于热阻值的影响,发现芯片制造、固晶条件和材料选型都会很大程度的干扰RTH(J-C)的仿真准确性。

[1]彭洋洋.微波/毫米波单片集成收发机中关键电路的设计及其小型化[D].浙江:浙江大学,2012.Peng Yangyang.Design and Miniaturization of Key Circuits in Microwave/Millimeter Wave Monolithic Integrated Transceivers[D].Zhejiang:Zhejiang University,2012.

[2]金撼尘.微电子技术发展的新领域[J].电子世界,2014(9):5-6.Jin Hanchen.A New Field of Microelectronics Technology Development[J].Electronics World.2014(09):5-6.

[3]Wu H,Chen M,Gao L,et al.Thermal resistance analysis by numerical method for power device packaging[C]//International Conference on Electronic Packaging Technology and High Density Packaging.IEEE,2012:666-670.

[4]Cong Yue,Jun Lu,Xiaotian Zhang and Yueh-Se Ho,et al.Effects of Package Type,Die Size,Material and Interconnection on the Junction-to-Case Thermal Resistance of Power MOSFET Packages[C]//2011 International Conference on Electronic Packaging Technology&High Density Packaging,Shanghai,China,Aug.2011,pp.567-572.10.

[5]王静.LED前照灯近光系统实现及散热机理研究[D].江苏大学,2014.Wang Jing.Implementation and Heat Dissipation Mechanism Research of LED Headlamp Passing Beam System[D].Jiangsu:Jiangsu University.2014.

[6]王剑峰,刘斯扬,孙伟锋.基于ANSYS的TO-220封装功率器件热特性校准及优化设计 [J].电子器件.2015,34(04):734-738.Wang Jianfeng,Liu Siyang,Sun Weifeng.Thermal Characteristic Calibration and Optimization of TO-220 Package Power Device Based on ANSYS Software[J].Chinese Journal of Electron Devices.2015,34(04):734-738.

[7]Azoui T,Tounsi P,Dupuy P,et al.3D Electro-thermal Modeling of Bonding and Metallization Ageing Effects for Reliability Improvement of Power MOSFETs[J].Microelectronics Reliability,2011(51):1943-1947.

[8]吴昊,陈铭,高立明,李明.粘结层空洞对功率器件封装热阻的影响[J].半导体光电.2013,34(02):226-230.Wu Hao,Chen Ming,Gao Liming,Li Ming.Effect of Solder Layer Voids on the Thermal Resistance of Power Device Package[J].Semiconductor Optoelectronics.2013,34(02):226-230.

[9]康锡娥.功率MOSFET器件稳态热阻测试原理及影响因素[J].电子与封装.2015(06):16-18.Kang Xi'e.The Principle and Influence Factors of the Thermal Resistance of Power MOSFET Device[J].ELECTRONICS&PACKAGING.2015(06):16-18.

Methods to Fix Simulation Value and Measurement Results of Thermal Resistance of Electronic Device Package

Zhao Heran,Kang Xi'e,Ma Yanyan

(The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China)

With the development of integrated circuits,devices become miniaturized,integrated and high-power,IC packaging and testing engineers are increasingly concerned about the heat resistance of electronic devices.Especially high-power MOS devices,thermal management directly affects the reliability of the product.For a metal casing circuit,using numerical simulation method to analyze the thermal resistance of case,obtained theoretical value of RTH (J-C)and RTH (J-A)Compared the difference between the thermal resistance test and simulation results,improved simulation models and methods,fixed the simulation and test results.Studied the influence on the thermal resistance of chip manufacture and package technology.The results showed that chip manufacturing and packaging technology have a great impact on both resistance test and simulation.

heat resistance;package technology;numerical simulation;high-power devices;method optimization

10.3969/j.issn.1002-2279.2017.05.008

TN302

A

1002-2279-(2017)05-0027-05

赵鹤然(1986—),男,辽宁省沈阳市人,工程师,硕士研究生,主研方向:电子封装设计及失效分析。