基于CSMC 0.5微米混合信号工艺的ESD保护电路实现

李湘君

(中国电子科技集团公司第四十七研究所,沈阳110032)

基于CSMC 0.5微米混合信号工艺的ESD保护电路实现

李湘君

(中国电子科技集团公司第四十七研究所,沈阳110032)

ESD保护电路已经成为CMOS集成电路不可或缺的组成部分,MOS器件的栅氧化层面积小、厚度薄,因此在测试、封装和应用过程中,来自人体或设备的静电电荷可产生的高达几千伏以上的电压,足以使栅氧化层击穿,造成器件失效。根据选用的CSMC 0.5μmFEOL 0.35μm BEOL_Mixed_Signal工艺推荐的ESD保护结构,完成输入级、输出级及电源地的ESD电路设计,同时根据版图设计规则,完成了芯片端口ESD设计。

ESD保护电路;输入级电路设计;输出级电路设计;电源地电路设计;版图设计;混合信号工艺

1 引言

随着现代集成电路的发展,工艺尺寸越来越小,氧化层越来越薄,这在降低了单个芯片的制造成本的同时却导致了器件对外界电磁骚扰敏感程度的大大提高,使静电放电对器件可靠性的危害变得越来越显著。尤其对于深亚微米工艺集成电路来说,静电的损害更加严重,所以必须在设计芯片时加入适当的静电放电(Electrostatic Discharge,ESD)保护电路以减少对芯片内部的损伤[1]。同时,芯片I/O管脚和电源管脚的数目随芯片规模的增长也不断增长,且由于管脚越多,芯片与环境的接触的机会就越多,ESD冲击对芯片造成损伤的机率也大大增加。另外,多种不同制造工艺的发展和使用,要求有不同的ESD保护结构,由于工艺的改变,用作ESD保护器件的特性发生了变化,原来有效的ESD保护方法不再有效,必须重新设计适应新工艺的ESD保护结构 , 故 针 对 CSMC 0.5μmFEOL_0.35μmBEOL_Mixed_Signal工艺,设计一款对I/O端口及电源地端口的ESD保护电路。

2 ESD保护电路原理

抗静电保护电路设计就是在电路的端口增设保护电路(器件),使得静电电荷形成的高压通过保护电路(器件)泄放掉,而保护电路(器件)自身不被破坏,使电路得到永久保护[2]。

抗静电保护电路(器件)的设计思想,一是放电电阻尽可能小,放电回路能承受高的瞬态功耗;二是不影响电路的正常功能,占用尽可能小的芯片面积。根据不同的工艺条件以及应用要求,可采用不同的抗静电保护电路(器件)[3-4]。

3 CSMC 0.5μm ESD电路结构分析

所选的 C SMC 0.5μmFEOL_0.35μmBEOL_Mixed_Signal工艺可以实现HBM-2kV ESD保护指标,工艺推荐的ESD保护电路如图1、图2、图3所示。

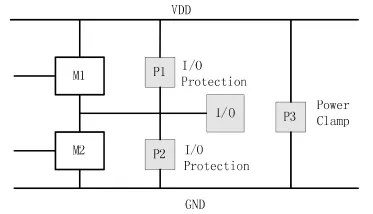

图1 工艺推荐的带GDPMOS管的端口ESD保护结构

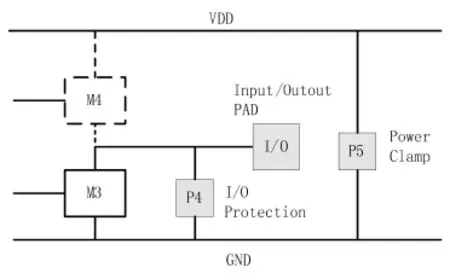

图2 工艺推荐的不带GDPMOS管的端口ESD保护结构

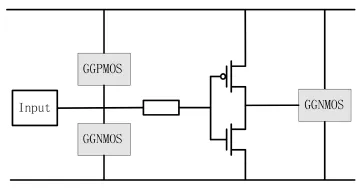

图3 工艺推荐的带输入电阻的输入级ESD保护结构

图1 中M1、M2为端口输入/输出驱动管,P1、P2、P3为ESD保护管,对于工作电压小于5V的低电压设计,M1、M2参照ESD保护管设计规则设计,P1、P2ESD保护管可以省去;图2与图1类似,只是没有GDPMOS保护管,对于工作电压小于5V的低电压设计,M3参照ESD保护管设计规则设计,P4保护管可以省去;图3比图1(作输入)多了一个输入电阻,这是一种常用的ESD保护方案,通常用于低工作电压设计。

4 ESD保护电路设计

全芯片ESD保护通常包括:输入级保护电路、输出级保护电路、电源地保护电路。

4.1 输入级ESD设计

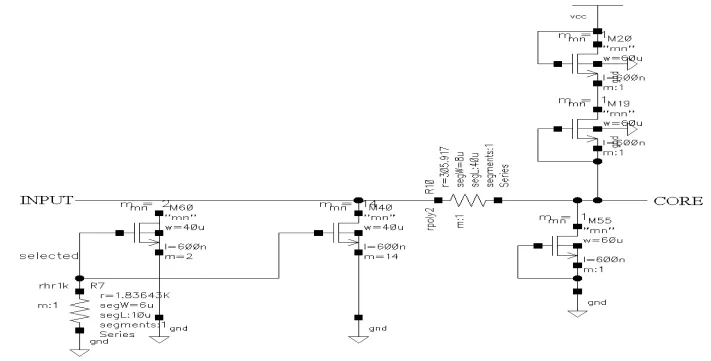

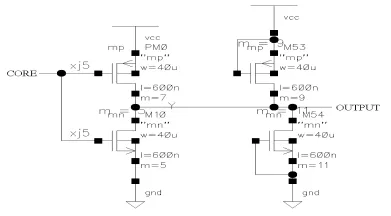

研制芯片的工作电压范围为2~5.5V,输入电压范围为0~5.5V,若输入端口上有GDPMOS保护管,当供电电压为2V或3.3V且输入电压增大至比VCC大一个|VGS(th)|时,PMOS保护管会发生导通漏电,故输入端口不能有GDPMOS保护管,以防止产生漏电。电路采用GGMOS管的主次级ESD保护结构[5-6],如图4所示。

图4输入级ESD保护电路的主级结构没有GDPMOS保护管,主次级ESD保护结构的输入电阻采用多晶电阻,约为200Ω;次级结构用两个串联的NMOS保护管代替GDPMOS保护管。在芯片正常工作电压范围内,串联的两个NMOS保护管不会同时导通,避免了漏电流的产生。当输入端口对电源PAD放电时,串联的两个NMOS保护管可以等效为一个电阻与GGNMOS管的串联,主要用于输入端口的电压箝位,而ESD电流的泄放主要是通过电源地间的ESD放电通路实现[7]。

4.2 输出级ESD设计

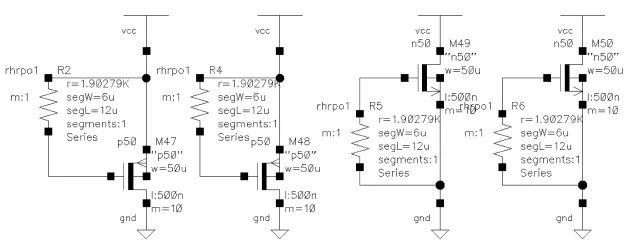

输出级ESD保护结构如图5所示,输出级采用ESD保护管做输出驱动,并添加了一对GGMOS保护管,增强输出级ESD保护能力。

图4 GGMOS输入级ESD保护结构

图5 输出级ESD保护结构

4.3 电源地的ESD设计

电源地ESD保护电路采用四个ESD保护管实现,每个均接成类似GGMOS的结构,只是在保护管栅与源端串联一个高阻值的多晶电阻,用于实现保护管(叉指结构)各个“手指”的有效导通[8]。如图6所示。

图6 电源地ESD保护结构

5 ESD保护电路版图设计

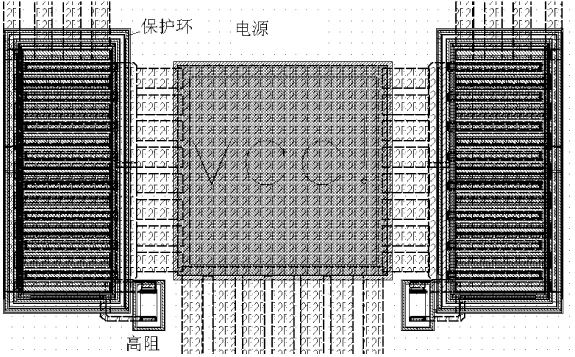

根据CSMC 0.5μmFEOL_0.35μmBEOL_Mixed_Signal工艺版图设计规则,按照电路结构进行版图设计,下面针对电源的ESD版图设计为例介绍,如图7所示。

按图6电源的ESD逻辑结构,设计出了图7所示的版图结构。由于大尺寸的PMOS或者NMOS器件本身可以充当防护器来用,且为了能够在较小面积内画出这样大尺寸的器件,所以在版图设计时需要画成叉指结构。首先在PAD的两端分别对称排布一个叉指结构的PMOS管;其次在栅、源间串接一个1~2kΩ的电阻,以保证芯片引脚受到ESD攻击时,叉指结构ESD保护管的所有“手指”均导通工作,提高ESD保护管工作的可靠性;再次在PMOS管的外端增加一个连接到电源上的保护环[9],用来区分不同的功能电路,同时保护环还可以区分外围电路和核心电路,还可用于电路内部避免闩锁效应。通过上述多重保护手段使得电源的PAD得到有效的静电保护。

图7 电源的ESD版图设计

6 结束语

根据CSMC 0.5μm混合信号工艺推荐的ESD保护电路结构,完成输入级、输出级及电源地的ESD保护电路设计;利用叉指结构、保护环结构以及栅、源间串接一个1~2kΩ的电阻结构完成了版图设计,设计出了一款端口具有抗静电能力,通过人体放电模型(Human-Body Model,HBM)2000V的芯片。

[1]马巍,郝跃.LDD-CMOS中ESD及其相关机理[J].半导体学报,2003,24(8):892-896.Ma Wei,Hao Yue.LDD-CMOS of ESD and its Related Mechanism [J].Journal of Electrostatics,2003,24(8):892-896.

[2]王颖.MOS集成电路ESD保护技术研究[J].微电子技术,2002,30(1)25-28.Wang Ying.Mos Integrated Circuit ESD Protection Technology Research[J].Microelectronics Technology,2002,30(1)25-28.

[3]WANG A Z,FENG H G,GONG K et al.On-chip ESD Protection Design for Integrated Circuits:An Overview for IC Designers[J].MicioelectronicsJournal,2001,32(9):733-747.

[4]Voldman S.H,Gerosa G.,Gross V.P,et al.Analysis of Snubber-Camped Diode-String Mixed Voltage Interface ESD Protection Network for Advanced Microprocessors[J].Journal of Electrostatics,1996,38:3-31.

[5]Dabral S,Aslett R,Maloney T.Designing On-chip Power Supply Coupling Diodes for ESD Protection and Noise Immunity[J].Journal of Electrostatics,1994,33:357-370.

[6]Amerasekera A,Duvvury C.ESD in Silicon Integrated CircuitsSecond Edition[M].NewYork:JohnWiley,Sons,2002.

[7]李若瑜,李斌,罗宏伟.栅长L对GGNMOS抗静电能力的影响[J].电路与系统学报,2005年10月,10(5):93~95.Li Ruoyu,Li Bin,Luo Hongwei.The Influence of Gate Length L of GGNMOS Antistatic Ability[J].Journal of Circuits and Systems,2005.10,10(5):93~95.

[8]向洵,刘凡,杨伟等.基于CMOS工艺的全芯片ESD保护电路设计[J].微电子学,2010,40(3):396~399.Xiang Xun,Liu Fan,Yang Wei,et al.Design of All Chip ESD Protection Circuit Based on CMOS Process[J].Microelectronics,2010,40(3):396~399.

[9]王大睿.CMOS电路中ESD保护结构的设计[J].中国集成电路,2007(6):37~41.Wang Darui.Construction Strategy of ESD Protection Circuit[J].China Integrated Circuit,2007(6):37~41.

Implementation of the ESD Protection Circuit Based on CSMC 0.5 Micron Mixed Signal Process

Li Xiangjun

(The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China)

ESD protection circuit has become an integral part of CMOS integrated circuit.MOS device gate oxide area is small,and the layer thickness is thin,therefore in the process of testing,packing and application,electrostatic charge from the human body or equipment can produce as much as more than a few kV voltage enough to make the gate oxide breakdown,and cause device failure[1].According to the ESD protection structure recommended by the selected CSMC 0.5μm FEOL_0.35μm BEOL_Mixed_Signal process,the ESD circuit of input level,output level and power ground is designed,meanwhile,the design of the chip port ESD is also achieved according to the design rules of the layout.

ESD Protection circuit;Input level circuit design;Output level circuit design;Power ground circuit design;Layout design;Mixed-signal process

10.3969/j.issn.1002-2279.2017.05.003

TN306

A

1002-2279-(2017)05-0008-04

李湘君(1984—),女,辽宁省沈阳市人,工程师,主研方向:集成电路设计。