高压高重频脉冲发生装置研制

尚明健 李 强

高压高重频脉冲发生装置研制

尚明健 李 强

(西南科技大学信息工程学院,四川绵阳 621010)

本文介绍了一种高压高重频脉冲发生装置的研制过程,装置主要由脉冲信号源,驱动电路和功率放大电路组成。本文详述使用FPGA设计脉冲信号源的方法,驱动电路中脉冲整形电路的设计思路和在功率放大电路中降低电路寄生参数的手段。装置在1MHz重频下工作,在50W负载上测得脉冲前沿低于14ns。

FPGA;脉冲整形;1MHz重频

高压高重频脉冲发生装置是可以在高重复频率下运行并产生高压脉冲的脉冲功率系统[1]。该类装置在材料、环保、生物医疗、光源和高能加速器领域均有代表性应用[2]。脉冲发生装置输出脉冲的幅度、频率、脉宽决定了装置的应用场合,比如针对感应式回旋加速器设计的脉冲源就要求MHz重频,且对脉冲的前沿也会有一定要求,如果脉冲的前沿不够陡峭,就会严重影响加速效果[2-4]。为了达到高重频或高压,目前该类装置多采用微机或FPGA控制功率MOSFET或IGBT的方式[1,5]。

本文介绍了一种高压高重频脉冲发生装置的研制过程,包括窄脉冲信号源、驱动电路、功率放大电路3个主要的组成部分。文中详细叙述了各部分电路的工作原理和设计要点。最终的测试结果表明,该装置可在1MHz重频下工作,且脉冲前沿低于14ns。

1 系统整体结构和工作原理

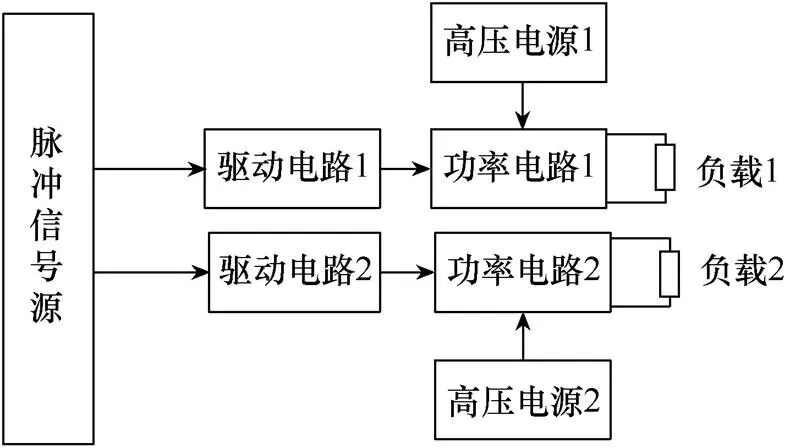

图1所示为系统的整体结构。该系统主要由脉冲信号源、驱动电路、功率电路构成。其中脉冲信号源产生脉冲信号,该信号作为驱动信号送入驱动电路中用于控制功率电路中的功率MOSFET导通或关断。系统在使用时首先使用高压电源给功率电路中的储能电容充电,充电完成后,电源即断开,此时使能脉冲信号源的触发功能即可在负载端测得对应幅值及脉宽的高压脉冲信号,试验中所用的负载为50W阻性负载,两路脉冲发生装置相互独立。

图1 系统整体结构

对于整个系统而言,驱动信号的前后沿过于缓慢会导致功率MOSFET无法及时开关,而出现震荡甚至会导致MOSFET出现误触发,功率电路中的寄生参数如寄生电阻过高会使输出高压脉冲的前沿变缓,幅值降低,而寄生电感过高甚至会引起输出波形出现震荡。所以良好的驱动信号应当接近于方波,而功率电路中的寄生电阻和寄生电感都应尽量低。

1.1 脉冲信号源设计

脉冲信号源的作用为按照设定值发送一定频率、脉宽和个数的窄脉冲序列。设计中需要着重考虑减小输出信号的抖动与偏移,同时精简装置的结构缩小装置的体积。

1)嵌入式系统构建

为保证装置的稳定性并缩小体积,采用单片FPGA实现数字控制器的全部功能,但是由于使用纯硬件逻辑电路会带来巨大的硬件开销,所以在FPGA中嵌入了一个MicroBlaze软核(单线程CPU软核),利用CPU在运行时不产生额外的硬件开销、只是读取相应的机器码完成对应操作的特点,减少FPGA中乘法器、LUT等资源的消耗。但是CPU不同于纯硬件电路通过确定的硬件结构实现相应的逻辑功能,其在执行程序的过程中会执行一些中断服务子程序,导致输出信号的抖动与偏移几乎无法避免。所以在进行功能模块划分时CPU只进行复杂的数值计算或逻辑判断,对于时序要求较高的功能依旧使用纯硬件电路实现。

具体实现方式为CPU通过运算得到相应的操作码,并通过AXI总线写入相应的外设IP的内部寄存器中,外设IP读取相应的寄存器完成对应的 操作。

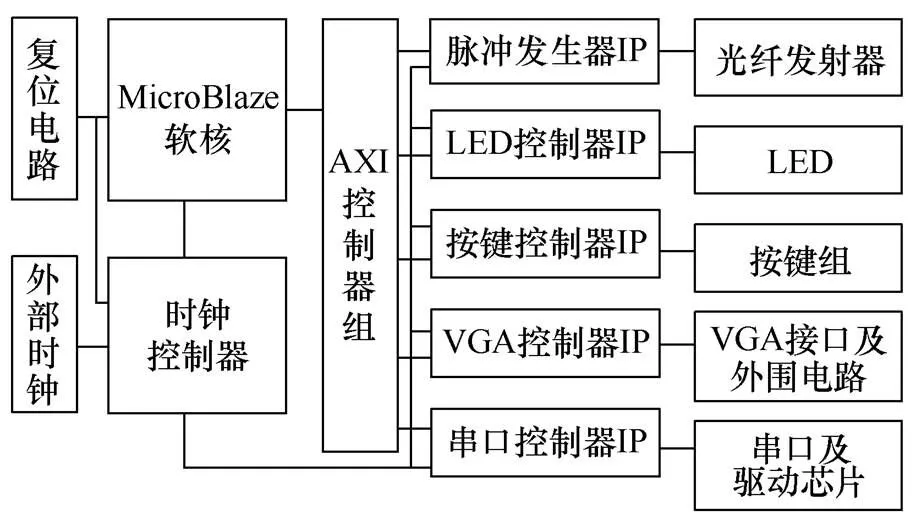

在构建嵌入式系统时,先由功能入手考虑系统的结构,系统所需具备结构及对应功能如下:①串口:与PC建立通信完成参数设置;②按键:完成如信号触发等操作;③LED:辅助显示系统状态;④VGA接口:通过外接显示器显示系统参数;⑤光纤发射器:发送周期在500~2000ns可调且占空比不低于10%的窄脉冲信号。图2所示为构建完成的脉冲信号源系统结构。

图2虚线框内所表示的即为在FPGA内搭建的嵌入式系统。在该系统中:时钟控制器的输出决定了CPU的主频和CPU外设的时钟频率,AXI总线控制器组用于实现Microblaze软核与外设IP之间通信,从而实现CPU对外设的控制,二者为系统的基本组成部分;LED控制器和按键控制器采用设计软件自带的axi_gpio,串口控制器采用axi_uart,这一类的控制器可以自主设计,但是设计功能与之完全相同的IP不仅花费时间,而且在SDK软件中无法使用已经封装好的函数,所以在系统设计中优先使用软件自带的IP。VGA显示和脉冲输出则没有现成的IP可供使用,并且二者对于输出信号要求都较高,前者的信号质量差会导致显示内容出现虚影,后者出现抖动会直接影响高压脉冲的输出质量。因此,将二者的逻辑功能使用用户自定义IP的形式进行封装,但将显示内容、脉冲的频率、脉宽等信息统一放在CPU中进行计算。

图2 脉冲信号源系统结构示意

2)脉冲信号发生器IP设计思路

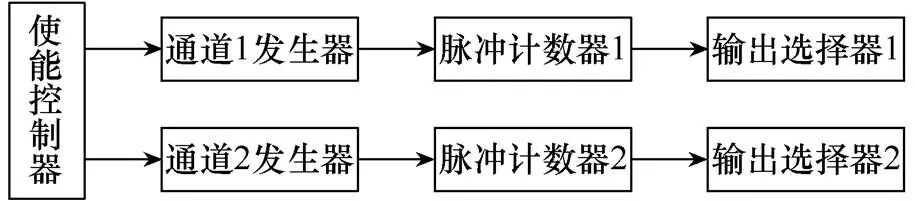

图3为脉冲信号发生器IP核的硬件结构,其工作原理如下:①使能控制器通过控制发送至通道发生器的使能信号,控制输出脉冲的相位差;②各通道的发生器用于控制脉冲的频率和脉宽;③脉冲计数器在每个脉冲的起始位置进行加计数,在当脉冲个数达到后切断脉冲输出;④输出选择器用于通道切换,实现SMA或光纤输出的功能。

图3 脉冲信号发生器IP核硬件结构

由于采用了分模块的方式,每一个功能模块仅读取对应寄存器的值,完成相应功能,所以不会出现相互串扰和数据拥塞的情况。在脉冲信号发生器中,由于后级电路的输入即为前级电路的输出,所以控制需具有一定的优先级,才能保证可靠性。

1.2 驱动电路设计

驱动电路使用光纤实现高压与低压的隔离,并完成窄脉冲信号的传输。采用光纤时由于脉冲信号源与功率电路在工作时各自的地之间可能存在很大的电势差,所以需要驱动电路具有良好的隔离作用。

图4所示为驱动电路的硬件结构。FPGA产生的窄脉冲信号经过整形电路1后进入光纤发送头经过单模光纤传输至光纤接收头,经过整形电路2整形后送入功率放大电路中。在驱动电路中整形电路1的作用是去除信号传输过程中引入的一些干扰,并将FPGA输出的3.3V信号加重至5V以满足发送的电平要求;整形电路2除改善信号的前后沿外,还有提高接收端带负载能力,并防止的功率放大电路中电流回灌损坏光纤接收头的作用。

图4 驱动电路硬件结构

在驱动电路设计中采用HFBR-2412TZ作为光纤接收头,与之配合使用的光纤发送头为HFBR- 1414Z。HFBR-2412TZ的输出电平虽为标准的TTL电平,但是逻辑与发送信号相反,整体相当于一个反向器,这一点在设计中需要特别注意。整形电路中采用是TI公司SN74F04六路高速反相器完成信号的加重或整形,同时该芯片也具有一定的隔离作用。在设计中可以多个输出通道共用一片SN74F04,但为防止出现串扰,在本文所述设计中是独立使用的,并将不用的输入端接至芯片的电源端。设计中采用如下措施可以提高输出信号的质量:①使用小封装的电容退耦(电容封装影响寄生参数);②模拟地与数字地不做分割,但将易引入接地噪声的电路和模拟电路的铺铜设置为孤岛再进行连接。

1.3 功率放大电路设计

图5所示为功率放大电路的硬件结构。在功率放大电路中,通过功率MOSFET驱动控制功率MOSFET的关断,使储能电容中的电能向负载释放产生高压脉冲。

图5 功率放大电路结构

为防止输出振荡,并使高压脉冲的前后沿更陡峭,应当减少电路中的寄生参数。该电路的寄生参数主要为寄生电阻和寄生电感,主要来自器件中的寄生参数影响和PCB走线。设计中功率MOSFET驱动选择采用IXYS公司的集成驱动芯片IXRFD630,按照IXYS公司的测试结果在CC=15V,OUT= 100mA,即驱动信号频率接近1MHz的工作条件下,该芯片在低电平输出时的输出阻抗为0.17W,有利于功率MOSFET在关断时泄荷。与驱动芯片搭配使用的功率MOSFET为IXYS公司的RF-MOSFET系列芯片DE475-102N21A,依照数据手册该MOSFET导通时漏源内阻仅为0.45W,寄生参数很低。储能电容选用941C10W1K无感电容,容值为1mF,ESR为5mW,ESL仅为24nH。在电路进行布局时器件的放置应紧凑,并使用短粗的走线;储能电容要靠近功率MOSFET的漏极和源极,而不应外接。

针对储能电容中的电能会沿限流电阻向高压电源放电,导致电压迅速下降的问题,电路中采用的解决方式是,利用空气开关的隔离作用断开高压电源与电路的连接,同时也可提高操作的安全性。

2 实验及结果分析

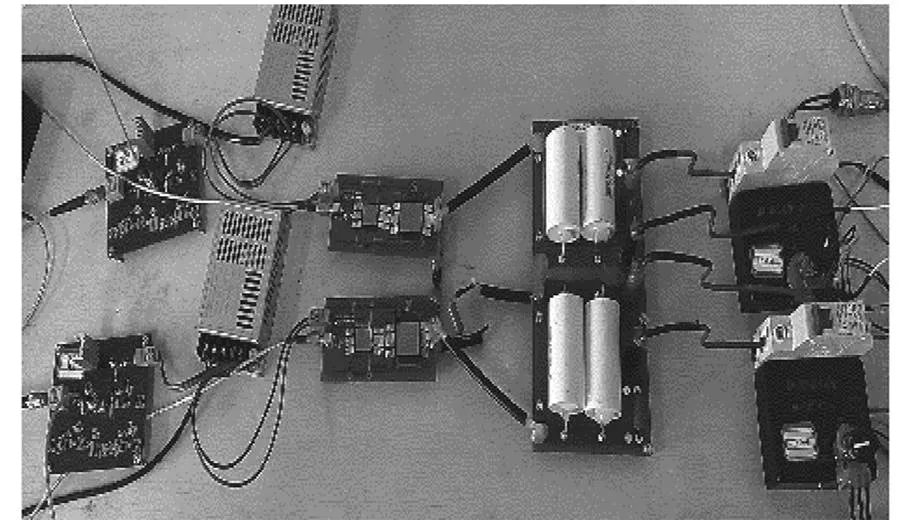

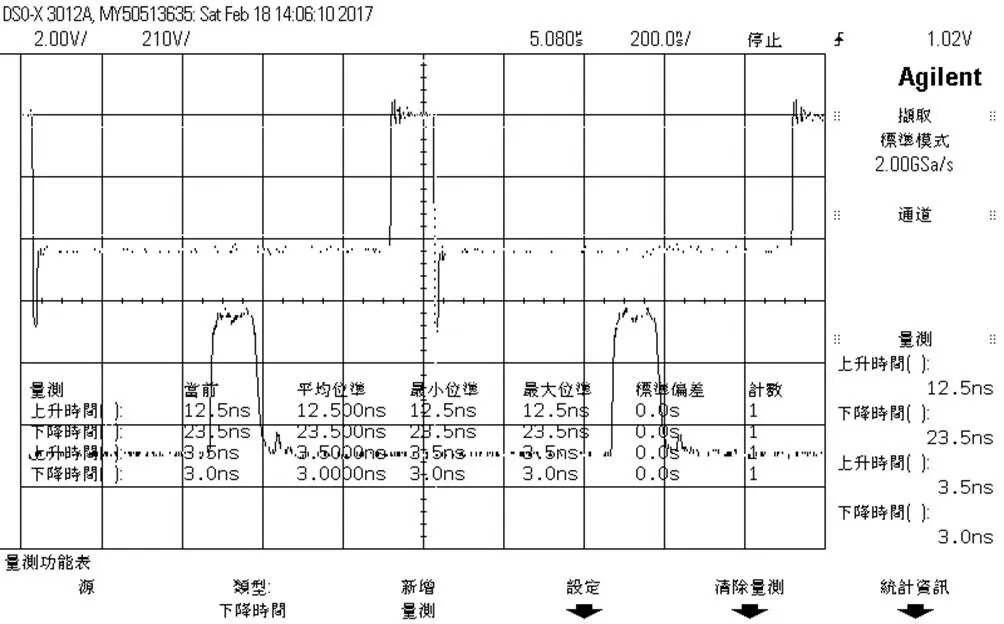

图6为实验平台的结构示意图。图7为实验装置实物图。该实验主要检测触发脉冲是否有丢失现象,以及高压脉冲的前沿是否达到标准。驱动电路2为示波器提供触发信号,保证示波器能够被稳定触发并完整记录高压脉冲的波形。试验中使用100∶1高压探头测量功率电路1输出的高压脉冲。实验以频率500kHz、1MHz在占空比为10%、20%、30%时各进行1次,设定储能电容的预充电压值为500V,并统一设置脉冲个数为10个,测试值为高压脉冲信号的上升时间,表1所示为实验结果,图8所示为1MHz,10%占空比的测试波形,图中上方的波形为示波器的触发信号,即驱动电路2的输出信号下方的波形为输出的高压脉冲。图中驱动电路2的输出出现震荡的原因主要为驱动电路2直接与示波器连接,即与后级的匹配电路完全断开;而高压脉冲中部凹陷则与实验电路中的电缆线未采用同轴的接法,且未加屏蔽所致,而图9所示,设备装机后的检测波形则未出现这种问题。

图6 实验平台结构示意

图7 实验装置实物

表1 高压脉冲输出实验结果

图8 测试波形

图9 装机后的检测波形

实验结果表明,输出高压脉冲的前沿被控制在14ns以内。此外,如测试波形图中所示,驱动电路输出信号的前后沿也未超过4ns。

3 结论

本文详述了高压高重频脉冲发生装置的研制过程。着重介绍了在脉冲信号源设计中利用嵌入的CPU软核进行参数运算,节约片内资源的消耗的方法;驱动电路中脉冲整形电路的设计要点,以及功率放大电路中降低电路寄生参数的方式。实验结果表明,驱动电路输出信号的前后沿未超过4ns,输出高压脉冲的前沿被控制在14ns以内。

[1] 张良, 秦玲, 黄子平, 等. MHz重复频率固体调制器实验研究[J]. 强激光与粒子束, 2009, 21(8): 1250- 1254.

[2] 江伟华. 高重复频率脉冲功率技术及其应用: (6)代表性的应用[J]. 强激光与粒子束, 2014, 26(3): 1-1.

[3] 郭帆, 贾伟, 谢霖燊, 等. 基于半导体开关和LTD技术的高重频快沿高压脉冲源[J]. 强激光与粒子束, 2016, 28(5): 113-117.

[4] 石小燕, 梁勤金, 潘文武. 基于SOS的高重频高压纳秒脉冲源设计[J]. 太赫兹科学与电子信息学报, 2016, 14(1): 122-126.

[5] 李冰. Marx高压脉冲电源的设计和应用[D]. 成都: 电子科技大学, 2015.

[6] 章欣. 基于FPGA的脉冲信号发生器设计[J]. 气象水文海洋仪器, 2014(2): 69-73.

[7] 杜冬, 尹学峰, 吉小军, 等. 基于FPGA的脉冲信号发生/测试仪一体化设计[J]. 电子测量技术, 2015, 38(1): 64-68.

[8] 李红梅, 籍秀斌, 王一豪, 等. 1kA脉冲电流发生器测控电路设计[J]. 电气技术, 2015, 16(9): 56-58.

[9] 李传伟, 唐镜军. 基于STC89C52RC控制的线切割高频电源设计[J]. 电气技术, 2013, 14(8): 43-47.

[10] 吴厚航. 深入浅出玩转FPGA[M]. 北京: 北京航空航天大学出版社, 2013.

Fabrication of High-repetition-frequency High-voltage Narrow Pulse Source

Shang Mingjian Li Qiang

(School of Information Engineering, Southwest University of Science and Technology, Mianyang, Sichuan 621010)

This paper introduces the development process of a High-repetition-frequency high-voltage narrow pulse source . This equipment includes pulse signal source, drive circuit and power amplification circuit. The article describes in detail about the methods of design pulse signal source with FPGA, pulse shaping circuit in the drive circuit design and reduce the parasitic parameters of circuit in the power amplifier circuit. When Device work at 1MHz repetition frequency, the rising edge of the high voltage pulse keep in 14ns on 50Wload.

FPGA; pulse shaping; 1MHz repetition frequency

尚明健(1992-),男,西南科技大学在读研究生,研究方向为测控技术及通信电路设计。

特殊环境机器人技术四川省重点实验室开放基金资助项目(13zxtk07)