基于CPLD与DSP的数字式电抗器的设计

王卫兵 徐倩 张慧峰

摘要:为了更为准确可行地根据系统内无功状态进行抵消电力线电容效应,设计了一种可以根据系统实时运行状态平滑输出所需感性无功的数字式电抗器。该数字电抗器通过控制二次侧逆变器来改变本身电感线圈的感性电流以尽量抵消接地电容电流,从而达到动态无功补偿的目的。主CPU选用DSP,并与CPLD、A/D相配合从而产生PWM以控制后续逆变电路。通过仿真和实验证明,设计的数字式电抗器具有结构简单、响应速度快、无级可调并且电感调节范围大等优点,达到了调节电力线无功平衡的作用。

关键词:数字电抗器;PWM控制技术;CPLD逻辑器件;DSP处理器

DOI:1015938/jjhust201705011

中图分类号: TP3021

文献标志码: A

文章编号: 1007-2683(2017)05-0058-07

The Design of Digital Reactor Based on CPLD and DSP

WANG Weibing1,XU Qian2,ZHANG Huifeng1

(1School of Computer Science and Technology,Harbin University of Science and Technology, Harbin 150080, China;

2Distribution Operating Inspection Office,Harbin Branch of Heilongjiang Power,State Grid Corporation of China, Harbin 150016, China)

Abstract:In order to counteract the transmission line capacitance effect relatively accurate based on the reactive power state of the system, this paper designs a kind of parallel digital reactor which can output the required perceptual reactive power smoothly according to the power system realtime reactive state This digital reactor changes the inductive current which flows through the reactors inductance coil by controlling secondary side voltage inverter to offset the grounding capacitive current DSP is used as CPU which is cooperated with CPLD and ADC to control the inverter output PWM The experimental results show that digital reactor that has the advantages of simple configuration, rapid response and wide range continuously of inductance change to reached well to adjust the action of making power penetration line reactive power balance

Keywords:digital reactor; PWM control technology; CPLD device; DSP

收稿日期: 2016-01-07

基金项目: 国家自然科学基金(61305001)

作者简介:

徐倩(1969—),女,高级工程师;

张慧峰(1989—),男,硕士研究生

通信作者:

王卫兵(1964—),男,教授,Email:wangweibing163@163.com.

0引言

在电力系统中,由电力线电容效应引起的较大对地电容电流会使电力系统在运行过程中出现长距离空载线路的空载末端电压超出额定电压、空载切除电路引起操作过电压等弊端。在电力系统中一般采用电抗器来抵消电力线上的电容效应从而改善电能质量。在实际应用中,由于系统负载及天气的影響,系统本身的无功容量会发生变化。随着我国电力事业的飞速发展,一种可以根据系统参数变化和设计需要人为改变其本身感性参数的可控式电抗器的出现对电力系统发展至关重要。

目前,按照调节方式,可控式电抗器主要分为传统机械式可控电抗器、磁控电抗器(MCR)、晶闸管控制电抗器(TCR)、PWM控制电抗器[1]和超导可控电抗器。传统的机械式可调电抗器具有电感连续可调,结构简单,容易控制,不产生滤波,但是调节精度很差,难以适应电力发展,逐渐被淘汰。磁控电抗器控制简单,结构比较复杂,能够连续平滑地调节,常用于高压线路中,但是产生的滤波比较大。晶闸管控制电抗器的结构简单[2],控制灵活,精度也较高,但需要加以专门的滤波装置,造价很高,常用于低压领域。PWM控制电抗器精度很高[3],而且引起谐波含量很小,但是操作较复杂。本文利用CPLD和DSP及高精度ADC芯片和IGBT高频大功率开关器件基于PWM原理设计一种能够进行动态无功补偿的数字式电抗器,同时通过软件仿真以及实验进行了验证[4]。

1原理分析endprint

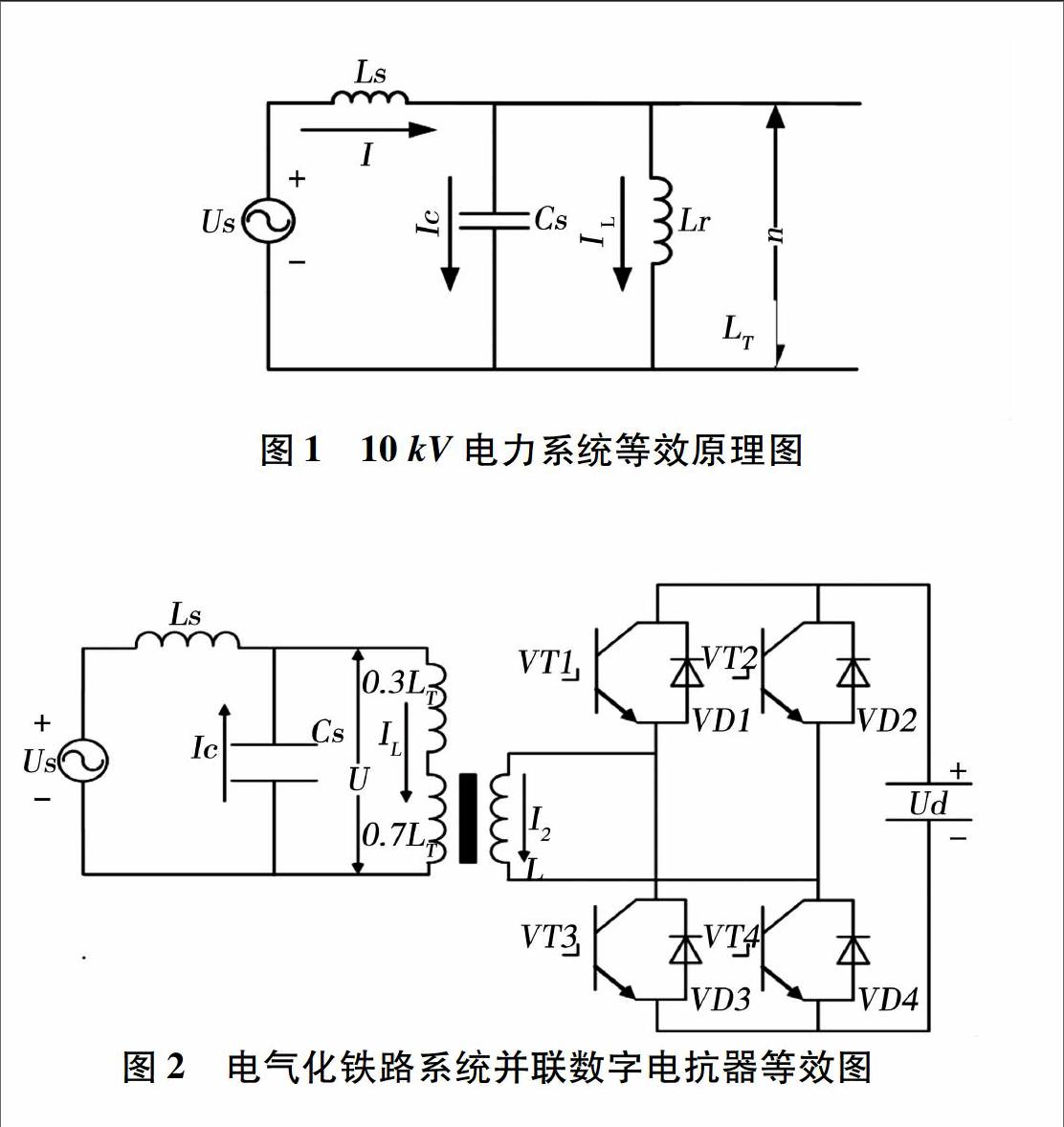

图1为10kV电力系统等效原理图。如下图所示,US为系统电源电压,LS为系统等效电感,CS为电力线等效接地电容,LT为吸收系统等效电容产生容性无功的并联电抗器。

由电工学原理可知道,在交流电路中,纯电容C中的电流ic超前端电压90°,纯电感中的电流iL,则落后端电压90°,电抗器中的电流滞后于电容电流180°[5]。根据图1可知,电感电流和电容电流方向相反,就可以减少接地电流,甚至可以完全抵消接地电流。适当选择参数可使

I·L+I·C≈0(1)

当图1系统满足式(1)时,可使电气化铁路信号灯系统的电力线的末端电压近似等于首端电压。所以可以控制电抗器的电流来补偿系统中接地电容电流。

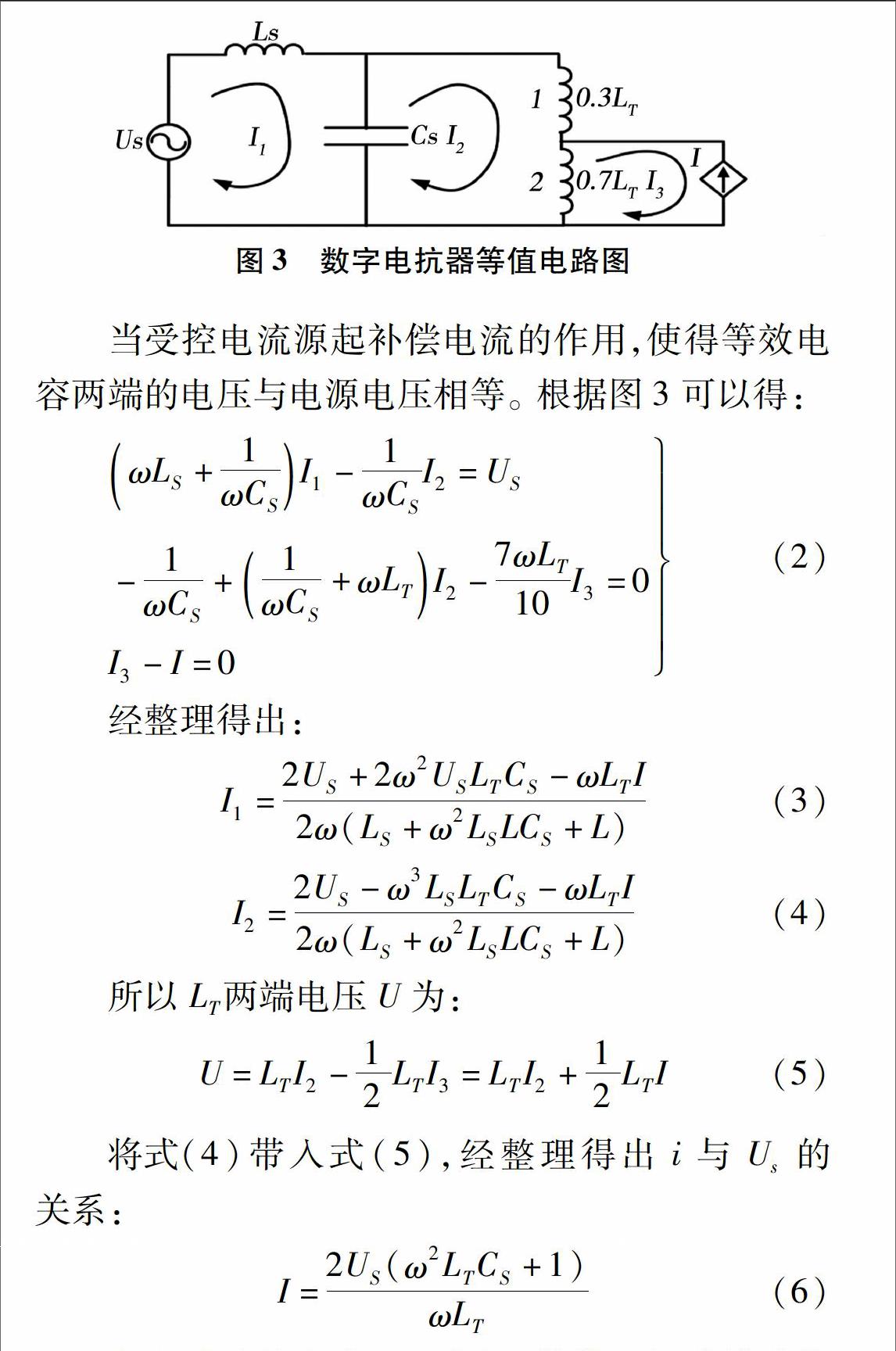

本设计提出了如图2所示的运用数字电抗器来进行电力系统无功平衡调节的系统等效图。其中US为系统输入电压;LS为系统在电力线的等效电感;CS为电力线电容效应对应的等效电容;LT为并入系统起无功平衡的电抗器。LT由电感值分别为03 LT和07 LT的兩个电抗线圈串联而成,线圈1为额定电感,并起滤除PWM产生的毛刺;线圈2起容量调节作用。由于线圈2具有二次绕组,控制二次绕组的电流形成±30%电流容量调节,并且与单相逆变器相连;控制电路由单相全桥电压型有源逆变器组成。逆变器的每个桥臂由IGBT与反并联二级管组成。该设计可根据实际需求调节输出电流,并确保输出电流谐波畸变率小于5%。电抗器的铁心应尽可能保持整体性,以减少噪音。如图2所示,电气化铁路信号灯系统并联数字电抗器系统构成等效图。其中电容电流IC与并联电抗器电流IL方向相反。本设计可完成并联数字电抗器电感电流的±30%调节,达到期望可调结果。

当10kV电力系统开始运行时,未接入并联数字电抗器时,容性无功功率产生容性电流Ic,因而电容两端电压升高,从而导致工频过电压;当接入并联电抗器时,电抗器能够吸收一部分容性无功功率,过电压会随之减小。为了使电容两端电压U与电源电压US基本相等,可以通过控制单相全桥电压型有源逆变器产生感性电流抵消等效电容产生的容性电流,最终达到并联数字电抗器实时补偿电力线对地电容电流的目的。在运行的整个过程中,若电力线等效电容、等效电感,负载发生变化,会导致系统的无功功率分布再次发生变化。为了提高电压调节的准确性,需要改变并联数字电抗器的电流,可通过该有源逆变器输出电流的大小,等效改变电抗器的感性容量,即IL≈IC,使得始终电容两端电压U与电源电压US近似相等,达到调节目的。

根据电力电子技术基础知识可知,有源逆变器可以等效为一个电流源,所以图2所示系统的等值电路图如图3所示。

当受控电流源起补偿电流的作用,使得等效电容两端的电压与电源电压相等。 根据图3可以得:

ωLS+1ωCSI1-1ωCSI2=US

-1ωCS+1ωCS+ωLTI2-7ωLT10I3=0

I3-I=0(2)

经整理得出:

I1=2US+2ω2USLTCS-ωLTI2ω(LS+ω2LSLCS+L)(3)

I2=2US-ω3LSLTCS-ωLTI2ω(LS+ω2LSLCS+L)(4)

所以LT两端电压U为:

U=LTI2-12LTI3=LTI2+12LTI(5)

将式(4)带入式(5),经整理得出i与Us的关系:

I=2US(ω2LTCS+1)ωLT(6)

由上述计算公式可以得知,若使电气化铁路信号灯系统电力线末端电压U近似等于电源电压US,可使可控电流源输出电流I满足式(6)达到调试目的。

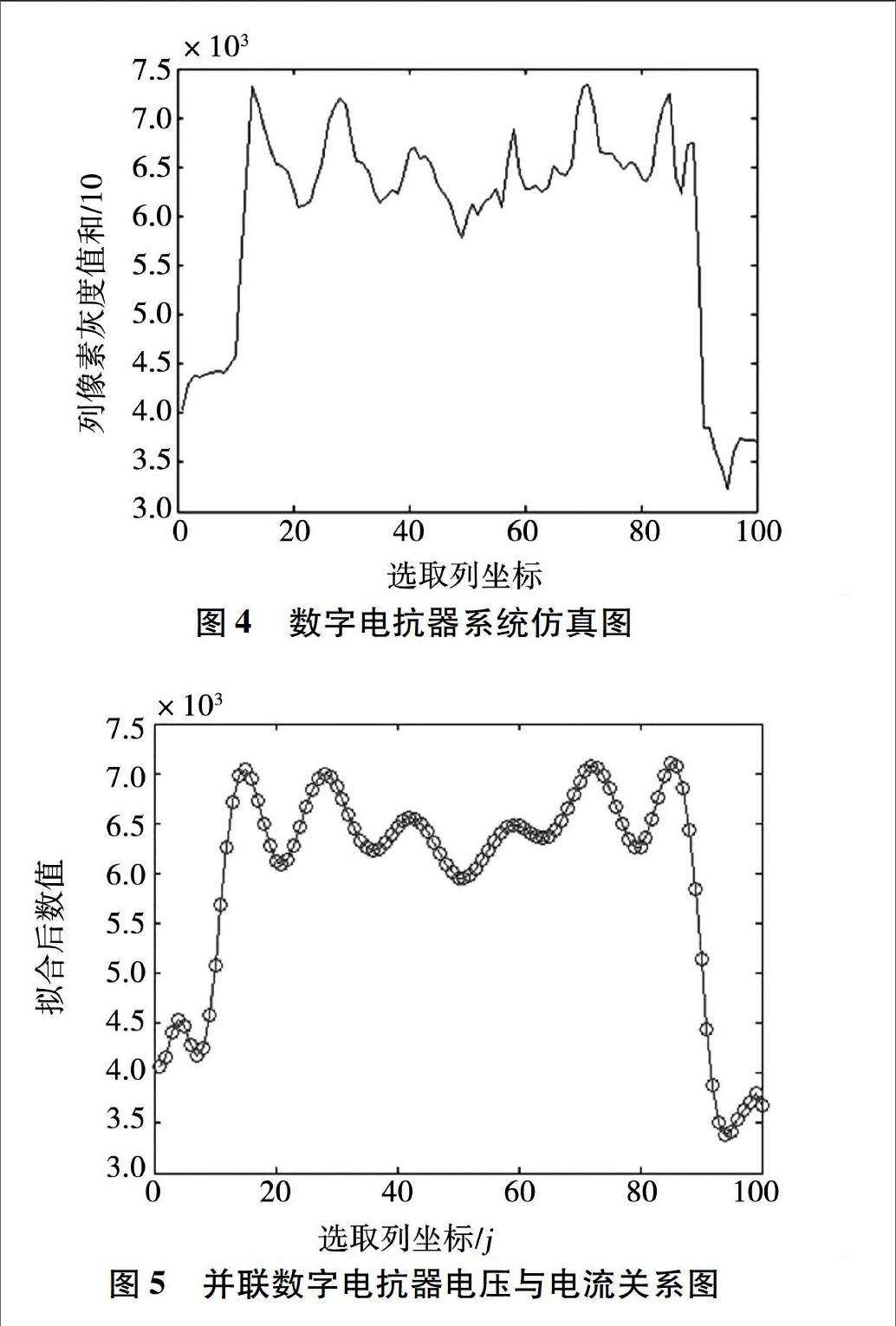

利用MATLAB软件进行仿真可以得到电抗器电感参数以及电抗器两端电压和通过电抗器电流之间的关系。仿真是在单相10kV条件下运行的,等效电感为55mH,等效对地电容为18μF,并联电抗器为60H。仿真图如图4所示,同时将得到的数据进行线性拟合,拟合结果如图5所示。在一定范围内改变电抗器电感参数,可得电抗器两端电压和通过电抗器电流之间的关系。

由上可知电抗器两端电压和通过电抗器电流满足线性关系。因此,本文在设计编程时,需要补偿的电流可以根据电压目标值进行计算。

由于10kV电力系统并联数字电抗器是通过改变数字电抗器的一次侧电流来改变系统的无功状态,所以使数字电抗器的一次侧电流等于通过计算得出的电流指令值便可达到系统调节目的。因此本文为了减小调节误差,采用电流滞环比较的方式来控制逆变器交流侧电流的输出。

如图6所示为本设计采用的滞环比较型PWM电流跟踪控制单相全桥式有源逆变电路原理图。根据该图所示控制过程如下:控制过程是把指令电流i1和实际一次侧电流i的偏差i1-i作为带有滞环特性的比较器的输入,通过其输出来控制功率器件VT1、VT2、VT3、VT4的通断。其中VT1、VT4和 VT2、VT3分别作为一对进行控制。设i的正方向如图所示,当i1>0时,若i 如图8所示为仿真系统仿真得出的PWM控制信号波形[6],上下两路控制信号互补。该图的上边PWM控制信号输出给逆变器开关器件VT1和VT4,控制VT1和VT4的开通与关断;下边的PWM控制信号输出给逆变器开关器件VT2和VT3,控制VT2和VT3的开通与关断。

2系统整体结构设计

21系统结构

如图9所示为10kV电力系统并联型数字电抗器系统结构图,本文通过10kV高压分压器采集电抗器一次侧两端电压信号;通过霍尔电流传感器采集电抗器一次侧电流信号;同时监测逆变器的直流侧电容两端电压信号。然后将系统采集的三路模拟信号传送到计算控制环节。其中计算控制环节包括指令电流计算环节、直流电压控制环节和补偿电流计算控制环节,经过一系列的计算和比较,得出PWM控制输出波形[7],通过隔离芯片输送到驱动模块,来驱动逆变器IGBT的开通与关断。

系统运行时,若因系统内容性无功过剩而需要增大感性无功时,控制系统中的CPU根据系统的实时状态分析计算出指令电流值,此时若想适量增加并联数字电抗器一次侧电流IL使其与指令电流值相等,在CPLD中比较产生PWM输出控制驱动模块使VT1和VT4导通,同时必须使VT2和VT3关断,逆变器输出交流电流I2,通过互感作用使得IL实际值达到指令电流值。

若当感性无功过剩时,需要减少系统内的感性无功,控制系统中的CPU根据系统的实时状态分析计算出指令电流值,此时若想适量减小电抗器一次侧电流IL使其与指令电流值相等,从而通过PWM控制VT2和VT3导通,需使VT1和VT4同时关断,逆变器输出交流电流-I2,通过互感作用让IL实际值接近指令电流值。

22硬件设计

控制器是数字式电抗器控制方面的核心部分,决定着数字电抗器感性电流的补偿性能,主要完成电抗器一次测电压、电流检测及基波提取、逆变器直流侧电容电压检测、补偿电流跟踪控制、直流侧电压控制等功能。本节将介绍基于高精度ADC、CPLD和DSP为主芯片结构的数字电抗器主控制器的硬件设计部分[8]。图10为整个控制器的结构图。

根据并联数字电抗器运行实时性的要求,采用DSP作为CPU与高精度ADC和CPLD相互配合,从而在每个周期输出500个计算电流数字值,同时产生2-5kHz的PWM调制信号输出到驱动电路。上述框图的整体工作过程为:CPLD控制A/D采样时间,接收经过信号调理电路、模数转换得到的采样数据,写到双口RAM的不同地址区域里;DSP根据CPLD发出的板选信号从双口RAM另一侧读出采样数据,计算需要输出的电流,即指令电流,该电流由逆变器直流侧稳压有功充电电流和感性无功补偿电流组成。再把指令电流写回双口RAM,在CPLD内将指令电流与实测并联电抗器一次侧电流进行比较,产生4路PWM信号,经隔离芯片ADUM3220并通过DB9屏蔽线与驱动器连接,发出+15V或-10V的驱动信号控制主电路中IGBT的开通与关断。同时若驱动模块发生故障时候,驱动模块将通过隔离芯片向CPLD发出故障信号,以使CPLD做出判断;若系统中出现诸如系统短路等故障时,通过4路开关输入电路传输到CPLD中进行处理,发出信号断开继电器,进行系统保护或者系统正常运行时,若需要断开某些设备,也可以通过CPLD发出信号断开继电器。

本文采用高精度的ADC芯片MAX1324与型号为EPM1270T144C5N的逻辑器件CPLD配合将模拟数据转换成数字数据。当控制系统需要对前端采集的模拟信号进行数模转换时,先由CPLD通过低8位数据通道发送8位数据对MAX1324进行通道选择,然后通过控制MAX1324使其对所选通道的模拟信号进行转换,得到对应的14位数字信号,然后再写入相应的CPLD寄存器里进行数据应用。

在工业设计中,为了防止外部电路产生短路等故障引起控制板毁坏,需要在控制器与外部电路之间做隔离保护,多数情况下采用电磁隔离或光电隔离[9]。考虑到驱动器对于输入信号延迟时间60ns的要求,因此本文在控制器和主电路驱动器之间采用电磁隔离,选用ADI公司ADUM3220隔离芯片,该芯片工作频率可以达到1MHz,输出端电压范围+45V~+18V,满足驱动器的输入要求。输入端逻辑电平+33V~+5V,可以与输出电平为+33V的CPLD直接连接。此隔离芯片具有两个输入通道,因此对于主电路4个IGBT产生的4路PWM驱动信号,只需要2个隔离芯片。

本设计选用了型号为FZ400R12KS4的IGBT作为逆变器的开关器件。为了使CPLD输出的PWM能够安全、稳定地驱动IGBT的开关,应在CPLD的PWM信号输出引脚与IGBT之间建立一套驱动电路。本设计所选IGBT为全桥开关且开通触发信号为+15V,关断触发信号为-10V。本文选用瑞士CONCEPT的2SC0435T2A0-17驱动模块,该模块具有以下特点:高集成双通道驱动模块;单通道门级驱动电流为±35A,驱动功率为4W;驱动信号为+15V/-10V;可驱动1200V或1700V IGBT模块;具有SCALE-2技术的驱动器。

3软件设计及系统仿真

数字式电抗器控制器的软件设计根据硬件电路的特点基于DSP+CPLD编程设计。主要分为两部分:系统电信号检测部分和运算控制部分。CPLD编程设计采用了Altera公司推出的Quartus_II 90 Web Edition集成开发环境,应用Verilog语言对控制部分进行编程;DSP的软件设计部分是应用TI公司推出的DSP的开发环境CCS33集成开发环境,编程采用C语言。

为了达到该10kV力系统数字电抗器调节的准确性和时间精度的要求,本文把一个周波正弦函数离散成500个相同时间间距的数组成的函数,由于数字电抗器运行在工频周期下,即一个周波函数的时间为002s。所以每个离散点运行需要的时间为40μs。因此本文可以设置DSP和CPLD的控制周期为40μs。要求CPLD和DSP的运行周期可以整除控制周期。由于控制器中时钟频率为25MHz的有源晶振为CPLD芯片提供时钟频率,因此CPLD在此控制器中的计数周期为40ns,即CPLD的计数器计数1000次完成一个数点的运行。本文DSP设置的主频为125MHz,即计数周期为8ns。本文编程时在CPLD程序中编写板选控制信号模块,将板选控制信号发给DSP以确定两者的通讯是否正常。从CPLD在“0”地址每隔20μs向DSP交替發出“1”和“0”信号,若DSP能读到板选控制信号,说明CPLD与DSP的通讯正常,这也是本设计保护的一部分。CPLD与DSP之间的地址和数据通过SRAM在每个板选控制周期进行一次并行数据通信。endprint

本控制系统中DSP主程序的功能主要是读取從CPLD经双口SRAM传过来的板选控制信号、三路采集信号、判断电压过零点、求出一个工频周波的电抗器一次侧电压、电流以及逆变器直流测电压的平均值,求出指令电流即感性补偿电流和逆变器直流侧稳压充电电流之和[13]。首先对DSP进行初始化,定义地址、固定参数等,设置计算用的标准正弦数组指针,每周期500个点中每个点的正弦函数值是通过MATLB仿真得到的,使之与电网电压波形同步。DSP的板选控制周期为40μs。初始化之后开始从SRAM读取数据的数字量并转换为采集的模拟信号实际值,然后判断电压的过零点,计算实时采集的工频周波内电压平均值、电流平均值、需要补偿的感性无功电流值和逆变器直流侧的有功稳压充电电流值,然后将计算出的感性无功电流值和有功稳压充电电流值按照实际规定方向求和得到指令电流值,最后将指令电流值通过SRAM以14位数据的形式传回到CPLD的寄存器中,与CPLD中的并联数字电控器一次侧实测电流值进行比较产生PWM调制信号。图11为主程序流程图。

数字电抗器控制系统中CPLD主程序的功能主要是完成A/D转换和PWM控制信号及其死区的产生[12]。程序中设置每8μs读取一次3个通道的ADC芯片的并行数字数据,然后通过SRAM传送到DSP里,DSP完成所需要的计算,得到指令电流值,将指令电流值通过SRAM传送给CPLD,接着CPLD通过将实时采集的数字电抗器一侧实测电流值和指令电流值进行比较得出PWM信号,做成死区模式,通过隔离芯片发送到驱动电路,最后驱动电路驱动逆变器IGBT的开通与关断。图12为CPLD程序流程图。

为了防止全桥逆变器每个桥的上下两个IGBT同时导通导致逆变桥短路引起IGBT及直流侧电容的烧坏乃至爆炸,在CPLD程序中通过比较指令电流和实测电流值得出的PWM调制信号需要做一个PWM死区使得逆变器每个全桥的上下两个IGBT不能同时导通但可以同时关断,这样就不会产生上面所提到的逆变桥短路现象。由于在CPLD中产生的PWM调制信号有明显的上升沿和下降沿,所以本文在编程时上升沿延迟4μs,即延迟IGBT开通4μs,下降无延迟,产生PWM死区,解决了逆变器由于单桥上下两个IGBT同时导通导致事故发生的问题。

4实验验证与分析

根据本文上述内容的阐述,在实验室内搭建实验平台验证电力系统并联数字电抗器设计理论[10]。由于实验室内电压等级达不到10kV,所以实验条件如下:电源单相相电压为220V,系统等效电感为自制导线电感为015mH,系统等效对地电容为电力电容器电容值为256μF,并联可调电抗器电感值为556mH。如图13为在CPU中显示的系统调试稳定的逆变器交流侧输出电流波形。

系统调试稳定的电压及电流波形显示,数字电抗器一次侧两端电压波形,为PWM脉宽波形,其幅值为逆变器直流侧电容电压稳定值,转换成近似正弦电压波形为有效值约为216V的交流电压值,达到了通过调试使电力线末端电压与首端电压近似相等的目的。

本文针对10kV电力系统内由于电力传输线分布电容产生的容性无功过剩导致电力传输线末端电压高于首端电压的现象,提出了可根据具体环境实时控制改变电感容量的并联数字电抗器。提出前端、后端电感线圈按电感容量3∶7串联,后者接有二次线圈用于电抗器总电感容量调节的结构。本文通过数字电抗器软件仿真,并搭建数字电抗器低压平台进行试验验证可得,新型数字电抗器调节效果良好,此结构设计具有控制方法比较简单,成本低廉的特点。

参 考 文 献:

[1]陈涛,高平,黄艳铃,等.低压配电网并联电容器无功补偿优化算法的研究[J].哈尔滨理工大学学报,2010,3(1):82-85

[2]崔俊霞.并联型有源电力滤波器谐波检测与控制方法的研究[D].燕山大学硕士学位论文,2010:30-33.

[3]沈宏伟,马仪等干式空心并联电抗器投入瞬态电动力研究[J]. 哈尔滨理工大学学报,2014,6(19):93-97

[4]郑征,张子伟,张朋 三相电压型PWM整流器不平衡控制策略的研究[J].电气传动,2014,44(5):26-29

[5]祝军10kV 5Mvar链式STATCOM装置的研发[D].哈尔滨理工大学硕士学位论文,2013:15-17

[6]王鹤霖,程启明,李明 基于不定频滞环空间矢量电流控制的三相PWM整流器仿真比较研究[D].华东电力,2014,42(6):1144-1149

[7]赵卓鹏,贾石峰电流滞环跟踪PWM 逆变器控制仿真研究[J].电气传动自动化,2011,33(2) :1-3

[8]三恒星科技TMS320C6713DSP原理与应用实例[M].北京:电子工业出版社2009:88-89

[9]徐德鸿.电力电子器件及其应用[M].北京:机械工业出版社,2010:50-150

[10]王学明并联电抗器在长电缆电力贯通线电容电流补偿中的应用[J].上海铁道科技,2010,1:122-124

[11]郑涛,赵彦杰 超/特高压可控并联电抗器关键技术综述[J].电力系统自动化,2014,38(7):127-135

[12]魏中夏 柔性交流输电技术(FACTS)在现代电力系统中的应用展望[J].电子测试,2013,21 (6): 283-284

[13]侯文清,张波,丘东元,等基于DSP的电能质量检测与无功补偿综合测控装置[J].仪器仪表学报,2007,28(1):120-127

(编辑:关毅)endprint