应用于并网逆变器的锁相环关键技术

宋杨呈祥

(国网冀北电力有限公司张家口供电公司,河北 张家口 075000)

应用于并网逆变器的锁相环关键技术

宋杨呈祥

(国网冀北电力有限公司张家口供电公司,河北 张家口 075000)

电网电压的相位和频率,是关系到并网逆变器控制信号参考值获取,保证并网逆变器系统平滑、可靠、稳定运行的重要信息。锁相环技术作为获取电网电压相位和频率的关键技术,是国内外学者研究、讨论的重点。根据不同性能的需要,国内外学者对锁相环技术做了大量研究,这些专门研究锁相环的文献相对复杂。首先对目前常用的单相同步坐标系锁相环正交信号的生成和单相锁相环谐波的剔除加以介绍;由于三相锁相环一些技术和单相锁相环相同,对目前常用的3种三相锁相环进行简要介绍。最后指出:鉴相器算法的提高和如何剔除谐波干扰,是未来的锁相环(phase-locked loop,PLL)技术发展最为关键的2个方面。

锁相环;并网逆变器;同步坐标系;正交信号;滤波

0 引言

1932年,法国工程师De Bellescize实现了第一个实际意义的锁相环(phase-locked loop,PLL),PLL开始广泛应用于工业和民用电器中[1-2]。进入21世纪,随着资源、环境问题的日益加剧,以太阳能、风能和热电联产等为代表的可再生、清洁能源纷纷通过逆变器以分布式电源的形式并入电网。电网电压的相位、频率是保证分布式电源并网系统可靠运行而必须获得的重要参数。准确及时的电网电压相位和频率信息,不仅可用来计算并网运行时控制信号的参考值,也可以在并网/孤岛切换过程中用来减少对电网的冲击作用。PLL作为一种闭环反馈控制系统,以其可以在一定范围内良好地使输出相位和频率跟踪输入信号而被广泛地应用在并网逆变器

控制系统中。在实际运行的电网中,不可避免地存在谐波、电压跌落等各种情况。PLL运行在这些情况下,必须拥有良好的鲁棒性以保证输出信号和电网电压同步[3]。现有文献大多局限于对某一流行的PLL进行研究论述,如文献[4-5];或对几种现今较为新颖的PLL进行性能上的比较,如文献[6]。本文着重介绍并网逆变器PLL的共性技术,对现在分布式并网系统中广泛应用的同步坐标系锁相环(synchronous reference frame PLL,SRF-PLL)的正交信号生成进行介绍;以基本PLL模型为例,综述PLL设计中的谐波滤除技术;最后,对3种成熟的三相并网逆变器PLL加以介绍。

1 基本PLL的结构和原理

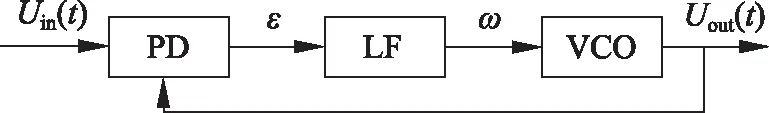

PLL电路由鉴相器(phase detector,PD)、环路滤波器(loop filter,LF)和压控振荡器(voltage-controlled oscillator,VCO)3大基本部分组成,如图1所示。

图1 PLL电路的构成Fig.1 Circuit structure of PLL

其中:Uin(t)为输入的待锁相电压;Uout(t)为锁相过程中由压控振荡器生成的、Uin(t)对应的输出电压;ε为Uin(t)和Uout(t)的相位差;ω为经锁相环生成的Uin(t)的角频率。鉴相器用于检测出两个输入信号的相位差。环路滤波器将鉴相器输出的含有纹波的直流信号变换为交流成分少的直流信号,并作为压控振荡器的驱动信号。压控振荡器是一种可变频率振荡器,用环路滤波器产生的直流信号控制振荡频率。最基本的基于乘法鉴相法的PLL如图2所示。

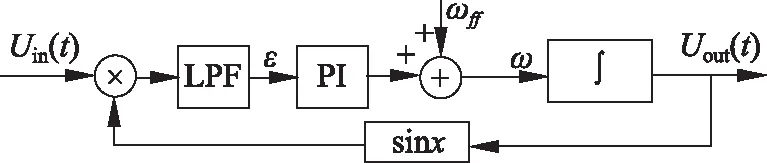

图2 基本PLL结构框图Fig.2 Structure diagram of basic PLL

其中:ωff为给定的参考角频率;PI为比例积分控制器(proportional-integral controller,PI)。其鉴相原理可以概括为

(1)

基于乘法鉴相法的PLL,实质是通过构造两个正交变量输入乘法器,并通过控制使乘法器输出ε为0来完成锁相的。这种锁相法虽然简单,但不能同时在动态响应速度和应对电网谐波上完全兼顾,且不能得到电网电压的幅值信息。现在广泛应用的单相SRF-PLL,则主要通过算法构造出正交于输入信号Uα的另一信号Uβ,以这两个信号作为虚拟两相输入,采用同步旋转坐标锁定原理完成锁相,如图3所示。

图3 单相SRF-PLL结构框图Fig.3 Structure diagram of single-phase SRF-PLL

其中:uq、ud分别为Uin(t)在dq坐标系下的q轴分量和d轴分量;Uα、Uβ分别为Uin(t)在αβ坐标系下的α轴分量和β轴分量。同步旋转坐标锁定原理中,经过Park变换得到的旋转坐标下的Uq、Ud和虚拟两相Uα、Uβ,有下式成立:

(2)

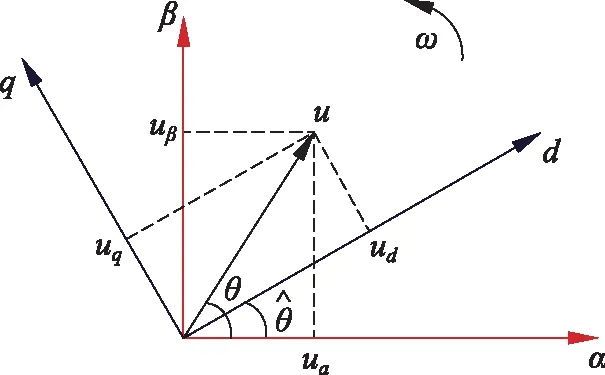

αβ-dq坐标变换可由图4所示向量图表示。

图4 αβ -dq坐标变换Fig.4 Coordinate transformation ofαβ -dq

其中:d、q分别为dq坐标系的d坐标轴和q坐标轴;α、β分别为αβ坐标系的α坐标轴和β坐标轴。使dq坐标系下的d轴和电网电压向量完全重合,则有Ud等于电网电压幅值,Uq为0。

2 正交信号的生成算法

显然在单相SRF-PLL设计中,关键在于生成和输入信号Uα正交的虚拟信号Uβ。正交信号的生成算法有许多,其中最为简单的是基于延迟法的SRF-PLL。基于延迟法正交信号的获得,是通过将输入信号延迟T/4即90°,来获得正交信号的。在实际电网中,由于频率会发生变化而延迟的T/4却不变,因而这种方法动态性能很差。另一种基于微分法的SRF-PLL虽然简单,但也存在乘法鉴相法的不足[7]。由于上述2种方法缺陷明显,且在并网逆变器系统中很少使用,本文主要对下述3种方法进行介绍。

2.1 基于Park反变换的正交信号生成

Park反变换完成αβ-dq的坐标变换:

(3)

图5为基于Park反变换的SRF-PLL结构图,Park变换和Park反变换的输出分别相互作为对方的输入,从而形成了2个相互依存的非线性闭环。在图5所示的2个变换的dq信号间,加入1对一阶低通滤波器(low pass filter,LPF),提高了系统的稳定性[7]。

图5 基于Park反变换的PLL结构图Fig.5 Structure diagram of PLL based inverse Park transformation

2.2 基于2阶广义积分的正交信号生成

通过构建图6所示基于2阶广义积分(second order generalized integrator,SOGI)的自适应滤波器来实现正交信号的获得,就是基于2阶广义积分SRF-PLL的基本原理。由于结构中构建了自适应滤波器,这种方法不仅可实现对输入信号的90°相角偏移,而且还可滤除高次谐波。图6所示的自适应滤波器具有如下传递函数,由1对积分器构成。

(4)

图6 基于2阶广义积分的自适应滤波器Fig.6 Adaptive filter based on SOGI

(5)

(6)

式中:增益k可用来调节滤波能力;q为90°的相位偏移因子。

2.3 基于Hilbert变换的正交信号生成

相对于前面2种正交信号的生成方法,基于Hilbert变换来获得正交信号的方法不太常见。这种方法,将输入信号通过如下Hilbert变换,直接得到正交信号。

(7)

式中p为柯西主值。式(7)所示的理想Hilbert变换,容易导致设计的PLL成为非因果系统[8]。因而在实际应用中,常采用系数h[n]定义为下式的有限脉冲响应滤波器(finite impulse response filter,FIR),来完成Hilbert变换的功能。

(8)

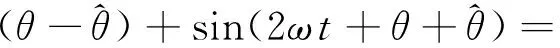

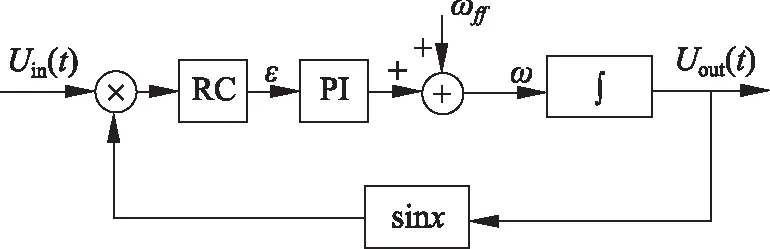

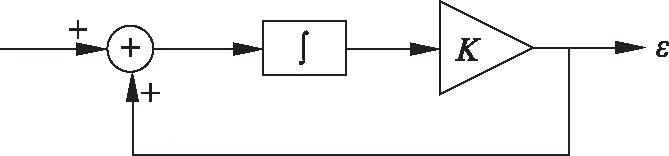

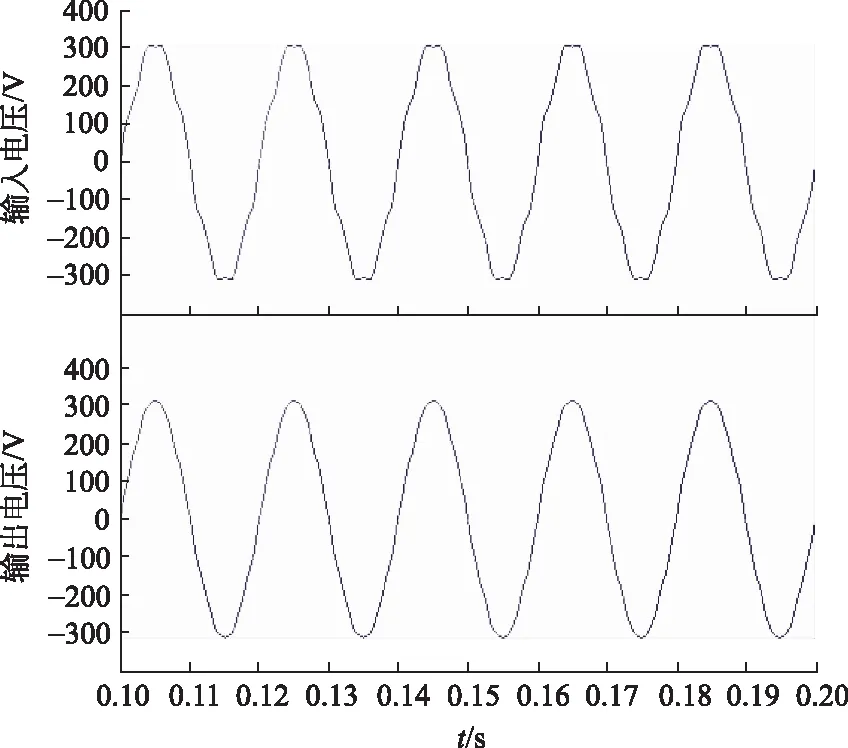

式中N为FIR的阶数,n、N取自然数,且0 鉴相器用于检测锁得的输出信号与输入信号的相位差,是后续工作的基础,也是构成PLL最为重要的一部分。鉴相过程中面临的最重要问题,就是如何剔除谐波的干扰。消弱谐波的干扰可以通过2种机制完成: 1)通过合理设计降低鉴相过程对谐波干扰的敏感程度,如第2节中的其他正交生成方法对谐波的敏感程度都要低于基于延时法SRF-PLL; 2)附加滤波环节滤除部分或全部谐波。本文主要介绍后一种方法。由于具体的环路滤波器设计需要大量细致的论述,本文仅以单相基本乘法鉴相PLL对各种滤波方法及其特点做一简介。这之前,注意到图2所示的基本乘法鉴相PLL天然有下式成立: (9) 式中:A为电网相电压幅值;k为鉴相增益。当考虑到锁得的输出信号和输入信号误差很小时,式(9)等号右侧括号中可以有下式成立: (10) 显然经鉴相后,存在二次谐波分量,需要被滤除。实际并网逆变器系统PLL设计中,常在图2所示的PI控制器前加滤波环节,下文对常用的滤波环节加以简介。 3.1 低通滤波器 当滤波环节设计为图7所示的LPF,滤波环节具有如下传递函数: 图7 低通滤波器滤除谐波Fig.7 LPF technique for harmonics rejection (11) 式中fc为滤波器截止频率。采用LPF后,PLL的跟踪精度明显提高,但动态响应速度变慢。LPF的加入引起了信号相位的偏移;当输入信号频率变化时,滤波效果将受到一定影响。 3.2 谐振滤波器 当滤波环节设计为图8所示的谐振滤波器(resonant filter,RF),滤波环节具有如下传递函数: (12) 式中kf决定带宽。采用谐振滤波器,将获得比低通滤波器更好的系统稳定性,同时也可以保持良好的谐波滤除效果。信号经过谐振滤波器时,谐振频率分量将不会发生相位偏移,而其他频率分量将会偏移±90°。 图8 谐振滤波器滤除谐波Fig.8 RF technique for harmonics rejection 3.3 滑动平均滤波器 当滤波环节设计为图9所示的滑动平均滤波器(moving average filter,MAF),滤波环节具有如下通用信号处理能力: (13) 图9 滑动平均滤波器滤除谐波Fig.9 MAF technique for harmonics rejection 当输入信号含有的谐波分量频率正好都是MAF等效频率的整数倍时,MAF可以将输出稳定为一个固定的常数。通过合理设计Tω,MAF可以表现出低通滤波器的性质,MAF对谐波的传递函数为 (14) 3.4 重复控制器 最后介绍滤波环节设计为图10所示重复控制器(repetitive controller,RC)的情况,这种方法可大大减少二次谐波对PI控制器的作用。RC实际表现为带通滤波器的性质,可有效滤除齐次谐波,甚至将其完全滤除。通过增加RC滤除谐波,可理解为等效增加了PI控制器的比例环节增益。 图10 重复控制器滤除谐波Fig.10 RC technique for harmonics rejection 图11是一种常用的基于离散傅里叶变换(discrete Fourier transform,DFT)的RC模型,DFT的离散传递函数为 (15) 式(15)其实也就是N阶有限单位冲击响应滤波器的作用函数方程。 图11 重复控制器结构图Fig.11 Structure diagram of RC 三相SRF-PLL如图12所示,其基本构成和单相SRF-PLL基本相同。同样通过Park变换从αβ静止坐标系变换到dq旋转坐标系,q轴分量通过闭环控制为0,d轴分量反应电压向量幅值。不同之处在于,在Park变换前存在abc/αβ变换: (16) 图12 三相SRF-PLLFig.12 Three-phase SRF-PLL 评价三相SRF-PLL的性能指标,主要有锁相精度和动态响应速度两方面。这二者是相互矛盾的,在PLL内部参数设计时往往需要在二者间进行权衡。同单相SRF-PLL一样,三相SRF-PLL在输入信号存在谐波时输出信号质量也很差,需要采取滤波措施,这和单相PLL没有本质区别。图12中,ua、ub、uc为对应的abc三相待锁相电压。 图13 双广义2阶积分PLLFig.13 Dual SOGI-PLL 增强型锁相环(enhanched PLL,EPLL)在鉴相环节采用具有更好滤波能力的算法,其实际上是自适应陷波滤波器(adaptative notch filter,ANF)和传统PLL结合的产物。EPLL最大的特点是通过该算法可估算出基波分量,同时也可给出输入信号幅值等其他信息。图14为组成三相EPLL的单相EPLL,无需额外的正交生成就可产生正交于输入的信号。 图14 单相EPLLFig.14 Single-phase EPLL 图15 三相EPLLFig.15 Three-phase EPLL (17) 基于PSCAD搭建图12的SRF-PLL、图13所示的DSOGI-PLL和图15的EPLL模型。考虑5次和7次谐波(THD为12%),仿真分别得到的a相输入、输出信号对比如图16—18所示。3种PLL谐波滤除能力的定量比较,则在表1中列出。可见:SRF-PLL没有滤波效果,而EPLL的滤波效果远远好于DSOGI-PLL。 图16 SRF-PLL滤波能力Fig.16 SRF-PLL’s filtering capability 图17 DSOGI-PLL滤波能力Fig.17 DSOGI-PLL’s filtering capability 图18 EPLL滤波能力Fig.18 EPLL’s filtering capability PLL类型输入信号THD/%输出信号THD/%SRF-PLL12.0312.03DSOGI-PLL12.034.40EPLL12.030.28 PLL技术是一门比较系统的科学,本文主要对 现今最常用的并网逆变器系统PLL关键技术进行了介绍。PLL技术最关键的两方面:一是鉴相器算法的设计;一是如何剔除谐波的干扰。国内外介绍各种不同PLL的文献,都基本围绕这两方面内容进行探讨;同时,这两方面也是今后PLL仍需要研究改进的地方。 [1] BEST R E. 锁相环设计、 仿真与应用[M]. 5版. 李永明, 王海永, 肖珺, 等译. 北京: 清华大学出版社, 2007. [2] 远坂俊昭. 锁相环(PLL)电路设计与应用[M]. 何希才, 译. 北京: 科学出版社, 2006. [3] MEERSMAN B, DE KOONING J, VANDOORN T, et al. Overview of PLL methods for distributed generation units[C]//45th International Universities Power Engineering Conference(UPEC). Cardiff, Wales: IEEE, 2010: 1-6. [4] SHI Lisheng, CROW M L. A novel PLL system based on adaptive resonant filter[C]//40th North American Power Symposium(NAPS). Calgary, AB: IEEE, 2008: 1-8. [5] YAZDANI D, PAHLEVANINEZHAD M, BAKHSHAI A. Three-phase grid synchronization techniques for grid connected converters in distributed generation systems[C]//IEEE International Symposium on Industrial Electronics. Seoul, Korea: IEEE, 2009: 1105-1110. [6] GAO Siyu, BARNES M. Phase-locked loop for AC systems: analyses and comparisons[C]//6th IET International Conference on Power Electronics, Machines and Drives(PEMD). Bristol, English: IEEE, 2012: 1-6. [7] 张兴, 张崇巍. PWM整流器及其控制[M]. 北京: 机械工业出版社, 2012. [8] SILVA S M, LOPES B M, FILHO B J C. Performance evaluation of PLL algorithms for single phase grid-connected systems[C]//39th IAS Annual Industry Applications Conference. Seattle, America: IEEE, 2004: 2259-2263. 宋杨呈祥 (编辑 谷子) Key PLL Techniques for Grid-Connected Power Inverters SONG Yangchengxiang (Zhangjiakou Power Supply Company of State Grid Jibei Electric Power Company, Zhangjiakou 075000, Hebei Province, China) The phase and frequency of grid voltage determine the reference value of control signal of grid-connected inverter system, and ensure smooth, reliable and stable operation of the system. As the key technique obtaining the phase and frequency of grid voltage, phase-locked loop (PLL) techniques gain the attention of scholars at home and abroad. According to different properties, studies on PLL techniques are various, while literature on specialized PLL design is relatively complex. Firstly, we introduce the generation of quadrature signals of single-phase synchronous reference frame PLL and the rejection of harmonic for single-phase PLL. Because some technologies of three-phase PLL are the same with single-phase PLL, the introduction of three commonly used three-phase PLLs is given. Finally, two most critical aspects are proposed for the future development of PLL technology, including the enhancement of phase detector algorithm and the method of eliminating harmonic interference. phase-locked loop(PLL); grid-connected inverters; synchronous reference frame(SRF); quadrature signal; filter TK 01;TM 71 A 2096-2185(2017)03-0033-06 10.16513/j.cnki.10-1427/tk.2017.03.006 2017-05-05 宋杨呈祥(1987—),男,助理工程师,主要研究配电网规划、高压直流输电、交直流混联系统相关问题,songyangchengxiang@163.com。3 谐波的滤除

4 三相PLL技术

5 结论