一种加速DRAM灵敏放大器的设计方法

段会福,付 妮,拜福君,蒋 强,李 进

(西安紫光国芯半导体有限公司,陕西 西安 710075)

一种加速DRAM灵敏放大器的设计方法

段会福,付 妮,拜福君,蒋 强,李 进

(西安紫光国芯半导体有限公司,陕西 西安 710075)

文章设计了一种DRAM中的灵敏放大器,通过增加一个过充电压开关,一个过充电压工作时间脉冲控制电路,一个发生器电路,使得灵敏放大器的放大速度有效提升,从而改善了DRAM的性能指标参数tRCD,提高了DRAM的性能。这种方法通过很小的代价,实现了灵敏放大器放大速度的改进。电路易于控制,版图面积增加很小,功耗无需增加,是一种提高灵敏放大器性能的有效方法。

DRAM灵敏放大器;tRCD过充电压;脉冲控制电路;信号建立时间

动态随机存储器(Dynamic Random Access Memory,DRAM)在集成电路领域有着广泛的应用。从ACTIVE命令到READ命令的最小时间tRCD是其重要的时序参数指标,表征了ACTIVE命令后,可以最快发READ命令的延时,在这段时间内,ACTIVE命令必须将存储单元的数据读取到位线上,然后通过灵敏放大器将位线电压放大到足够的摆幅,以等待READ命令能正确地将为线上的数据读出。灵敏放大器的放大时间是tRCD的重要组成部分,改善灵敏放大器的性能,即加快灵敏放大器的放大速度是改善tRCD参数的有效方法。

如何加快灵敏放大器的放大速度?增加灵敏放大器开始工作时的位线与参考位线之间的电压差?这种方法能有效地加快灵敏放大器的放大速度,但是增加位线与参考位线之间的电压差,一种方法是增加DRAM存储单元的电容,另一种方法是增加信号建立时间(字线打开到灵敏放大器开始工作的时间),前者在工艺上很难实现,后者虽然改进了灵敏放大器的放大速度,但是信号建立时间也是tRCD的组成部分,反而会使得tRCD增加。减少位线的负载?也就是减少位线连接的存储单元的数目。这种方法也能有效地加快灵敏放大器的放大速度,但是位线负载的减少就意味着灵敏放大器数目的增多,使得芯片面积大大增加,从而增加了DRAM芯片的成本。

针对上述技术难点,本文提出了一种加速DRAM灵敏放大器放大时间的设计方法,该方法既能显著地加快灵敏放大器的放大速度,又不会增加芯片面积及功耗,是改善DRAM tRCD的有效方法。

1 DRAM灵敏放大器电路及工作原理

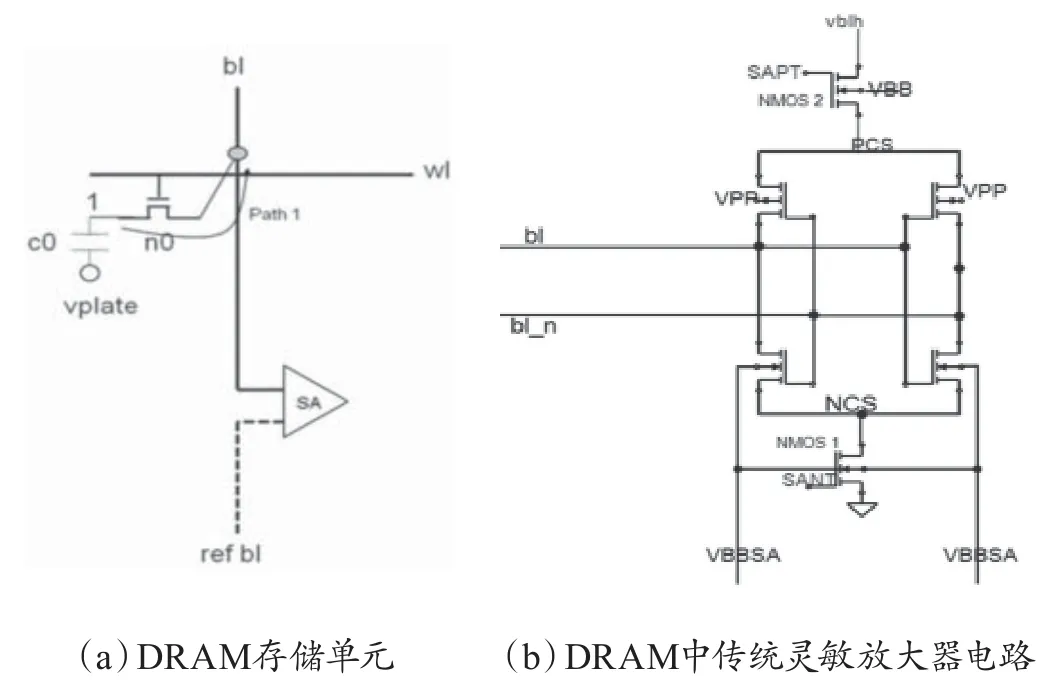

动态存储器存储单元是由一个晶体管,一个电容构成,数据存储在电容上,如图1(a)所示,激活操作(ACTIVE)原理如下:激活操作前,字线电压为低,位线及参考位线电压为一个中间电压,假设存储单元存储的值为“1”,其电压一般为位线上中间电压的两倍,激活操作后,经过地址译码,字线被选中电压升高,这时晶体管N0导通,因为电容上极板电压高于位线电压,所以电容C0上的电荷流向位线,位线电压逐渐升高,这样位线跟参考位线之间的电压差会越来越大。当这个电压差足够大时,灵敏放大器被开启,位线和参考位线被灵敏放大器放大成全摆幅,从字线开启到灵敏放大器开始工作这段时间被称作信号建立时间(signal develop time)。图1(b)为传统灵敏放大器电路,当位线与参考位线电压差达到一定程度时,首先SANT信号升高,ncs降低至vss电压,SAPT升高,pcs升高至vblh电压,通过锁存器,位线被下拉,参考位线被上拉,从而实现放大功能,图2为灵敏放大器工作波形。Vblh的电压值很大地影响着灵敏放大器的放大速度,vblh越高放大速度越快,vblh越低,放大速度越慢,但是vblh的电压不能升高,因为升高会使得存储单元的可靠性出现问题。

图1 DRAM存储单元及传统灵敏放大器的电路

图2 传统 DRAM灵敏放大器工作波形

2 采用过充电压的灵敏放大器电路

如图3(a)所示,在灵敏放大器中增加一个开关,增加一个比vblh电压值高的过充电压vod,当灵敏放大器开始工作时,SAP1T升高,SANT升高,开关NMOS1和NMOS3首先打开,pcs被充至vod,ncs被拉至vss,通过inv1和inv2构成的锁存器,位线被迅速上拉,参考位线被迅速下拉,当位线被上拉至稍微高于vblh时,开关NMOS3关闭,开关NMOS2打开,位线被重新拉回vblh。灵敏放大器利用过充电压vod快速放大位线,放大到足够程度后切换到vblh电压,从而实现了灵敏放大器放大速度的加快。图3(b)为灵敏放大器工作波形。SAP1T为一个脉冲,只工作一段时间,所以需要增加一个脉冲产生电路来产生SAP1T信号。SAP1T的脉冲宽度非常重要,脉冲过宽会使得位线过充过多,首先会增加功耗,其次如果vblh泄放电路泄放能力不足会导致位线电压无法拉回到vblh,SAP1T宽度最好控制在恰好将位线完全充至vblh电压。同时由于vod这个电压的增加,需要增加一个generator电路来产生vod电压。脉冲产生电路和generator电路只需要很小的版图面积。

图3 灵敏放大器电路图及工作波形

3 仿真结果

采用38 nm DRAM电路,Vblh=1.1 V,Vod=1.3 V,Vbleq=0.55 V,灵敏放大器开始工作时位线与参考位线电压差delta V为100 mV。如图所示,本文所设计灵敏放大器开始工作时,SAP1T升高,SANT升高,开关NMOS3和NMOS1首先打开,pcs被充至Vod,ncs被拉至Vss,通过in V1和in V2构成的锁存器,位线被迅速上拉,参考位线被迅速下拉,当位线被上拉至稍微高于Vblh时,开关NMOS3关闭,开关NMOS2打开,位线被重新拉回Vblh。图4(a)所示为仿真波形中位线和参考位线波形,本文所设计灵敏放大器位线上拉明显加快;图4(b)所示为位线电压—参考位线电压波形图,以位线电压—参考位线电压=60%×Vblh为标准,本文设计灵敏放大器电路放大速度比传统灵敏放大器增快了398 ps。

图4 仿真波形对比

4 结语

本文设计了一种DRAM灵敏放大器电路,通过增加一个过充电压开关,一个过充电压工作时间脉冲控制电路,一个generator电路,使得灵敏放大器的放大速度有效提升,从而改善了DRAM的性能指标参数tRCD,提高了DRAM的性能。这种方法通过很小的代价,实现了灵敏放大器放大速度的改进,电路易于控制,版图面积增加很小,功耗无需增加,是一种提高灵敏放大器性能的有效方法。

[1]KURT H. System integration from transistor design to large scale integrated circuits[M]. USA:Science Press House, 2004.

[2]段会福.一种加速DRAM灵敏放大器的方法[P].版权号:CN 103971728A,2014.

[3]JAN M.Rabaey digital integrated circuits[J].Digital Integrated Circuits, 1969(7):249-252.

A design to speed up sense ampli fi er in DRAM

Duan Huifu, Fu Ni, Bai Fujun, Jiang Qiang, Li Jin

(Xi’an UniIC Semiconductors Co., Ltd., Xi’an 710075, China)

A sense ampli fi er of DRAM is designed in this paper, by adding an over drive voltage switch, an over drive voltage working time pulse control circuit and a generator to effectively improve the zoom speed of sense ampli fi er, thus the performance index parameter tRCD of DRAM is improved and so does the DRAM. This method improves the zoom speed of a sense amplifier at a low cost. The circuit is easy to control, increase of the layout area is very small, without increasing the power consumption, which is an effective way to improve the performance of the sense ampli fi er.

DRAM sense ampli fi er; tRCD over drive voltage; pulse control circuit; signal development time

段会福(1982— ),男,山东日照,硕士,工程师;研究方向:存储单元阵列设计。