基于Systenl Generator的流体力学算法建模及仿真

韩伟+谢建春

摘要:为了提高流体力学算法EULER3D程序的性能,提出了一种基于System Generator的软硬件结合的优化方法。在分析算法流程和耗时函数的基础上,用System Generator模块搭建系统模型,实现EULER3D的核心计算功能,并进行仿真。利用高速以太网接口实现PC和FPGA之间的数据交互,最终实现了EULER3D程序的整体性能优化。将实验结果与直接编写VHDL代码开发方法比较,结果表明,使用System Generator能够降低FPGA编程要求,提高开发效率。

关键词:System Generator;FPGA;模型化設计;流体力学;性能优化

随着FPGA的高速发展,FPGA中的可用资源不断增加,集成了多种用于数字信号处理的IP核。为了适应这种发展趋势,各FPGA厂商都推出了基于Matlab接口的代码自动生成工具,Xilinx公司的System Generator就是其中的一个代表。它是一种系统级(或算法级)的设计工具,在Matlab/Simulink提供的高层运行环境中对所需的硬件进行图形化建模,利用可以自动转化成所需的VHDL或Verilog语言的基本模块组件大型系统,提高开发效率。由System Generator构建的模型可用Simulink进行仿真和调试,算法模型的修改方便,时序设计简单。在不降低执行效率和可靠性的情况下,使得FPGA不仅具有硬件级的运行速度,又表现出软件的易重构性。FPGA上的一定规模的系统设计可以借助System Generator等工具提高开发效率,在模糊控制器、直接数字频率合成器和信号滤波器等诸多设计中得到应用,取得了良好的效果。

对于某些并行计算软件而言,CPU、GPU的并行计算能力有限,而FPGA则能够提供更好的并行计算支持。通过运用软硬件结合的方法,将软件中计算量集中的核心代码移植到FP-GA上由硬件实现,以期获得更快的程序执行速度。

本文分析了流体力学算法EULER3D的算法流程和核心运算,在不同层次上建立算法模型,利用System Generator工具进行仿真并在FPGA上实现,算法其他部分在PC机上进行计算,这样以软硬件结合的方式提高了程序的执行效率。通过与手工编写VHDL代码的开发方法进行对比,可以反映出SystemGenerator工具在开发周期、资源利用等方面的优势。

1EULER3D算法简介

1.1算法原理

EULER3D算法是流体力学计算的一个重要的步骤,计算非均匀流场中质元的密度、速度和能量的变化情况。相关的数值算法公式为

其中,u=(u,v,w)是流体速度,T是温度,p是压强,是热膨胀因子,g是重力场,是热扩散性。

每隔时间计算每个质元在4个“相邻质元”的作用下发生状态变化,“相邻质元”可以是真实的质元,也可以是机翼边界或者远场边界。该算法分为以下几个计算步骤:初始化;读入数据,填充空位;备份数据;计算时间步长;计算流场变化;更新流场数据;输出计算结果。算法流程如图1所示。

1.2程序热点分析

本文针对EULER3D的多核CPU C语言版本(https://github.com/pathseale/rodinia/blob/master/cuda/cfd/euler3d.cu)进行优化。利用gprof工具分析程序中各函数的调用次数和耗时比例,对40万质元运算量的一次分析结果如图2所示。由图2可见,程序运行时调用次数较多的函数有compute_flux函数、time_step函数、compute_velocity函数、compute_speed_sqd函数等。compute_velocity及其子函数包含了大量的浮点数乘法、除法和开方运算,耗时比重达到了总运行时间的八成以上,因此compute_velocity函数可以考虑作为利用硬件加速和优化的对象。

2基于System Generator的EULER3D算法的建模

System Generator是Xilinx公司和MathWorks公司联合开发的基于FPGA的建模和设计工具。它可以将算法表示成为一个高度抽象的模块,自动将算法模型映射为一个基于FPGA的硬件设计方案。设计者不必清楚硬件描述语言,而关注于算法模型就可以完成硬件设计,另一方面,System Generator根据算法模型自动生成测试文件,这使得仿真更加方便。这样就将开发时间主要用于算法模型的设计上,节约了编码和调试时间。

根据程序热点分析结果,将compute_flux函数用硬件实现有望很好地提高算法的整体效率。compute_flux调用的子函数有compute_velocity、compute_speed_sqd、compute_pressure、corn-pute_speed_of_sound和compute_flux_contribution。采用自底向上的建模过程,先构建compute_velocity等的模型,生成子系统,再利用这些子系统构建出compute_flux模型。

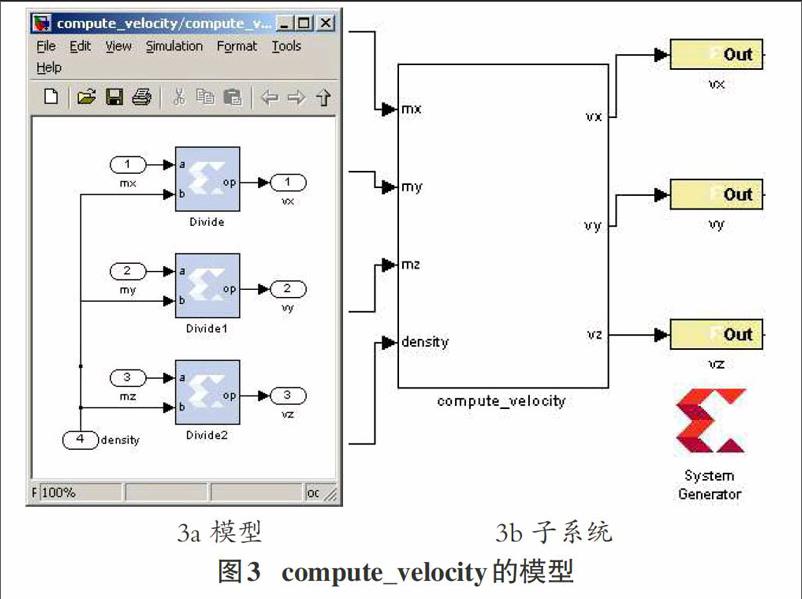

2.1底层模型

对compute_velocity等底层函数建模,涉及的基本运算有加、减、乘、除和开方运算,它们都可以直接对应到svstem Gen-erator的Xilinx Blockset工具箱中的5种基本运算模块。构建底层模型之后,可以生成对应的子系统(如compute_velocity.mdl),便于上层引用。构建compute_velocity函数的模型及其对应的子系统,如图3所示。注意这里使用的基本模块均来自Xilinx Blockset工具箱。在compute_velocity函数内作了3次除法,外部表现为4个输入和3个输出。其他底层模型有com-pute_flux_contribution、compute_pressure、compute_speed_of_sound、compute_speed_sqd,建立方式与compute_velocity类似。

2.2顶层模型

在底层函数模型的基础上,建立con-pute_flux函数的模型,即顶层模型。con-pute_flux含有循环体和内存索引结构(大型数组),为在FPGA上实现,需要将遍历质元邻居的循环体展开,并去除索引结构,这里假定索引结果是可以直接获得的。除此之外,判断相邻质元类型的分支语句需要对应到system Generator的Switch模块上。构建的顶层模型如图4所示。其中Neighbor1~4是对4重循环的展开,计算一个质元受邻居质元的作用,Add模块再将速度和质量的变化合成起来。两个Delay模块实现了串行数据和并行数据之间的转换。

图4中的Neighbor算子调用了底层模型,其数据流示意图如图5所示。这里利用两个质元的状态及粘度经验值(nor-mals)计算出流量的变化。Neighbor算子之间的并行计算可以提高算法效率。

3实验仿真与效率分析

3.1实验平台

本文实验采用FPGA软件/硬件协同设计的方式,实验平台由PC和FPGA组成,FPGA为Kintex7 xc7k160t。PC运行EULER3D程序直到compute_flux函数,将相关数据发送到FP-GA片上系统。片上系统对数据进行相关计算后,再把计算结果传送回PC,以进行后续计算。PC机和FPGA之间通过千兆以太网口进行数据传输。

3.2仿真结果

在System Generator中设定目标板及时钟等选项,应用自动生成的testbench测试文件,system Generator系统模型能够在Simulink环境下完成系统仿真验证。对开发的底层模型和顶层模型先后进行仿真,验证算法模型的正确性。其中,com-pute_velocity的仿真结果如图6所示。该模块内有3个浮点除法运算,由仿真输出可知计算的结果是正确的。

为了验证应用System Generator设计出来的算法模型输出结果的正确性和精确性,使用Simulink与System Generator并行地搭建了上述讨论的EULER3D算法模型,并要求两者的结果误差不超过千分之一。System Generator系统参量设置如下:系统的采样率为100MHz,FPGA时钟频率为10ns,仿真时间为20μs。在仿真环境相同的情况下,100组仿真数据都显示误差不超过千分之一,满足设计要求。

仿真结果正确后,生成VHDL代码,在Xilinx ISE中综合和实现,最后下载到FPGA中。FPGA上时钟频率为100MHz,compute_flux运算需要240个时钟周期,加上数据传输耗时,实际上一次运算需要2.8μs。相比于单独在3.0GHz双核处理器的PC上运行的4μs,局部加速比达到了4/2.8=1.43。程序的整体运行时间节约了16%左右。

3.3效率分析

为了分析基于System Generator的开发效率,采用直接编写VHDL代码的方式实现compute_flux函数,实现相同的功能。比较两种方法的开发时间、资源使用率和程序执行时间,比较结果见下表1。从表1中可以看出,基于SystemGenerator的开发方法节约了13%的开发时间,资源利用率较低,程序执行时间基本相同。另外,两种的计算精度是一致的。由此可见,Sys-tem Generator在保证资源利用率和執行时间的基础上提高了开发效率,降低了对开发人员的要求。

4结束语

本文介绍了在System Generator环境下建立模型实现EUL-ER3D算法的方法,经过仿真和生成VHDL代码的过程,在FP-GA和PC上快速、高效地实现了该软件算法,相比于PC机,处理速度有明显提高。本文模块化的设计简化了设计流程,使得模型易于修改。通过与手工编码对比发现,利用System Gener-ator开发快速而高效,使得FPGA在并行算法开发和实现方面具有较好的效果和更多的优势。