基于NAND Flash的存储设备设计与实现

潘旭明,刘嵩岩,齐可心,吴尚儒,陈 婷

(黑龙江大学 电子工程学院,黑龙江 哈尔滨 150080)

基于NAND Flash的存储设备设计与实现

潘旭明,刘嵩岩,齐可心,吴尚儒,陈 婷

(黑龙江大学 电子工程学院,黑龙江 哈尔滨 150080)

Flash是目前最火的存储介质,具有传输速度快、功耗小、无噪音等优点。但用于存储设备时常因片上总线的局限而性能低下。针对因总线限制Flash性能发挥的问题,设计了一种基于AXI总线的NAND Flash存储设备,所设计的存储设备具有多通道传输、流水线操作、ECC校验,以及RAID5架构存储等功能。设计分析与测试结果表明,设计的基于NAND Flash存储系统传输速度更快,系统更稳定,同时增强了存储数据的可靠性为NAND Flash存储设备的研究提供了一个新的解决方案。

AXI总线;SSD存储;DMA;NAND Flash

0 引言

随着科技的快速发展,存储行业也发生了很大的变化,固态硬盘(简称固盘),因其传输速度快、无噪音、功耗小等优点,迅速占领了大量存储设备的市场,即将成为当今主流存储介质的不二人选。固态硬盘通常具有很快的传输速度,但设计成存储设备时常因为片上总线的传输限制而发挥不出应有的传输性能。搭配怎样的片上总线能把SSD性能更好地发挥出来,这已成为设计SSD存储设备应考虑的重要问题。

基于这种情况,人们着手研究SSD的原理与特性以及各类总线的原理和特性,并且在不断突破创新。目前,此项研究在国内外已经取得了很大的成果。文献[1]中,作者根据PCIE总线和SSD的特点,设计出一种基于PCIE的固态硬盘嵌入式存储系统;文献[2]中作者将SSD与PCIE总线相结合,提出了基于PCIE总线的SSD标准化准则;文献[3]作者及其团队将SSD设备与AHB总线结合在了一起,并提出一种8通道传输机制来提高其传输速度。

设计了一款基于AXI总线的SSD存储模块,将AXI总线的性能与SSD更好地结合在了一起,模块主要由产生并发送实验数据的下载板和接收数据的SSD电子盘2部分组成。

1 基于NAND Flash存储设备的技术分析

1.1 SSD(NAND Flash)技术

固态硬盘是用固态电子存储芯片阵列而制成的硬盘。固态硬盘的存储介质可分为2种,一种是采用闪存(FLASH芯片)作为存储介质[4],另外一种是采用DRAM作为存储介质。基于闪存的固态硬盘是固态硬盘的主要类别,其内部构造十分简单,固态硬盘内主体其实就是一块有着控制芯片、缓存芯片和用于存储数据闪存芯片的PCB板。SSD相较于传统的机械硬盘拥有以下优点:

① 不用磁头,快速随机读取,读延迟极小;

② 无噪音。因为没有机械马达和风扇,工作时噪音值为0 dB;

③ 工作温度范围更大。典型的硬盘驱动器只能在5~55℃范围内工作。而大多数固态硬盘可在-10~70℃工作,一些工业级的固态硬盘还可在-40~85℃,甚至更大的温度范围下工作;

④ 低容量的固态硬盘比同容量硬盘体积小、重量轻。

因此SSD目前以传统硬盘无法比拟的优势逐步蚕食传统硬盘的市场,相信在不久的将来会代替传统硬盘,成为存储的主流设备。

1.2 AXI片上总线协议

随着多核、多级内存及众多外设复杂化的SOC设计需求增大,总线架构日益成为系统性能的瓶颈,ARM公司适时推出了AMBA3.0系列规范,AXI作为这个系列新发布高性能协议,很快得到了整个半导体行业的广泛认可和采用,这是因为AXI协议具备以下技术优势:

① 单项通道体系;

② 结构独立的地址和数据;

③ 通道支持多项数据交换,通过并行执行的Burst碎发操作,极大地提高数据吞吐能力;

④ 很强的灵活性。

如图1所示,AXI协议有以下几大特点:

① 在整个AXI单项通道体系中,分了读写2类通道,将这2个实现机制不同的操作分开实现,这有利于协议根据读和写自身的特点,来提高数据传输能力。

② 在读和写2个独立的体系中,又细分了Address Channel、Data Channel和Response Channel。在一般的总线请求中,主设备要了解从设备的情况,需要增加读写Busy信号,这种机制不仅增加了互连线,而且增加了读写操作所需要的时序开销。在AXI协议中读写的主动权由主机交给了从机,从机完全可以根据自身硬件环境(例如总线带宽和时序等),采取最合理的读写实现方案。

③ AXI协议能兼容以前的AMBA2、AHB总线协议,但相比AHB协议具有更高的数据总线带宽、支持乱序访问和非对齐操作等优势。

图1 AXI总线读写体系结构

2 基于NAND Flash存储设备的硬件设计

本文设计的存储设备可以分为SSD电子盘和下载板2部分组成。SSD电子盘通过FMC接口接收上位机发来的数据或命令,并将其存储到NAND Flash 芯片[4]中,用户可以通过下载板先将数据从Flash芯片中先下载到下载板上,再通过网口将数据还原到PC机中用以处理。系统的整体框图如图2所示。

图2 系统的整体框图

2.1 SSD电子盘

如图3所示,SSD电子盘的硬件主要由FPGA形成的4个cortex-M1软核及24块NAND Flash芯片[5]组成,ARM Cortex-M1 处理器是第一个针对FPGA 而优化的 ARM 处理器。处理系统为4个核形成的一控三处理架构,由一个cortex-M1软核作为总控制器控制另外3个cortex-M1软核形成3条数据传输通道,轮询快速地处理由下载板发到上位机的数据,将数据快速地通过3条通道,存储到上位机上的24块NAND Flash芯片中,实现数据的存储。

图3 SSD电子盘实物图

2.2 下载板

下载板的处理器为Z-7020芯片[6],Z-7020芯片是Xilinx公司生产的Zynq-7000系列中一款,Zynq-7000系列是首款将ARM cortex-A9硬核与FPGA相结合的芯片,属于ARM+FPGA结构,如果暂时没有用到FPGA的部分,ARM处理器子系统也可以独立工作。处理器芯片连接着AXI总线和2片512 M的DDR3芯片,因为有这2片DDR3的存在,操作系统才可以顺畅地运行。此外,下载板上还有一个网口用来接收PC机的命令和数据,一个串口用来调试和测试程序,以及一个FMC接口用来与上位机相连,实物如图4所示。

图4 下载板实物图

下载板运行的系统为PetaLinux,PetaLinux操作系统[7]是PetaLogix公司发布的面向MicroBlaze软核处理器的嵌入式Linux操作系统,作为一种特殊的嵌入式微处理器系统,PetaLinux融合了SOC和FPGA各自的优点,具备软硬件在系统可编程、可裁剪、可升级等功能。它拥有专门针对FPGA片上系统的开发套件,可以在满足工程应用的同时,极大地缩短产品的开发周期。

2.3 AXI DMA

AXI总线的DMA(AXI DMA)可分为直接模式和分散/聚合模式[8],本文使用分散/聚合模式的DMA传输数据,分散/聚合模式就是可以把离散的内存组成一个描述符用来传输。AXI DMA分为MM2S用来发送数据和S2MM用来接收数据,以发送数据为例,将第一段内存地址放在MM2S_CURDESC寄存器中,最后一段内存地址放在MM2S_TAILDESC寄存器中,然后给MM2S_DMACR寄存器的最低位置1,启动DMA,传输数据,接收数据时也是一样。具体的寄存器描述如表1所示。

表1 AXI总线寄存器地址、名称及描述

地址偏移量名称描述00hMM2S_DMACRMM2SDMA控制寄存器04hMM2S_DMASRMM2SDMA状态寄存器08hMM2S_CURDESCMM2S当前描述符指针寄存器10hMM2S_TAILDESCMM2S结束描述符指针寄存器2ChSG_CTL分散/聚合模式30hS2MM_DMACRS2MMDMA控制寄存器34hS2MM_DMASRS2MMDMA状态寄存器38hS2MM_CURDESCS2MM当前描述符指针寄存器40hS2MM_TAILDESCS2MM结束描述符指针寄存器

3 基于NAND Flash存储设备的软件设计

基于AXI的SSD存储设备软件主要为:PC端窗口app程序、下载板的AXI DMA驱动程序及上位机数据处理程序。其中AXI DMA驱动最为重要,也是SSD存储设备性能的主要程序,本文的研究重心也是下载板AXI DMA驱动,AXI DMA程序大体可分为5步,其流程图如图5所示。

① DMA通道申请

DMA数据的传输都是通过通道来完成的,所以驱动的第一步是申请DMA通道[9]。本文使用dma_request_channel函数来申请DMA通道。通道申请完成后需要提交使用,提交申请的通道使用函数dmatest_add_slave_channels(chan,rx_chan),函数的参数为申请的通道。

② 申请数据内存及数据初始化

当申请和提交后,需要申请数据内存以及初始化传输数据。申请数据空间时要注意cache一致性问题[10],因为DMA传输需要的是内存的物理地址而CPU给内存赋值时操作的是缓存,CPU赋值后要想数据能DMA传输需要将cache中的数据刷到内存中,所以申请的空间最好能是cache一致性空间。本文用dma_alloc_coherent()函数申请一致性空间[11],空间申请完,需要CPU给空间赋上要传输的数据(即数据的初始化使用函数)dmatest_init_src()完成。

③ 数据描述符的封装

数据初始化完成后,需要将数据封装成用于DMA传输的描述符[12]。本文使用的是AXI DMA的S/G模式,所以使用device_prep_slave_sg(tx_chan,rx_sg,bd_cnt,DMA_MEM_TO_DEV,flags,NULL)完成描述符的封装,参数分别为传输通道、传输的分散内存、分散内存的个数、传输方向和应答标志。

④ DMA传输

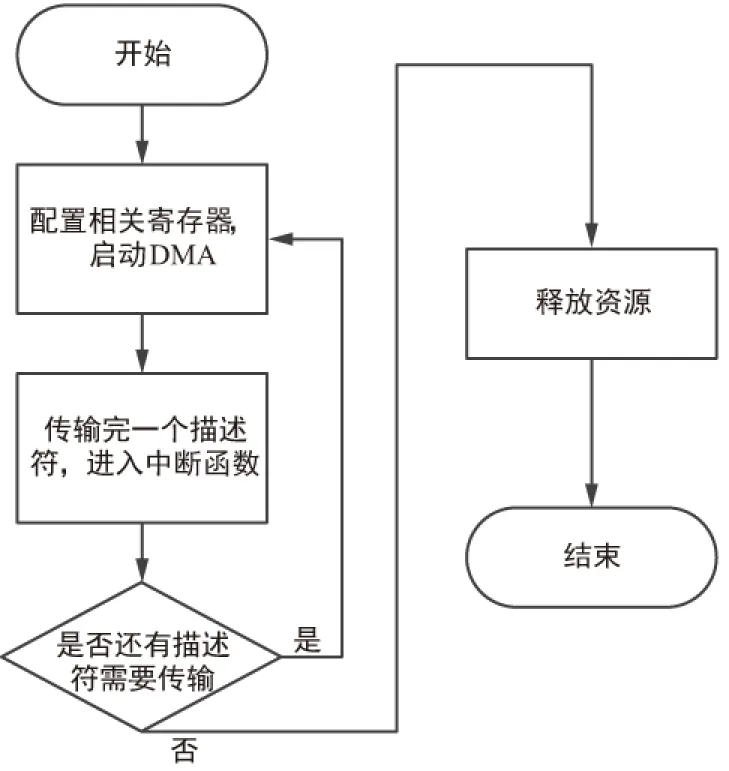

封装完数据描述符后,需要将描述符挂载到通道上用于传输[13]。挂载完成后给控制寄存器最低位置1,启动DMA,用dma_async_issue_pending(chan)函数完成,当一个描述符传输完成之后会产生一个中断,并进入中断处理函数,在中断处理函数中判断是否有下一个描述符需要传输,如果有则继续传输,如果没有,传输结束。具体流程如图6所示。

图6 数据传输流程图

⑤ 传输完成释放资源

数据传输完成后,需要将申请的数据空间和传输通道释放掉,分别用kfree(thread->srcs)和dma_release_channel(chan)实现。

4 操作步骤及实验结果

经实验测试,基于NAND Flash存储设备传输数据的速度最高可达到230 MB/s。其测试原理:传输的数据量÷传输所用的时间。所以只需要知道传输的数据量和传输这些数据所用的时间,即可求得设备的传输速度。

本文驱动发送数据的方式是循环发送,一次循环发送64 KB的数据,并且发送结束时会进入回调函数,在程序发送数据前获取时间用do_gettimeofday(&tv_start)来实现[14],所得到的时间为tv_start。在回调函数中加入函数记录驱动进入回调函数的次数n,随即循环发送数据,当数据发送结束后,再调用do_gettimeofday(&tv_end)来获取发送数据之后的时间,得到时间为tv_end,这样传输速度就可用64 K*n/ (tv_end - tv_start)值得到。

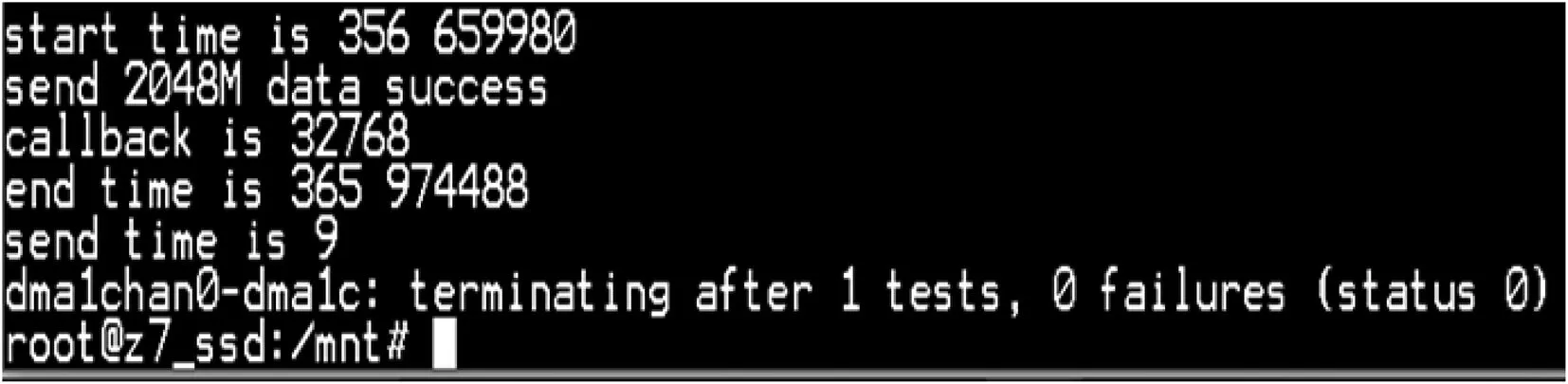

将程序编辑成模块并加载到内核中,然后编辑内核将生成的内核文件image.ub[15]、引导文件boot.bin和系统文件system.dtb拷贝到下载板中。在串口助手的窗口种输入命令insmod axidmatest.ko来加载驱动模块,会得到图7所示的图片。

图7 试验测试结果图

如图7所示,发送的开始时间为356.659 980 s,发送的结束时间为365.974 488 s。Callback为进入回调函数的次数为32 768次,如上文所说,循环发送数据,循环一次发送64 KB数据同时调用一次Callback函数,也就是说此次发送了64*1 024*32 768=2*1 024*1 024*1 024=2 G数据,发送时间约为9 s,所以传输速率为2 G / 9 = 227.6 MB/s。

5 结束语

此次设计了一款基于NAND Flash的存储设备,首先简述了基于AXI总线SSD设备的主要技术,完成了SSD设备的硬件设计和软件设计,阐述了测试数据产生的原理以及实际操作步骤。设计原理和实验数据表明,本文设计的存储设备可以和AXI片上总线完美结合,拥有很好的传输速度和很稳定的系统,无论是设备的硬件设计,还是软件模块程序都可以为研究AXI总线、SSD存储设备或AXI DMA驱动提供一定的参考价值。未来的研究工作将进一步提高设备的性能,并在数据传输安全上进一步优化和改进,使其能拥有更高的推广性和普及性。

[1] 雷雨. 基于PCIE固态硬盘的嵌入式存储技术[D].成都:中国科学院研究生院(光电技术研究所),2014.

[2] 彭振翼. 固态存储系统PCIe接口的设计方法与实现[D].武汉:华中科技大学,2013.

[3] Yu Z L,Hua J,Feng L. The Design and Implement of SSD Chip with Multi-Bus and 8 Channels[J]. Applied Mechanics & Materials,2011,58-60:2592-2596.

[4] 郑文静,李明强,舒继武. Flash存储技术[J]. 计算机研究与发展,2010(4):716-726.

[5] 黄小勇. NAND Flash的存储管理设计[D].北京:北京邮电大学,2011.

[6] 倪峰. 基于Zynq7000嵌入式平台的Flash验证系统设计与实现[D].苏州:苏州大学,2014.

[7] 薛慧敏,武传华,路后兵. MicroBlaze处理器的PetaLinux操作系统移植[J]. 单片机与嵌入式系统应用,2011(4):67-69.

[8] 张迪宇. 基于AHB总线的DMA控制器分析与验证[D].西安:西安电子科技大学,2015.

[9] 梁科,李国峰,王锦,等.通用多通道高性能DMA控制器设计[J]. 天津大学学报,2008(5):621-626.

[10]张骏,田泽,梅魁志,等. 基于节点预测的直接Cache一致性协议[J].计算机学报,2014(3):700-720.

[11]曹彦荣,张 锐. DMA传输与Cache一致性分析[J]. 硅谷,2014(8):39-40.

[12]李超,邱柯妮,张伟功,等. 基于PCIE总线主模式DMA高速数据传输系统设计[J]. 电子技术应用,2015(9):142-145.

[13]杨立成,刘丹峰,史继辉. 基于DMA的大批量数据快速传输模块设计[J]. 电子科技,2012(12):49-51.

[14]孙亮亮,吕虹,刘德方,等. 嵌入式系统中实时时间的获取[J]. 电子技术,2009(2):63-66.

[15]舒志文. 嵌入式Linux操作系统实时性的研究与实现[D].武汉:华中科技大学,2007.

Design and Implementation of Storage Device Based on NAND Flash

PAN Xu-ming,LIU Song-yan,QI Ke-xin ,WU Shang-ru,CHEN Ting

(School of Electronic Engineering,Heilongjiang University,Harbin Heilongjiang 150080,China)

Flash is the most popular storage medium,which has the advantages of high transmission speed,low power consumption,no noise and so on. However,when it is used for storage device,the performance is often limited by the limitations of on-chip buses. Aiming at the problem of Flash performance restricted by bus,a NAND Flash storage device based on AXI bus is designed. The designed storage device has the functions of multi-channel transmission,pipeline operation,ECC check,RAID5 architecture storage and so on. Design analysis and test results show that the designed storage system has faster transmission speed and is more stable,and the data reliability is enhanced at the same time. This provides a new solution for the research of NAND Flash storage devices.

AXI bus;SSD;DMA;NAND Flash

10. 3969/j.issn. 1003-3114. 2017.22

潘旭明,刘嵩岩,齐可心,等.基于NAND Flash的存储设备设计与实现[J].无线电通信技术,2017,43(4):91-95.

[PAN Xuming ,LIU Songyan ,QI Kexin,et al. Design and Implementation of Storage Device Based on NAND Flash [J]. Radio Communications Technology,2017,43(4):91-95. ]

2017-03-03

潘旭明(1990—),男,硕士研究生,主要研究方向:嵌入式系统与应用。刘嵩岩(1969—),男,副教授,主要研究方向:嵌入式系统与应用。

TP333.5

A

1003-3114(2017)04-91-5