基于VHDL语言的数字钟设计

张颖

摘 要:以自顶向下的模块化方法进行数字钟系统设计,采用VHDL语言编写各功能模块,原理图作为顶层文件的方式,在Quartus II集成开发环境里进行编译、仿真、综合,最后在线下载到实验箱进行调试,调试结果表明:数字钟的时间显示、调时和闹钟功能均可实现。

关键词:EDA技术;VHDL;自顶向下;数字钟

引言

随着可编程逻辑器件应用的日益广泛,以大规模可编程集成电路为物质基础的EDA技术打破了软硬件之间的设计界限,使硬件系统软件化,这已成为现代电子设计技术的发展趋势。[1]VHDL(超高速集成电路硬件描述语言)作为一种常用的数字系统设计输入方式,语法结构严谨,描述功能强大,可用简洁明了的代码描述复杂的逻辑电路设计。而且VHDL语言支持从系统级到门级所有层次的设计,支持自顶向下的模块化设计方法,在电子设计领域,已被广泛使用。本文详述使用VHDL语言实现对数字钟的层次化设计,将文本编辑和图形编辑两种方式混合使用[2],实现数字钟计时、调时和闹钟功能。

1 系统总体设计

设计数字时钟要求实现以下功能:(1)能显示时、分、秒;(2)可手动调整时和分;(3)具有闹钟功能,可设定时间并且到时提醒。根据系统的功能,采用自顶向下的模块化设计方法,以VHDL语言描述底层模块硬件功能,原理图做顶层文件的方式进行设计。根据数字钟的功能要求,可以把系统大体分为三部分:计时部分、闹钟部分和显示部分。计时部分的主体是3个级联的异步计数器,计数并输出结果。其中秒、分计数模块分别由60进制计数器组成,时计数模块由24进制计数器组成,且上一级计数器的进位输出信号作为下一级的时钟脉冲输入。为了实现调时调分功能,则分别在秒、分计数模块外部增加调分调时控制端和调时信号脉冲输入端。闹钟模块则要求具有闹钟功能控制端,若控制端有效,模块可以手动调整闹钟时间;反之,则进行正常的计时功能。而且当闹钟时间与正常时间相同时,可以发出提醒信号[3]。显示部分则要通过动态扫描的方法将计数器的输出送到数码管上来显示,由选择模块和数码管显示模块组成。

2 底层模块的设计与实现

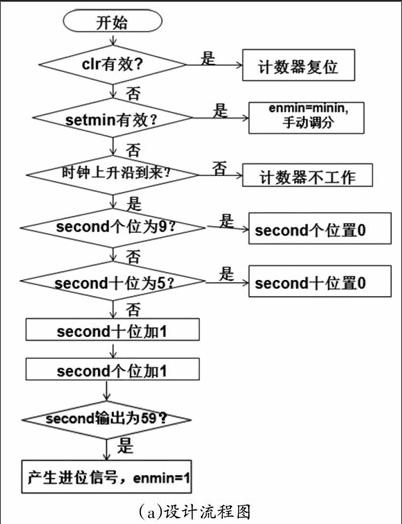

2.1 秒计数模块(实体second)

秒计数模块可以看成一个60进制的计数器,实现正常的计时和调分功能。此模块与分计数模块进行级联,其进位输出信号enmin作为下一级分计数模块的时钟输入,即秒计数器计数到59时,enmin端输出单个脉冲,此时分计数器加一计数。

当复位端clr有效时,计数器复位清零;当clr无效时,如果调分控制端setmin有效,计数器则进入调分状态,进位输出端enmin不再输出计数器的计数结果,而是输出手动调分信号minin(minin输入端为手动控制的脉冲信号),通过使下一级分计数模块以minin脉冲信号的频率快速计数来完成调分功能;如果setmin无效,则计数器处于正常计时状态,从00计数到59并输出进位信号。硬件功能描述时通过多个if语句的嵌套使用来实现,根据时钟信号clk的输入按照流程图所示依次循环。过程中采用十进制计数,并且用BCD码来表示个位和十位数字,使其易于理解也方便数码管的显示。设计流程如图1(a)所示,生成的逻辑符号如图1(b)所示。

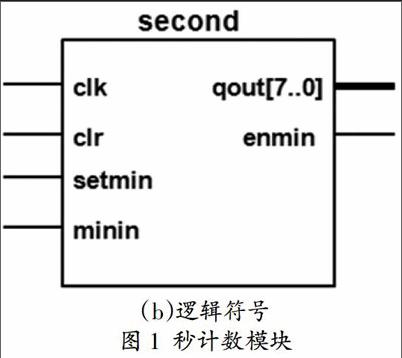

2.2 分计数模块(实体minute)

分计数模块实质上与秒计数模块相同,也是一个60进制的计数器,可实现计时和调时功能。模块与下一级时计数模块级联,当计数到59时,进位输出端enhour输出单位脉冲到时计数模块的时钟输入端clkm,时计数模块加一计数。其设计流程同秒计数模块相似,调时功能也是通过调时端sethour来控制进位输出端enhour输出手动调时信号hourin,使时计数模块快速计数到需要的时间。生成模块的逻辑符号如图2所示。

2.3 时计数模块(实体hour)

时计数模块是一个简单的24进制计数器,其时钟输入信号是分计数模块的进位输出,不需要产生进位信号。模块功能描述与分、秒计数模块大同小异,但要注意此计数器是从00计数到23,所以需多加一个if语句使计数器计数到23后复位清零。逻辑符号如图3所示。

2.4 闹钟模块(实体naozhong)

此模块通过3个进程语句,分别描述了手动设定闹钟时、分和到时提醒的功能。设定闹钟时间的设计思路与之前second模块调分功能相似,也是控制计数器加一计数直到需要的时间为止。以闹钟调分为例,当闹钟调分控制端setm有效时,进入闹钟定时模式,通过minnao端手动调分信号的输入来设定闹钟时间,这里输入的minnao信号与分计数模块的时钟输入信号clk作用相同,控制计数器进行计数,其过程与前面时、分、秒計数过程是分开的,二者互不影响;若setm端无效,输出端outm、outh输出时、分计数模块的正常计数结果(即inm和inh的输入)。而闹钟调时过程则需注意是从00计数到23,是24进制计数。设计流程如图4(a)所示。第三个进程语句较为简单,只需通过if语句来判断设定的闹钟时间与正常的计数时间是否相同,若相同,则产生提醒信号。生成模块逻辑符号如图4(b)所示。

2.5 选择模块(实体select)和数码管显示模块(实体display)

这两个模块实质上是通过动态扫描的方法显示时间。select模块相当于数据选择器,在高频率时钟信号的作用下进行循环扫描,选择显示的数码管以及对应的时、分、秒的结果。display模块则接受选择信号,轮流向各位数码管送出字形码和相应位选,使七段数码管显示所对应的数字。此处的clk端必须输入较高频率的时钟信号,利用发光管的余辉和人眼视觉暂留作用,使人感觉好像各位数码管都在显示[4]。模块逻辑符号如图5(a)(b)所示。

2.6 顶层设计原理图

在各模块编译通过且仿真成果正确的基础上,采用顶层原理图的设计方法,系统顶层方框图如图6所示。在实验中,还可在闹钟模块的提醒信号输出端sp后接一个简单的电子琴模块,当sp信号产生时,闹钟定时与正常计时相同,此时控制电子琴模块自动演奏乐曲作为闹钟铃声。

3 结束语

根据上述数字钟设计实例,可以看出通过VHDL 语言实现电子设计,是一个以软件设计为主,器件配置相结合的过程,能从多个层次对数字系统进行设计,设计数字电路更为灵活方便,设计周期也可大大减小,提高了设计效率和可靠性[5]。VHDL语言作为一种标准的硬件描述语言,具备强大的行为描述能力和移植复用能力,支持复杂电路设计的层次化分解和已有设计的移植再利用,已经成为数字系统设计不可缺少的重要工具。

参考文献

[1]李国丽,朱维勇,何剑春.EDA与数字系统设计[M].北京:机械工业出版社,2009.

[2]胡宏梅.基于VHDL语言的数字钟层次化设计与实现[J].电气自动化,2016(1).

[3]赖伟玮,苏静怡.FPGA原理及应用结课论文[D].东北大学秦皇岛分校,2012.

[4]席玉清,陈化奎.两位数码管动态显示编程常见问题分析[J].科技创新与应用,2016(12).

[5]王彩凤.VHDL语言在电子设计中的应用[J].实验科学与技术,2014(4).