基于FPGA和USB3.0的通用数据传输系统设计

匡 鹏,刘 冲,王永纲

(中国科学技术大学 近代物理系,安徽 合肥 230026)

基于FPGA和USB3.0的通用数据传输系统设计

匡 鹏,刘 冲,王永纲

(中国科学技术大学 近代物理系,安徽 合肥 230026)

现场可编程门阵列(FPGA)的高度灵活性和强大的数据处理能力,使其在越来越多的领域得到应用。USB 3.0也是目前主流的数据传输协议之一,具有速度快、功耗低等优点。将USB 3.0接口应用到FPGA上,能够有效地解决FPGA与上位机之间的数据传输问题,大大提高生产效率。文章利用USB 3.0的控制器芯片CYUSB3014实现了FPGA与上位机之间的高达390 MB/s的数据传输系统。

高速数据传输系统;现场可编程门阵列;USB 3.0;CYUSB3014

0 引言

现场可编程门阵列(FPGA)具有极高的灵活性以及强大的数据处理能力,在科学研究、大型实验仪器和商用医疗设备等诸多领域中早已被成熟使用。但是FPGA本身并没有提供任何与上位机通信的接口,这使得FPGA与上位机之间传输数据变得很不方便。开发者每次都必须根据具体外设重新开发FPGA和上位机的数据传输系统,从而降低了开发效率。

通用串行总线(USB)3.0标准早在2008年就已经提出,现在已取代USB2.0成为USB主要使用版本。USB3.0比USB2.0有更高的传输速度和更低的功耗。USB3.0的协议速度高达5.0 Gb/s(625 MB/s),是USB2.0的10倍之多。CYUSB3014是赛普拉斯(CYPRESS)公司设计的一款USB3.0外设控制芯片,它的主要功能是在USB主机与外设之间传输高宽带数据。该芯片提供一个第二代通用可编程接口(GPIF II),开发者可以对GPIF II和FPGA编程,来实现从FPGA到USB控制器,再到上位机的数据传输通道。

本文利用USB3.0外设控制器CYUSB3014,实现了基于FPGA与上位机之间的数据传输接口设计[1-3]。经测试,本设计可以实现390 MB/s的FPGA到上位机的数据传输通道,以及355 MB/s的上位机到FPGA的数据传输通道,几乎达到了该芯片支持的最高速度(400 MB/s)。

1 系统结构

图1为整个系统的结构。上位机的软件应用程序(例如MATLAB)通过调用驱动程序中的应用程序编程接口(API),向CYUSB3014控制器发送数据或从它接收数据;USB控制器芯片内部通过直接内存存取(DMA)互联结构建立USB端点到GPIF II的数据传输通道;FPGA内部接口逻辑模块负责其他逻辑模块与GPIF之间的数据传输。

图1 系统整体结构

本设计以FPGA接口逻辑为主设备,GPIF为从设备,接口逻辑负责控制整个系统的工作状态。为了通用性起见,本文设计了上位机对FPGA进行FIFO读写和寄存器读写共4种功能。FIFO读写可以完成高宽带高速数据的双向传输;寄存器读写则可以完成控制和监测的功能。这样的设计能够满足大部分FPGA设计对上位机接口的需求。

2 控制器芯片工作原理

赛普拉斯公司设计生产的USB3.0外设控制芯片CYUSB3014具有高度集成的灵活特性,它具有一个可进行完全配置的并行通用可编程接口GPIF II,可与任何处理器、ASIC或FPGA连接。芯片集成了USB 3.0和USB 2.0物理层(PHY)以及32位ARM926EJ-S微处理器,具有强大的数据处理能力,并可用于构建定制应用[1]。

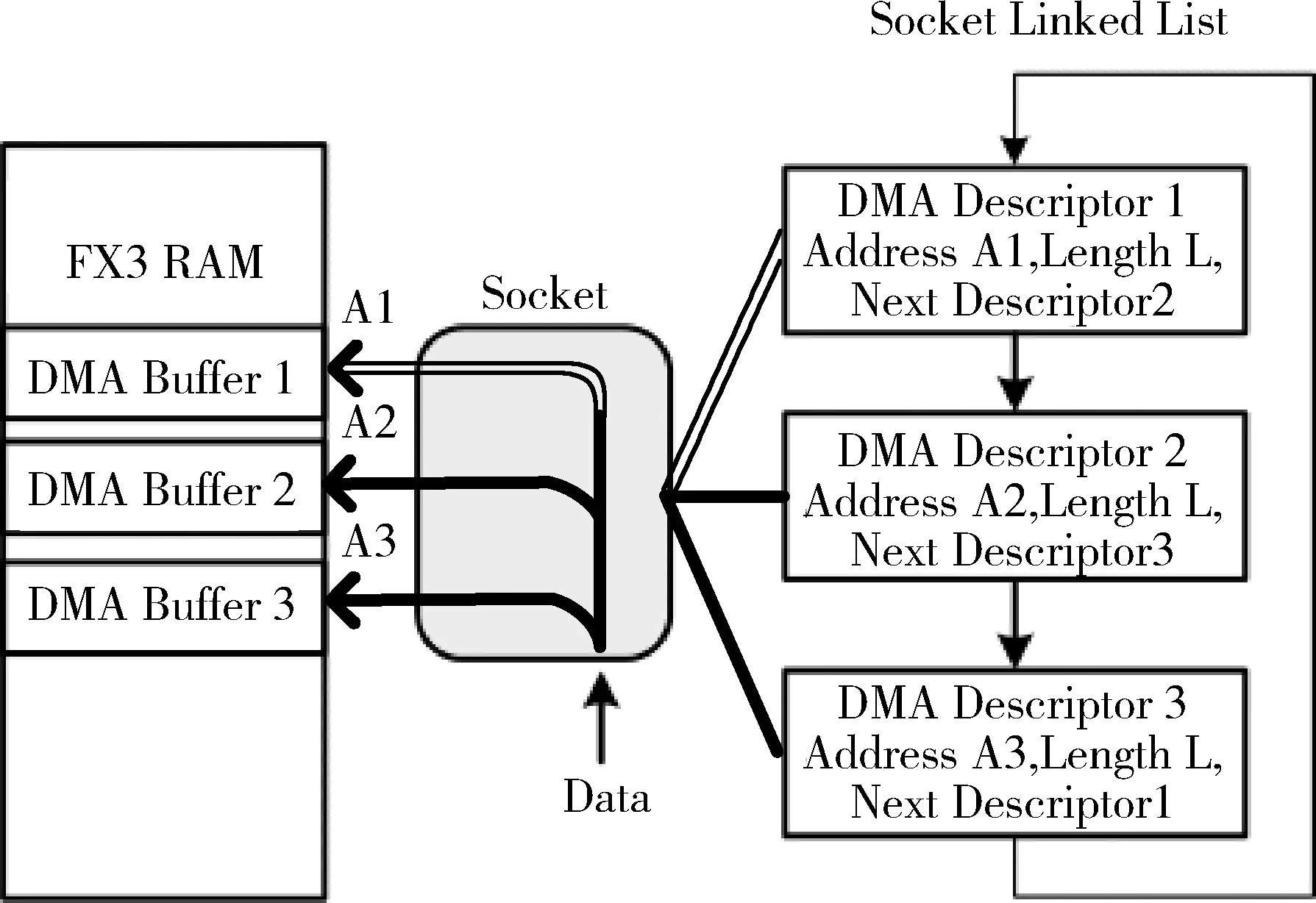

图2表示了控制器芯片的数据输入输出。其中DMA描述符(DMA Descriptor)保存了DMA缓冲区的地址和大小,以及指向下一个DMA描述符的指针。套接字(Socket)是外设硬件模块与RAM之间的连接点,每个外设硬件模块(如USB、GPIF、UART和SPI)具有各自固定的套接字数量,简单来说可以把套接字看成外设的接口。DMA缓冲区(DMA Buffer)是RAM的一部分,用来缓存外设间需要传输的数据,这部分RAM的地址正是DMA描述符中保存的地址。

图2 DMA通道示意图

当外设之间进行数据传输时,例如将GPIF的数据传输到USB端点,控制器会自动加载相应的DMA描述符,然后从GPIF的套接字接收数据,保存到RAM中DMA描述符所指定的地址。当前DMA描述符处理完后,系统会自动加载下一个DMA描述符。DMA缓冲区的切换需要消耗几个微秒的时间,在切换DMA缓冲区时,当前的DMA通道不能进行数据传输[4]。当某个DMA缓冲区被写满,或者GPIF主动提交数据包时,系统开始把该缓冲区的数据发送到USB端点。从USB端点到GPIF的数据传输过程与之类似,只不过数据传输的方向刚好相反。

3 系统设计

3.1 控制器芯片固件设计

USB控制器芯片的固件设计包括GPIF II状态机设计和运行于芯片内部ARM微处理器上的可执行程序设计。其中,GPIF II状态机的设计是关键,它描述了USB芯片如何响应主设备FPGA接口逻辑模块发出的请求。

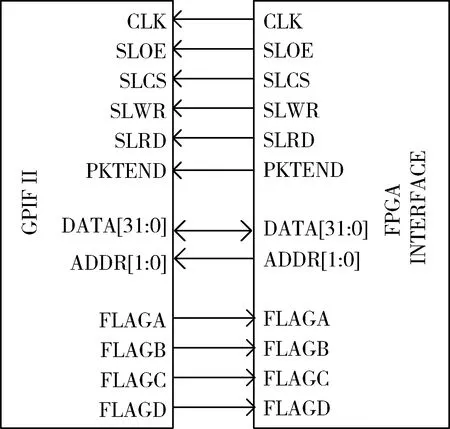

图3给出了USB控制芯片与FPGA的接口连接。其中,CLK是由FPGA提供的频率最高为100 MHz的时钟信号。DATA信号是双向数据线,完成GPIF与FPGA之间的双向数据传输。ADDR为地址线,用于选择使用哪个GPIF进程传输数据。GPIF共有4个独立进程,每个进程与相应的DMA通道绑定。FPGA通过改变地址线ADDR,从而选择使用哪个DMA通道进行数据传输。控制信号均由FPGA发出,控制信号包括SLOE、SLCS、SLWR、SLRD、PKTEND,这些信号均为低电平有效。SLCS为片选信号,系统工作时,SLCS必须始终有效(即始终为0)。SLRD为读请求信号,该信号有效时,GPIF会把缓存在RAM中的数据传输给FPGA。SLOE为输出使能信号,它的唯一作用是驱动数据总线DATA翻转。因为FPGA发出读请求后,USB芯片并不能立刻将有效数据传递到GPIF端点,从SLRD有效到DATA有效有两个时钟周期的延迟[5],因此需要额外的数据总线驱动信号SLOE。SLWR是写请求信号,该信号有效时,FPGA会发送数据给GPIF,GPIF随之将这些数据缓存在RAM中。PKTEND为传输结束信号,该信号用来标志此次数据传输结束。

图3 FPGA与GPIF之间的接口连接

另外,还有4个DMA标志信号FLAGX。这些信号由USB芯片发出,FPGA接收。这些信号并不是由GPIF状态机控制的,FLAG信号用来标志指定DMA通道对应的缓冲区的状态。

3.2 FPGA接口设计

FPGA接口既要完成与USB控制器GPIF II对接,同时也要提供对FPGA内部逻辑模块的数据传输接口。FPGA接口逻辑是本系统的核心,它作为主设备,控制着从设备GPIF的工作状态。FPGA接口逻辑模块内部有一些标志工作状态的寄存器,用户可以通过上位机软件来配置这些寄存器,从而指定整个系统的工作模式。因此,在执行某种操作之前,需要通过上位机软件先对FPGA接口逻辑模块进行配置。

图4 FPGA接口逻辑对外提供的接口

FPGA接口逻辑除了具有3.1节中与GPIF II相连接的接口外,还提供了其他接口与FPGA内部其他逻辑模块相连接。图4给出了这些接口信号。CLK是接口的工作时钟(100 MHz),同时这个时钟也是GPIF II的工作时钟。RST是全局复位信号。剩下的信号则用来完成FIFO读写和寄存器读写的功能。

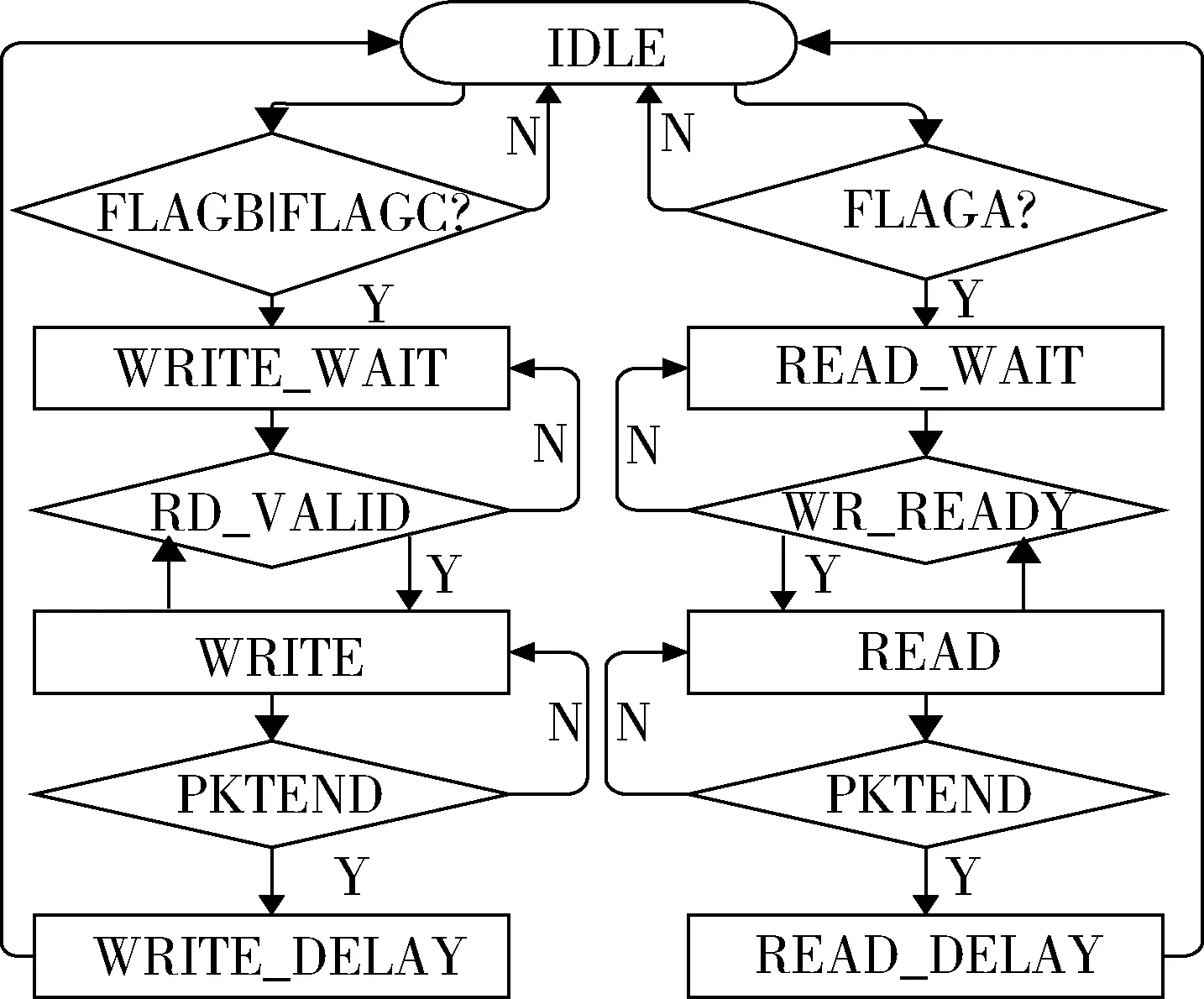

在进行FIFO读操作时,使用的接口信号是RD_ACK、RD_VALID和RD_DATA。当RD_VALID有效时,标志着外部FIFO数据有效,RD_ACK作为应答信号告知外部逻辑已经完成对该有效数据的读取。使用时,先通过上位机软件对接口逻辑模块进行配置,配置的信息确定了接口模块将工作在读FIFO模式,同时还确定了此次读FIFO的数据个数。当读取FIFO的数据个数达到上位机所请求的个数时,接口逻辑模块停止读取外部FIFO,同时停止向GPIF发送数据,并且发出PKTEND信号,标志着此次传输结束。

在进行FIFO写操作时,使用的接口信号是WR_ACK、WR_READY、WR_DATA。当WR_READY有效时,标志着接口模块可以向外部FIFO写入数据,WR_ACK作为应答信号告知外部逻辑已经完成了数据的写入。与读FIFO类似,使用时先通过上位机软件对接口模块进行配置。配置信息确定了接口模块工作在FIFO写模式,同时确定了将要写入的数据个数。

图5 FPGA接口逻辑状态机

图5给出了FPGA接口逻辑模块的状态机向GPIF收发数据时的工作流程。系统最初处在空闲状态(IDLE),然后根据配置信息确定的工作模式,以及DMA通道的FLAG标志信号,进入相应的状态机流程中。

此外,接口逻辑模块还实现了寄存器读写的功能,寄存器读写使用的DMA通道与FIFO读写的通道相同,只是传输的数据个数始终为1。

3.3 上位机软件设计

赛普拉斯官方提供了USB控制器芯片的驱动程序,并且提供了相应的应用程序接口(API)。为了使用方便,本设计在官方提供的API基础上,将主要功能(FIFO读写和寄存器读写)用C++封装成动态链接库(DLL)。这样用户可以直接在自己的C/C++工程中调用已经封装好的库函数。在封装库函数时,已经将配置FPGA接口模块这步工作封装在了相应的功能函数中,这样用户就不必先单独配置FPGA逻辑模块。

考虑到现在大部分研究阶段的数据处理工作都是使用MATLAB进行,本设计进一步将DLL函数封装成MATLAB函数,以便MATLAB能够直接使用USB的相关功能。

4 测试结果

4.1 测试环境

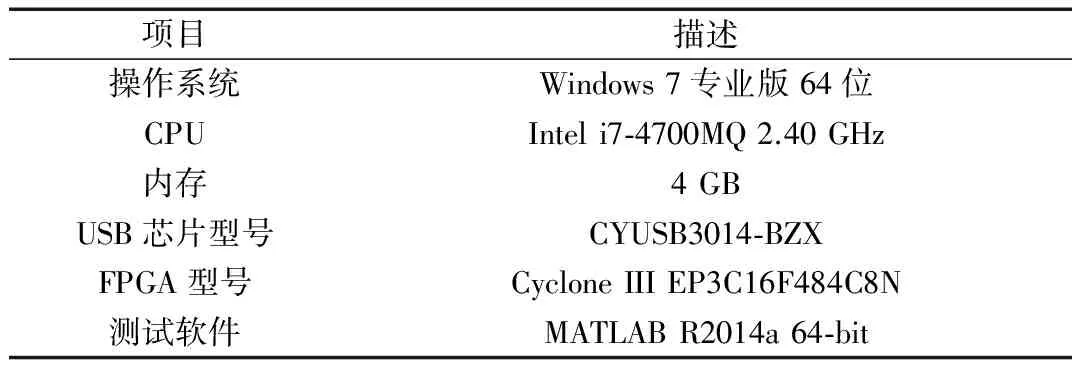

测试环境如表1所示。

表1 测试环境

4.2 寄存器读写测试

寄存器读写只涉及到正确性问题,测试工程在FPGA内部例化了16个32 bit的寄存器。测试时对某个寄存器随机写入一个数值,然后再把该寄存器的值读回来,比较读取的值是否等于写入的数值。经循环对这16个寄存器进行读写测试,发现寄存器读写功能能够稳定地正常工作。

4.3 FIFO回环测试

FIFO回环测试是为了验证FIFO读写的正确性。测试时,MATLAB先将1 024个数据写入到FPGA的FIFO中,然后再将这些数据从该FIFO中读出,验证读出的数据是否是原来写入的数据。经过测试,FIFO读写也能正常稳定地工作。

4.4 读写FIFO速度测试

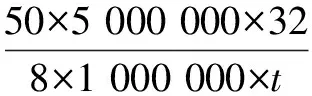

经测试,本设计读FIFO的速度能够达到390 MB/s左右,而写FIFO的速度能够达到355 MB/s左右。

5 结论

本设计利用USB 3.0控制器芯片CYUSB3014实现了FPGA与上位机之间的高宽带数据传输系统。主要实现的功能包括上位机对FPGA的寄存器读写和FIFO读写。经测试,这些功能都能稳定地正常工作。上位机读FIFO的速度能够达到390 MB/s,写FIFO的速度能够达到355 MB/s,接近于CYUSB3014芯片支持的理论最高速度400 MB/s。之所以读FIFO的速度会比写FIFO的速度高出不少,主要原因是因为在设计固件程序时,读FIFO使用了DMA双通道,而写FIFO则只使用了DMA单通道。

[1] 陈松. 基于USB3.0的高速数据传输系统的研究与设计[D]. 成都: 电子科技大学, 2014.

[2] 徐超, 刘冲, 王永纲. 基于FPGA和USB2.0协议的通用数据传输设计[J]. 微型机与应用, 2016,35(16): 41-43.

[3] 王成儒, 李英伟. USB2.0原理与工程开发[M]. 北京: 国防工业出版社, 2004.

[4] Manaskant Desai, Karthik Sivaramskrishnan. O-ptimizing USB 3.0 throughput with EZ-USB®FX3TM[EB/OL]. (2015-10-22)[2016-10-30]. http://www.cypress.com/file/125281.

[5] Rama Sai Krishna V. Designing with the EZ-USB FX3 Slave FIFO Interface[EB/OL]. (2014-07-21)[2016-10-30]. http://www.cypress.com/file/136056.

Design of universal data transmission system based on FPGA and USB3.0

Kuang Peng, Liu Chong, Wang Yonggang

(Department of Modern Physics, University of Science and Technology of China, Hefei 230026, China)

Field-programmable gate array (FPGA) is used more and more in various fields due to the highly flexible and powerful ability of data processing. USB 3.0 is one of the mainstream data transmission protocols, with the advantages of fast speed and low power consumption. Implementing USB 3.0 interface on FPGA can effectively solve the problem of data transmission between FPGA and the host computer, greatly improve production efficiency. In this paper, a data transmission system between FPGA and the host computer is designed and implemented with the USB 3.0 controller CYUSB3014, which achieves transmission speed of up to 390 MB/s.

high throughput data transmission system; FPGA; USB 3.0; CYUSB3014

TP334.7;TN791

A

10.19358/j.issn.1674- 7720.2017.07.008

匡鹏,刘冲,王永纲.基于FPGA和USB3.0的通用数据传输系统设计[J].微型机与应用,2017,36(7):26-28,34.

2016-11-14)

匡鹏(1991-),通信作者,男,硕士研究生,主要研究方向:FPGA逻辑设计。E-mail: kp77@mail.ustc.edu.cn。

刘冲(1989-),男,博士,主要研究方向:基于FPGA的高精度TDC系统研究与设计。

王永纲(1965-),男,博士,教授,博士生导师,主要研究方向:正电子断层扫描(PET)系统研究与设计。