高速大容量数据记录仪的无效块信息列表动态刷新算法设计

张志伟,靳 鸿*,李祖博,霍新明,张 瑞

(1.中北大学电子测试技术国家重点实验室,太原 030051;2.中北大学仪器科学与动态测试教育部重点实验室,太原 030051)

高速大容量数据记录仪的无效块信息列表动态刷新算法设计

张志伟1,2,靳 鸿1,2*,李祖博1,2,霍新明1,2,张 瑞1,2

(1.中北大学电子测试技术国家重点实验室,太原 030051;2.中北大学仪器科学与动态测试教育部重点实验室,太原 030051)

针对流水线技术构建的高速大容量存储阵列,设计了一种基于FPGA的“无效块信息列表动态刷新算法”。系统以NAND型Flash为存储介质,以FPGA为逻辑控制中心,在其内部建立一个一维RAM实现了高速大容量存储系统的无效块信息的记录。仿真结果及可行性分析验证了“无效块信息列表动态刷新算法”的可行性,该算法建立的无效块信息列表的容量不受存储容量扩展的影响,减少了对FPGA内部资源的占用,在满足大容量存储的同时,且不影响高速存储。

飞行器仪表、设备;高速大容量;FPGA;无效块;Flash

随着存储技术和航空航天技术的飞速发展,在各种飞行器飞行试验中,基于Flash的高速大容量固态存储系统作为一种重要的记录设备,记录着飞行器的重要工作环境参数和飞行动态参数,为飞行器设计的改进提供了可靠的实验依据。记录仪启动存储后,为了保证存储数据的有效性与完整性,在Flash执行读写操作之前需要跳过Flash的无效块。目前常用的无效块管理的方法有两种:一是在写入过程中“判一块写一块”[1],该方法影响Flash的写入速度,无法实现高速存储;二是在写入前建立好无效块信息列表[2-4],在进行写操作时,从列表中读出有效块地址,但随着Flash存储块数不断增加以及高速存储时使用存储阵列技术,无效块信息列表就需要进行位扩展或者深度扩展以此满足大容量高速存储,该方法增加了软件设计的复杂度,而且对于有限的FPGA资源来说,RAM的空间大小也有限。以某高速大容量机载雷达实时图像数据记录仪为例[5],针对流水线技术构建的高速大容量存储阵列,设计了一种“无效块信息列表动态刷新算法”。

1 某高速大容量存储系统概述

某高速大容量机载雷达实时图像数据记录仪系统结构框图如图1所示,系统的接口芯片选用了与发送端LVDS串行器MAX9247匹配使用的18位LVDS解串器MAX9250[6],其中低16位用于传输数据信息,高2位用来传输控制信号;解串后的18位并行LVDS数据经数字隔离芯片ADUM3440数字隔离处理后,最后输入到FPGA,FPGA检测到控制信号为“11”时,FIFO开始接收低16位数据,若检测到控制信号为其他状态时,FIFO停止接收低16位数据;FIFO满后,在FPGA的Flash逻辑控制器的控制下写入Flash存储模块中。雷达实时图像数据存储系统结构框图如图1所示。

图1 系统结构框图

系统存储模块采用16片NAND型Flash芯片K9WBG08U1作为存储介质[7-8],每8片组成一组Flash存储阵列,其中4片采用了8级流水线操[5,9]作用来存储高8位并行LVDS数据,最快存储速率可达39.96 Mbyte/s[5],另外4片以相同的流水线方式同步存储低8位并行LVDS数据,一组Flash存储阵列存储速度最高可达39.96×2=79.92 Mbyte/s。两组Flash存储阵列结构相同,按顺序存储方式存储,存储容量共64 Gbyte。存储阵列结构原理如图2所示。

图2 存储模块结构原理图

2 无效块信息列表动态刷新算法设计

由于16位并行LVDS数据在写入过程中需要实现每组Flash的高8位和低8位子存储单元的同步并行操作,因此每组Flash的两个子存储单元必须使用相同的无效块信息列表才能保证存储数据的完整性与有效性。

“无效块信息列表动态刷新算法”根据每组Flash子存储单元的存储块数,建立一个无效块检测信息列表,列表地址同步跟踪存储单元块地址。该无效块检测过程为:系统每次上电初始化完成后,提前建立第1组Flash存储单元的无效块检测信息列表,第1组Flash存储单元无效块检测过程为:同时对第1组Flash的高8位和低8位两个子存储单元执行无效块检测,两子Flash存储单元的每个相同块地址的无效块检测结果进行“与”运算,“与”运算后的结果标记在无效块信息列表地址上。第1组Flash存储单元执行无效块检测完毕后,若第1组Flash存储单元开始存储,首先读取无效块信息列表地址上的内容,若为有效块,则对该块开始执行流水线页加载操作,在此期间,对第2组Flash存储单元的相同块地址执行与第1组相同的无效块检测操作,“与”运算后的结果重新标记在无效块信息列表地址上;若为无效块,则跳过该块,同时默认该地址对应的第2组Flash存储单元块也为无效块。这样就保证了第1组Flash存储单元存储满后,第2组Flash存储单元的无效块信息列表已经建立完成,系统可以对第2组Flash存储单元执行流水线页加载操作。同理,第n组Flash存储单元存储满后,第n+1组Flash存储单元的无效块信息列表已经建立完成,系统可以对第n+1组Flash存储单元执行流水线页加载操作。无效块信息列表动态刷新算法工作流程图如图3所示。

K9WBG08U1M内部有16384个存储块,每块容量为256kbyte,有效期内无效块不大于320个[3],那么每组Flash的每个子存储单元就有16384×4=65536个存储块,每组无效块检测结果用1位二进制数(‘0’代表无效块,‘1’代表有效块)来标记。利用FPGA内部逻辑资源开辟一个容量为64 k×1 bit的RAM,按照“无效块信息列表动态刷新算法”,整个64 G存储模块只需要建立一个一维无效块信息列表,相对于从位扩展或者深度扩展的无效块信息列表,减少了FPGA内部资源的利用。

3 仿真与可行性分析

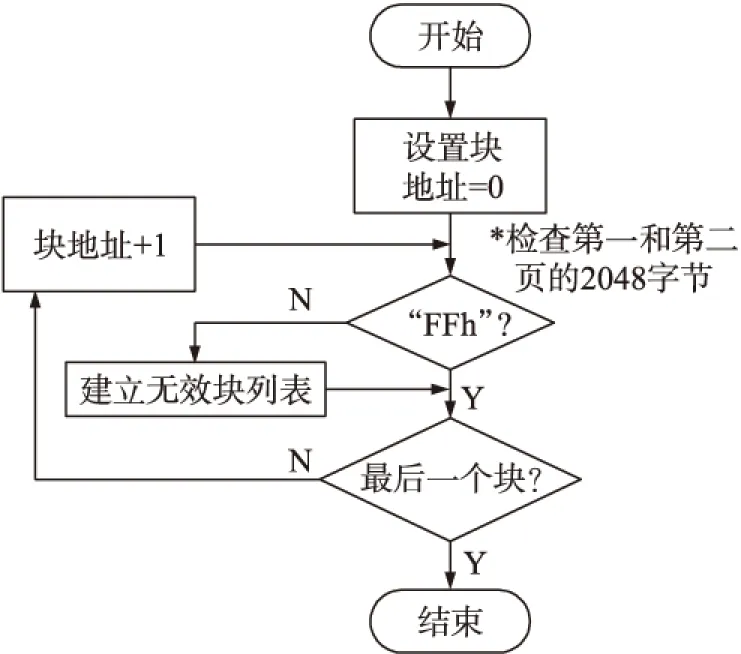

K9WBG08U1M在出厂时已经将每一块的检测信息存放在该存储块内第1页和第2页的第4 096 byte上,通过读出这两个字节的数据是否全部为“FF”,就可以判断该存储块的好坏[10],无效块检测的具体流程如图4所示。

图3 无效块信息列表动态刷新算法工作流程图

图5 Flash无效块检测在线仿真时序图

图4 Flash无效块检测流程图

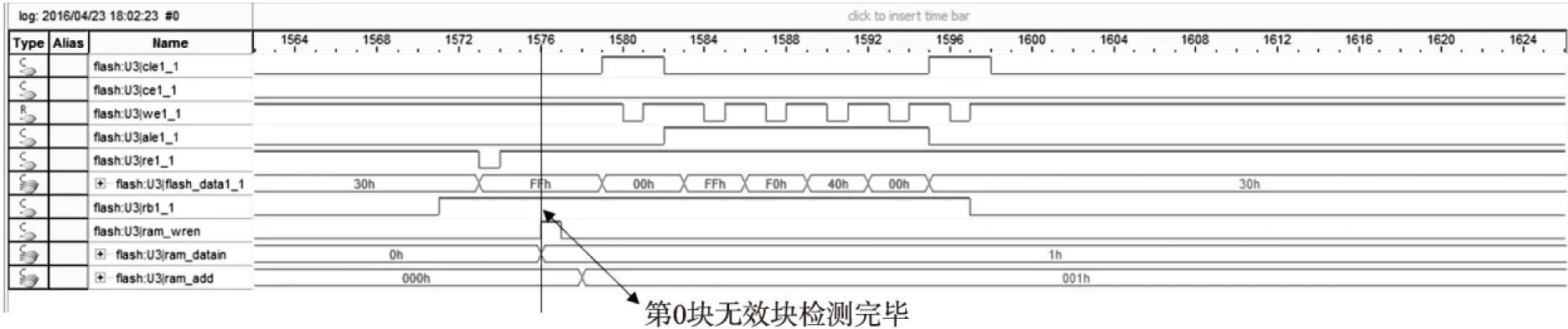

图5为使用SignalTapⅡ Logic Analyzer软件对Flash执行无效块检测操作的在线仿真时序图,逻辑分析器的采样时钟周期选择Flash的写时钟twc(频率为30 MHz),图6为第0块无效块检测完毕后的局部放大时序图。由图6可以看出当某第0块无效块检测完毕后时,ram数据写使能ram_wren拉高(写有效),并将检测结果标记到RAM中,随后ram的地址计数器ram_add加1,ram数据写使能ram_wren拉低(写无效),开始执行下一块的无效块检测。

由图5和图6可知检测一块共需要N1=1 576个采样时钟,那么检测一块所需的时间tcheck为:

tcheck=N1·twc≈52.53 μs

图6 局部放大后的仿真时序图

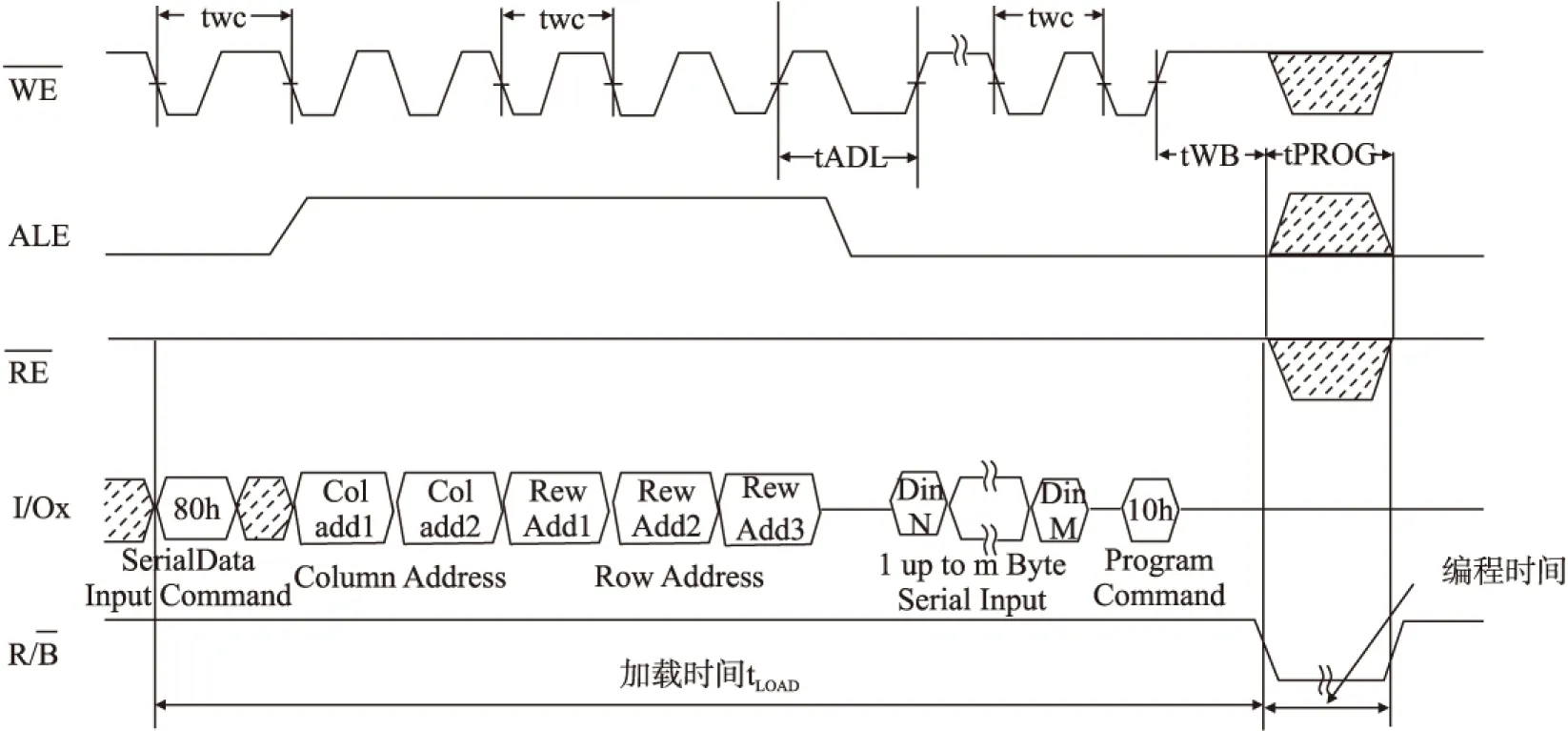

图7为Flash芯片页编程操作部分时序图,Flash经过页编程的命令(80 h)、地址加载及tADL之后,开始加载数据。数据加载完毕后,再经过页编程的命令(10 h)加载和tWB之后,Flash进入页编程状态。

图7 Flash页编程操作部分时序图

(1)页编程所有的命令和地址加载时间t1为

t1=7twc

(2)由芯片资料可知:tADL≥100 ns,tWB≤100 ns,取

tADL=4twc

(3)Flash写满一页所需的数据加载时间t2为

t2=4 096twc

(4)Flash写满一页一共所需的加载时间tLOAD为

136.9 μs≤tLOAD=t1+tADL+t2+tWB≤137 μs

tcheck 本文主要介绍了一种高速大容量机载雷达实时图像数据记录仪,针对流水线技术构建的高速大容量存储阵列,设计了一种基于FPGA的“无效块信息列表动态刷新算法”,该算法建立的无效块信息列表的容量不受存储容量扩展的影响,减少了对FPGA内部资源的占用,在满足大容量存储的同时,且不影响系统的高速存储,为高速大容量存储系统的无效块检测提供了一种全新的手段,且具有一定的通用性,可以扩展到所有类似Flash存储系统中,具有一定的使用价值。 [1] 刘雪飞,马铁华,刘廷辉,等. 基于NiosⅡ的新型弹载双备份数据记录仪[J]. 火炮发射与控制学报,2015,36(4):59-63. [2] 史玉健,任勇峰,李辉景,等. 基于Flash的高速数据记录器的研究与设计[J]. 计算机测量与控制,2011,19(12):3158-3160. [3] 余辉龙,何昕,魏仲慧,等. NAND型闪存大容量图像存储器无效块管理[J]. 微电子学与计算机,2010,27(2):1-4. [4] 曹翱翔,张会新,刘文怡,等. 一种高速数字视频信号记录装置关键技术研究[J]. 电子技术应用,2015,41(4):87-90. [5] 任敏,张艳兵,王欢,等. 基于硬件控制的双通道机载数据记录仪[J]. 探测与控制学报,2014,36(3):82-85. [6] 孟令军,周之丽,文波,等. 基于USB3.0的LVDS高速图像记录系统的设计[J]. 电子器件,2015,4(38):812-816. [7] 魏敏,刘文怡,王金陵,等. 基于交叉双平面技术的图像采集存储系统[J]. 电视技术,2013,37(15):63-66. [8] 梁永刚,崔永俊,郇弢. 基于NAND型FLASH的双备份固态存储系统[J]. 科学技术与工程,2013,13(26):7675-7682. [9] 任勇峰,张凯华,程海亮. 基于FPGA的高速数据采集存储系统设计[J]. 电子器件,2015,1(38):135-139. [10] 刘东海,任勇峰,储成君. 基于FPGA控制的NAND Flash存储设计[J]. 科学技术与工程,2013,13(34):10349-10353. The Design of Invalid Block Information List Dynamic RefreshAlgorithm of High Speed and Large Capacity Data Recorder ZHANGZhiwei1,2,JINHong1,2*,LIZubo1,2,HUOXinming1,2,ZHANGRui1,2 (1.National Key Laboratory for Electronic Measurement Technology,NUC,Taiyuan 030051,China; 2.Key Laboratory of Electronic Science and Dynamic Measurement of Ministry of Education,NUC,Taiyuan 030051,China) Due to high speed and large capacity memory array for pipeline technology“invalid block information list dynamic refresh algorithm”based on FPGA is designed. The system takes the NAND Flash as the storage medium,its core is FPGA logic control,establishing a one-dimensional RAM in its interior realizing the detection information of invalid block of high speed and large capacity storage system. Simulation and feasibility analysis results show that its feasibility,The capacity of the invalid block information list established the algorithmis isn’t affected by the expansion of storage capacity. It reduces the occupation of the internal resources of FPGA,at the same time to meet the large capacity storageand don’t affect high speed storage of the system. instrument and equipment of aerocraft;high speed and large capacity;FPGA;invalid block;Flash 2016-03-21 修改日期:2016-06-30 C:7210G 10.3969/j.issn.1005-9490.2017.02.032 TP333.5 A 1005-9490(2017)02-0420-054 结束语