基于Verilog的模拟前端时序的实现方法

赵 地,朱兴华,孙 辉,杨定宇,王 进,李小辉

(成都信息工程大学 光电技术学院,四川 成都 610225)

基于Verilog的模拟前端时序的实现方法

赵 地,朱兴华,孙 辉,杨定宇,王 进,李小辉

(成都信息工程大学 光电技术学院,四川 成都 610225)

针对如何高精度、高速实现模拟前端时序的问题,提出了一种用于平板探测器的模拟前端时序的Verilog实现方法。Verilog语言的编程整体上采用模块化设计,主要包含电荷采集模块、数据读出模块和计数器模块。利用锁相环技术设置各模块不同的时钟信号,通过编写有限状态机和改进型计数器实现各模块的时序。仿真结果表明,该编程方法满足了时序高精度实现的需求,具有运行速度快、灵活性高等特点,达到了预期效果。

平板探测器;模拟前端;时序;Verilog;仿真

随着医疗技术的不断进步,X射线成像技术得到了快速发展。以往的X射线成像系统采用胶片和增感屏获取图像,具有较多的缺点,包括检测速度慢、图像质量低等[1-2]。数字X射线平板探测器(Flat Panel Detector,FPD)的出现,较好地解决了这些问题,它具有空间分辨率高、可减少X射线辐射剂量等优点,在医疗、工业等领域得到了广泛应用[3]。

因此,研制具有自主知识产权的FPD在国内非常重要。目前广泛采用的是直接型FPD[4],其主要成像过程是转换层将X射线转换成电信号,薄膜晶体管(Thin Film Transistor,TFT)阵列对电信号进行采集、存储并读出,再经放大器、A/D转换器等转变成数字图像信号,并通过显示器显示[5-6]。模拟前端用于读出TFT阵列中的电信号,并对其进行放大、采样及转换等处理。模拟前端设计的成功与否决定了FPD成像中信噪比的成败[7]。本文针对用于FPD的AFE1256(Analog Front End,AFE)模拟前端进行分析[8],着重阐述了采用Verilog语言对AFE1256时序控制的实现方法,并通过Modelsim10.1c软件进行仿真,为平板探测器的研究提供了参考。

1 时序控制的要求和总体实现思路

1.1 AFE1256的基本结构

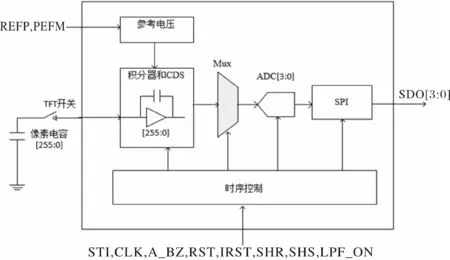

与普通模拟前端相比,AFE1256模拟前端在信号读取速度、噪声、功耗等方面进行了优化,其电路原理如图1所示[8]。

图1 AFE1256的电路原理图

从TFT阵列流入的电信号输入256个通道中,积分器对各通道电荷进行积分,经相关双采样器(CDS)采集电荷,并滤出低频噪声,再经模拟复用器(Mux)和模数转换器(ADC)输出相应的数字图像信号。每个采样电路都有两个电容器通道,当通道A采集电荷时,通道B会从之前的积分器中读取数据,此操作有助于优化帧的捕获和数据读取时间[9-10]。

1.2 时序控制的基本要求

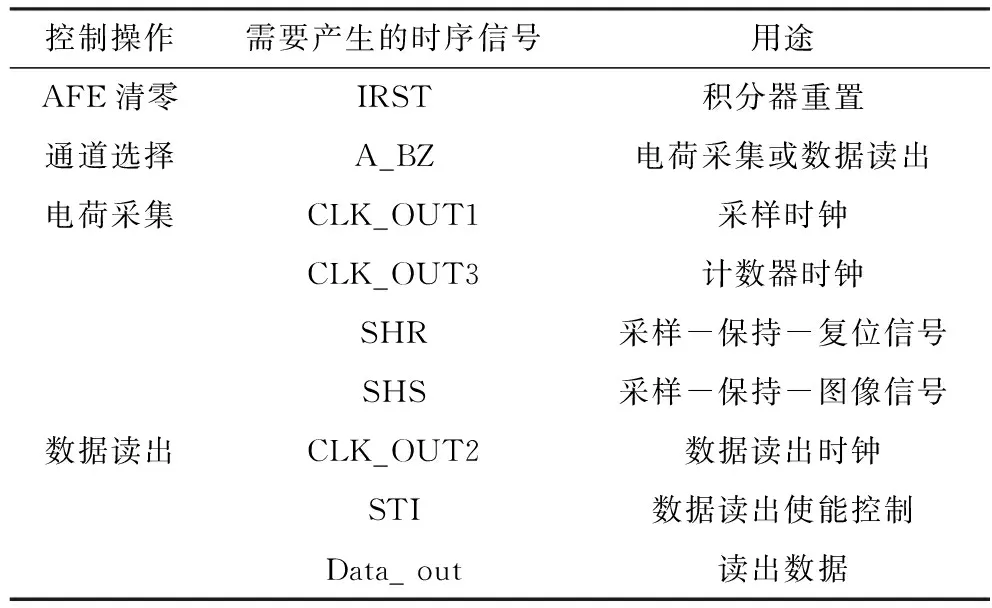

AFE1256需要实现的时序包括电荷采集时序和数据读出时序,主要工作信号如表1所示。

表1 时序产生的主要信号及其用途

X射线成像系统对AFE时序控制的基本要求如下:3种可选的时钟频率,即电荷采集时钟频率1.5 MHz(周期约583 ns)、数据读出时钟频率40 MHz(25.5 ns)以及计数器时钟频率100 MHz(10 ns);时钟扫描时间为电荷采集时钟周期的65倍;可自由设置AFE的参数,各阶段的建立、保持时间都能严格按照手册的规定值进行控制,如电荷积分时间最少为14 μs。

1.3 时序控制的总体实现思路

AFE1256时序控制的Verilog实现,具体来讲,就是实现AFE1256在电荷采集过程和数据读出过程的有效信号输出。电荷采集过程包含了电荷重置和电荷积分两部分,前者用于AFE存储区的电荷清除;后者用于正常的数据读出和成像。

根据Verilog语言自上向下的设计特点[11],本文整体结构上采用模块化设计,包含顶层模块和顶层模块下面的几个子模块。先在各个子模块中写入具体的逻辑代码,再进行子模块间的有机组合。

1.4 设计的难点及其优化方法

根据时序控制要求,数据读出和电荷采集阶段的建立时间约20 ns,远小于电荷采集时钟周期583 ns,若直接以电荷采集时钟作为系统的输入时钟,由于FPGA内部布线的传输延迟等因素,显示出的建立时间会远超过20 ns,因此设置不同的驱动时钟信号是不可缺少的。为此,本文运用锁相环技术提出了设计的优化方法[12]。将数据读出时钟频率作为输入基准时钟频率,分频至采样时钟频率,同时倍频至计数器时钟频率,100 MHz的计数器时钟能够精确的实现数据读出和电荷采集的建立时间,数据读出和电荷采集阶段可以相互不受影响的分别使用40 MHz和1.5 MHz的驱动时钟。此方法与普通的分频计数器实现方法相比,可以减少传输线路的延迟时间(控制在5 ns之内),时序的实现更加精准。时钟信号波形如图2所示。

图2 时钟信号波形图

2 时序控制的Verilog HDL实现

2.1 整体模块设计

本文在Xilinx平台ISE环境下,使用Verilog语言完成软件编程。顶层模块不能实现功能逻辑,只是完成端口的连接。以系统时钟CLK_IN1为基准输入时钟,输出3个时钟:电荷采集时钟CLK_OUT1、数据读出时钟CLK_OUT2和计数器时钟CLK_OUT3。子模块由电荷采集模块、数据读出模块和计数器模块组成,每个子模块都有独立的时钟信号及输出端口,均能实现各自的功能。

2.2 有限状态机的建模与实现

电荷采集模块和数据读出模块的时序是通过编写有限状态机来实现的。与其他方法相比,该方法能够优化芯片逻辑资源的占用,消除毛刺等[13]。在符合时序设计要求的前提下,为提高运行性能,在对状态机建模时首先考虑以下几点:(1)选用一位独热码编码结构,不需要再画状态表且电路运行快[14];(2)状态机必须完善,当外部逻辑发现异常时,状态机能够立刻恢复为初始状态;(3)采取双边沿触发的方法用以减少功率的损耗。

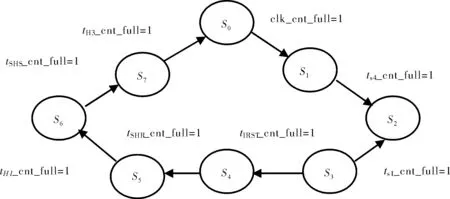

按照功能实现的先后顺序,电荷采集模块的时序可分为8个状态,分别为初始清零S0、通道等待S1、通道切换S2、复位保持S3、采样重置S4、TFT门极打开等待S5、采样信号S6、复位等待S7。同时设置相应的状态转移条件来控制各状态的有序转换,状态转移图如图3所示。

图3 状态转移图

工作过程如下:上电后,状态机进入初始状态S0,当第65个时钟上升沿到来即clk_cnt_full=‘1’时,进入通道等待状态S1;当ts4满信号标志ts4_cnt_full=‘1’时,进入通道切换S2状态;当ts1满信号标志ts1_cnt_full=‘1’时,进入复位保持S3状态,其余步骤与此类似,直到当tH3满信号标志tH3_cnt_full=‘1’时,状态机会跳转至初始态S0。

部分Verilog程序如下 :

always@(posedge clk or negedge rst_n)

if(rst_n==1'b0)begin

state <= rst;

ts4_en_cnt<= 1'b0; ……

end

else begin

case(state)

rst:

if(clk_cnt == 7'd64) begin

state <= wait_A_BZ;

ts4_en_cnt<= 1'b1;

end

else state <= rst;

wait_A_BZ:

if(ts4_cnt_full) begin

state <= A_BZ_toggle;

A_BZ <= 1'b1;

ts4_en_cnt<= 1'b0;

ts1_en_cnt<= 1'b1;

end

else state <= wait_A_BZ;

……

default:state <= rst;

endcase

end

2.3 计数器的改进

从上述过程可以发现,在一个功能模块中使用了大量计数器,且计数器满量程值这一常量(cnt_full),在不同计数器中需要设置不同的值。在功能仿真中,往往需要适当调整这个常量的值,则只能回到子模块中逐一修改数据,这势必会增加工作量且易发生疏漏。因此针对满量程值相同的计数器,使用parameter声明一个参数化常量“CNT_FULL”[15],在进行满量程修改时,直接修改parameter值,而不是逐一修改每个量程值数字。

除此之外,对于量程不同的多个计数器,一般使用的方法是把代码复制得到多个计数器文件,并修改parameter为所需的值,此种方式虽能避免一个常量值在多个计数器中被多次使用,但仍需多个计数器子模块,未能大幅减少工作量。因此,在顶层模块例化计数器子模块时,直接在例化的过程中修改计数器模块的参数值,使用defparam来重新定义CNT_FULL的值[7]。如本文中进行参数化设计为

defparam ts4_cnt.CNT_FULL=2

这里ts4_cnt是被例化的模块名字,CNT_FULL是ts4_cnt模块中需要修改的参数的名字,当使用defparam修改参数值后,原始文件的默认参数值会被忽略,CNT_FULL值就是2。这种参数化实现方式有效减少了工作量。

3 仿真结果及分析

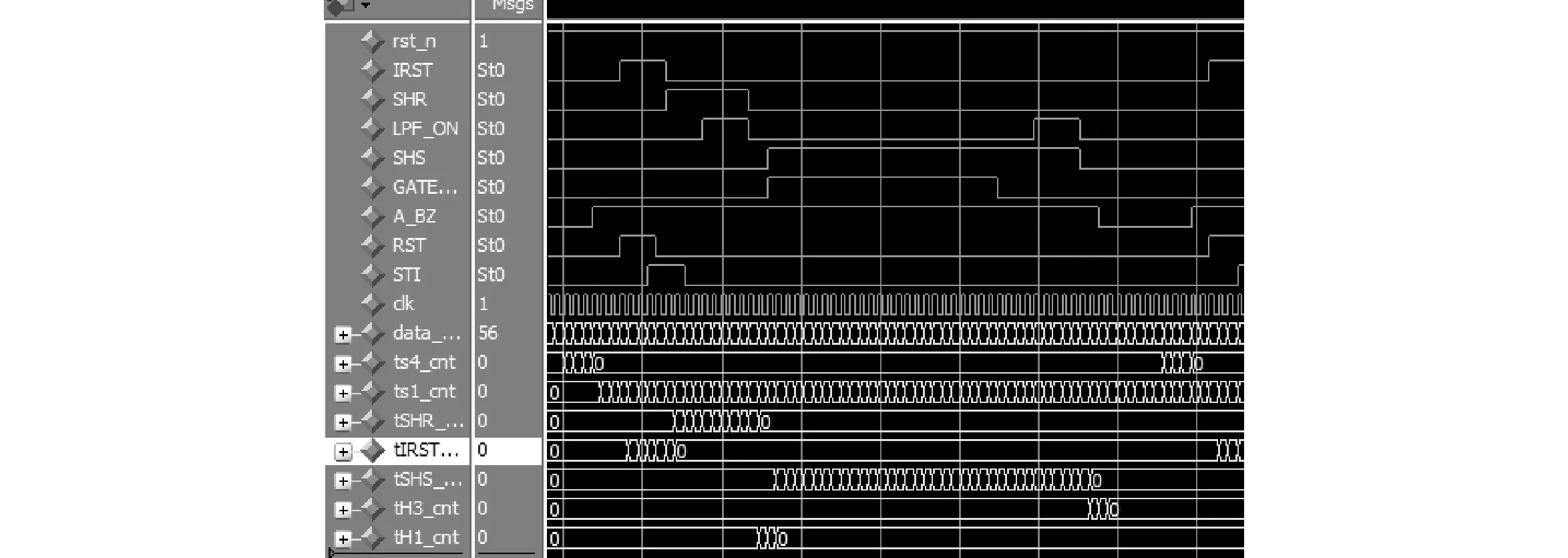

利用仿真软件Modelsim10.1c对编写的Verilog程序进行仿真,仿真结果如图4所示。从图中可知,Modelsim仿真和预期结果相符,所以Verilog程序准确。

图4 AFE1256时序仿真结果图

下面对仿真结果进行分析。电荷采集阶段的波形图是最复杂的,也是整个AFE1256时序控制的关键。当第65个时钟上升沿来临时,进入A_BZ通道等待状态,经过A_BZ切换的建立时间ts4,切换到A通道开始信号采样和B通道开始输出数据的模式;接着经过IRST的建立时间ts1,AFE1256进入复位阶段,开始重置信号;在复位阶段,数据输出使能端STI开始驱动一个数据的读出,该数据是由先前的积分器所采集;经过时间tIRST复位结束,系统开始采样背景噪声,经过tD1的延迟时间,系统受到低通滤波器(LPF)带宽的限制,开始积分漏电流,再经过时间tSHR采样背景噪声结束。这时经过tH1的保持时间后,TFT门极打开,向AFE1256输入电荷信号,系统开始积分采集来的电荷,经过至少14 μs的积分时间后,TFT门极关断,共经过65个时钟周期,系统会跳至初始状态开始下一个数据的扫描。

4 结束语

本文采用Verilog语言进行硬件描述,实现了用于平板探测器的高性能模拟前端的时序控制,通过采用锁相环的方法,实现了时钟信号延迟的灵活、有效控制。通过改进计数器并结合有限状态机的方法,使时序的控制更加高效和精准。功能仿真结果表明,这种实现时序控制的方法满足了用于平板探测器的模拟前端的逻辑和时序控制要求,为用于平板探测器的模拟前端设计提供了参考。

[1] 范雄.金属X射线学[M].北京:机械工业出版社,1996.

[2] Kasap S O,Rowlands J A.Direct conversion flat panel X-ray image detectors[J]. IEEE Proceeding of Circuits DevicesSyst,2002,4(2):149-150.

[3] Sylvie,Chapuy,Marc.Real-time flat panel pixel imaging systerm and control for X-ray and neutron detection[J].IEEE Transactions on Nuclear Science,2001,48(6):3-35.

[4] 任鹏举.平板探测器技术综述[J].仪器仪表学报,2008,8(1):1-4.

[5] 王远,许州,陈浩.基于平板探测器的高能工业CT数据采集系统[J].CT理论与应用研究,2006,7(3):3-4.

[6] 肖永顺.基于数字平板探测器的高能X射线成像实验研究[J].光学技术,2003,29(6):660-663.

[7] 王鹏程,张富利.数字化X线平板探测器的研究进展[J].医疗卫生装备,2004,2(1):26-27.

[8] Texas Instruments.AFE1256+NDA+Protected[EB/OL].(2015-04-04)[2016-04-12]http:∥www.ti.com.cn/tihome/cn/docs/homepage.tsp.

[9] 严志刚.高分辨率CCD模拟前端系统设计[J].航天控制,2010,28(2):89-90.

[10] 徐磊.基于FPGA的CCD模拟器采集系统的设计[J].电子测量技术,2014,37(8):112-114.

[11] 夏宇闻.Verilog数字系统设计教程[M].北京:北京航空大学出版社,2003.

[12] 但慧明.锁相环的研究与设计[D].无锡:江南大学,2011.

[13] Michael D Ciletti.Verilog HDL高级数字设计[M].北京:电子工业出版社,2005.

[14] Bhasker J.Verilog HDL synthesis a practical primer[M].北京:清华大学出版社,2004.

[15] Zhao J, Chen W, Wei S. Parameterized IP core design[C].Shanghai:International Conferenceon Asic Proceedings,2001.

Implement of Analog Front end Timing by Verilog

ZHAO Di,ZHU Xinghua,SUN Hui, YANG Dingyu,WANG Jin,LI Xiaohui

(School of Optoelectronic Technology, Chengdu University of Information Technology, Chengdu 610225, China)

A method of Verilog realization of the analog front end timing used in the flat panel detector is proposed for the implement with high precision and high speed of analog front end timing. Verilog programming uses of modular design including charge collection module, data reading module and counter module on the whole. Each module is set different clock signal by phase locked loop technique, and achieved by writing finite state machine and improved counter. The simulation results show that the method meets the requirements of realizing the timing with high precision, and achieves the desired effect with fast speed and high flexibility.

flat panel detector;analog front end;timing;Verilog;simulation

2016- 06- 03

四川省科技支撑计划基金资助项目(2014GZ0020, 2014GZX0012, 2015GZ0194, 15ZB0173, 2016FZ0018)

赵地(1993-),女,硕士研究生。研究方向:电子与通信工程。

10.16180/j.cnki.issn1007-7820.2017.04.036

TP311.1

A

1007-7820(2017)04-144-04