基于NiosII的CZT频谱细化算法仿真实现

朱怀毅

(长沙理工大学 电气与信息工程学院,湖南 长沙 410000)

基于NiosII的CZT频谱细化算法仿真实现

朱怀毅

(长沙理工大学 电气与信息工程学院,湖南 长沙 410000)

文中介绍了线性调频Z变换(CZT)的原理,针对工程中对CZT频谱细化算法实现难的问题,提出了一种嵌入式处理器(NiosII软核)设计方法,结合Nios IDE平台,在FPGA开发版上进行仿真实验,实现了在指定频率范围内对某电力基频信号的CZT频谱细化分析。实验表明,该方法具有设计简单、可靠性高、实现效果好等特点,具有一定的实用价值。

线性调频Z变换; NiosII软核; Nios IDE; FPGA

频谱细化[1]是信号分析中的重要手段之一。它能以指定的、足够高的分辨率分析频率轴上任一窄带内信号的频谱结构。直接在细化频带内致密取值,增加频率点数,并计算出相应的频谱值,这就是具有代表性的基于线性调Z变换(Chirp Z Transform,CZT)的频谱细化算法。由于在FPGA[2]中不能处理小数综合,被处理的数据必须是整数,近年来如文献[3]在FPGA上实现CZT频谱细化算法一般都是采用Altera公司自带的IP核,以IP核为主要设计方案建立CZT算法的核心步骤,但CZT算法中会遇到很多小数,所以用IP核的设计方式必须把小数量化成整数来处理,采用量化定点方式会引起很多误差,加大运算量,精确度也有所下降。故此设计采用SOPC Builder建立NiosII软核的方式,再在Nios IDE中运用C语言以便进行小数运算。通过CZT算法得到频谱细化值后将结果送入TFT LCD800×600的彩屏上显示,从而直观的查看仿真结果。此设计所使用的软件为:QuartusII 9.0和NiosII IDE 9.0。开发平台为LTE-SOPC-02FD EDA/SOPC实验箱,所用FPGA芯片为Altera公司的EP3C80F780C8。

1 CZT算法

CZT算法原理。设A/D采样信号为x(n),其Z变换[4]为

(1)

在z平面内,变量z可以沿更一般的路径取值,设z的取样点为

zk=AW-k(k=0,1,…,M-1)

(2)

式中,M为要分析的复频谱点数,可不等于N;A和W是任一复数,可表示为

A=A0ejθ0

(3)

W=W0e-jφ0

(4)

式中,A0为起始取样点z0的矢量半径长度,CZT中A0=1,表示在单位圆上的取值;θ0为起始取样点z0的相角,即选取频率范围的起点;φ0为两相邻zk点之间角频率差,即选频范围内的频率分辨率。W0=1,使得计算周线在单位圆上进行;M=N,使得CZT便于计算。所以,通过调整θ0来确定选频范围的起点;通过调整φ0来确定选频范围内频谱细化倍数。将式(2)带入式(1),可得

(5)

将等式

(6)

代入式(5),可得

(7)

设

(8)

(9)

则式(7)可写为

(10)

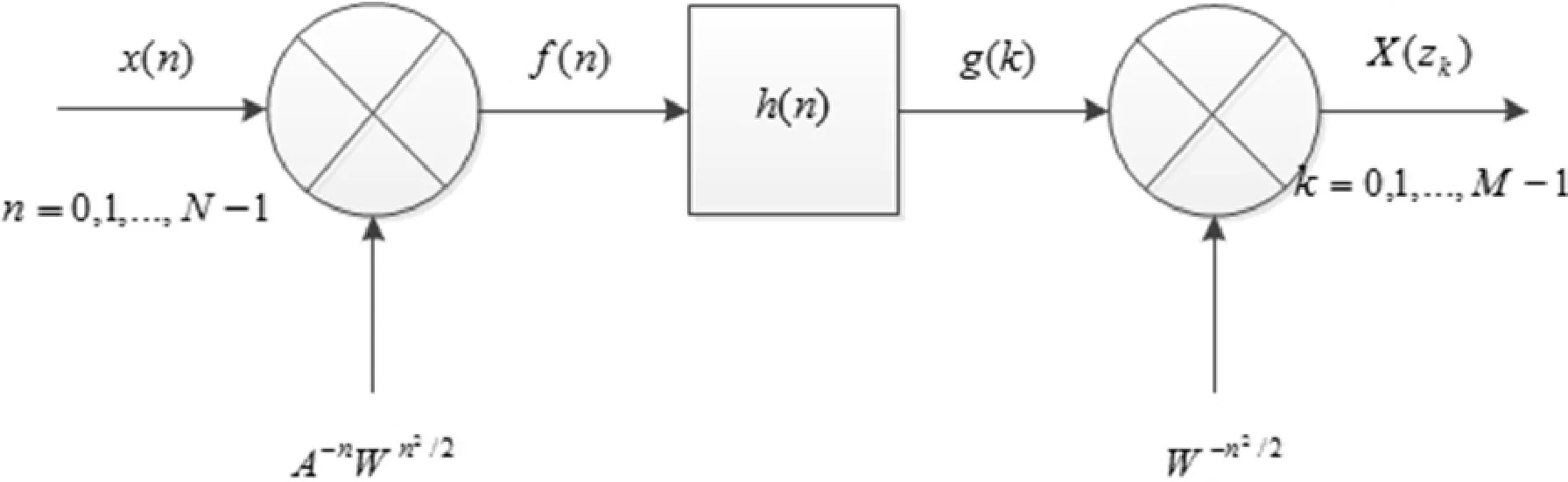

式(10)可用图1表示。

图1 CZT的系统框图

其中,f(n)与h(n)的适当段的圆周卷积[5]来表示

(11)

(12)

有限长序列的圆周卷积可采用FFT[6-8]快速计算,分别用FFT求出序列f(n)和h(n)的L点DFT,即F(r)和H(r)。将H(r)和F(r)相乘得到的结果定义为Q(r),Q(r)为L点频率离散序列。用FFT法求Q(r)的L点IDFT即为f(n)和h(n)的圆周卷积。

2 CZT算法的硬件实现

2.1 设计流程

NiosII[9]的设计流程分为硬件开发和软件开发两部分。硬件开发包括NiosII组件模型建立及配置,NiosII硬件系统的生成。软件开发包括FPGA下载配置,建立软件工程并运行测试。其主要设计方案是在Quartus II[10]中设计并生成SOPC系统[11],再通过Nios IDE进行软件程序设计。因此整个NiosII设计流程图可以归纳如图2所示。

图2 NiosII的设计流程图

2.2 系统硬件设计

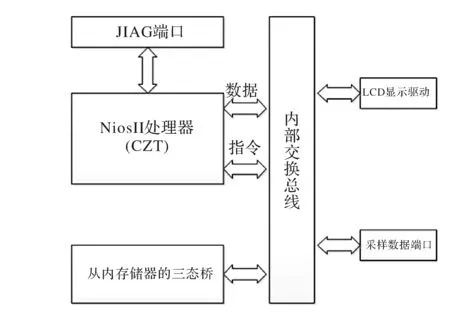

利用Quartus II的SOPC Builder组件进行软核的设计,在搭建软核[12]前首先设置目标FPGA及时钟,由于凌特公司的开发平台是50 MHz的时钟信号,所以设置时钟频率为50 MHz。软核的设计步骤如下:(1)CPU设计。展开Altera SOPC Builder选取NiosII Process,添加NiosII内核,此次选择NiosII/f内核的CPU;(2)展开System Contens列表中interface Protocols类中的Serial选项,选取JTAG UART,添加JTAG UART来作为输入输出终端;(3)展开System Contens列表中的Bridgesand Adapters类中的Memory Mapped选项,选择Avalon—MM Tristate Bridge,添加CPU外设的总线桥;(4)加入外部SRAM存储器,接口选择存储量为1 024 KB,用来运行程序和保存数据;(5)选择System Contents列表中的Memories and Memory Controllers选项,选取Flash Memory(CFI),添加Flash控制器;(6)添加通信PIO端口用于控制采样数据的输入和LCD显示屏的输出。至此,软核设计已完成,编译生成SOPC系统。加入指定的ROM IP核[13]存储模块和时钟模块,采用原理图设计方法连接好各模块,最后生成顶层文件,顶层文件编译成功之后通过JTAG数据线下载到FPGA开发版上。图3为系统硬件设计模块图。以下将开始为此系统进行工程项目软件设计和调试,如果发现NiosII嵌入式系统的CPU内核软硬件工作情况不能完全满足设计要求,可修正或更改设计,这是SOPC系统的一大优势。

图3 系统硬件设计模块图

2.3 系统软件设计

在NiosII软核配置系统完成并下载于FPGA中的基础上,进入集成开发环境IDE进行软件开发,下载和调试。利用SOPC生成的系统库函数,结合C语言[14]编程,调用HAL底层驱动函数来访问硬件层从而达到对数据的传输与处理。软件设计的主要步骤就是编写CZT的C语言算法。因此根据上述CZT算法原理进行了该算法的编写,所用核心程序如下:

#include "system.h"

#include"altera_avalon_pio_regs.h"

#include

#include

#include

#include "Complex.h"

#include "FFT.h"

#include "alt_types.h"

#include "lcd.h"

…………

将编写好的程序进行编译,同样通过JTAG数据线下载到FPGA上完成系统软件设计。

2.4 仿真和硬件实施结果

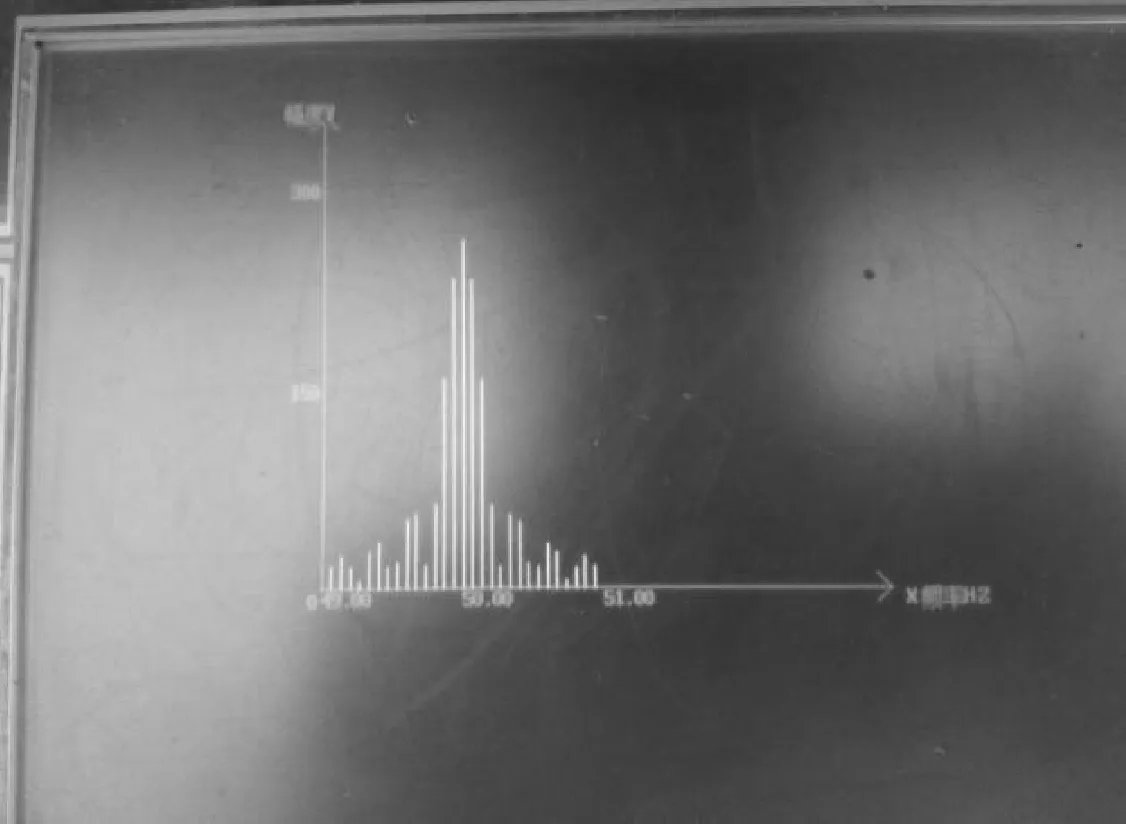

上面已经搭建好硬件和软件系统的连接,下面进行CZT算法的调试。以工程项目中电力系统基频x(t)=cos(2π×50t)为待测频谱分析信号,定义采用频率为128 Hz,采样512个数据,选取频段49~51 Hz之间30倍频谱细化。由于条件限制,此次数据的采样不使用A/D转换器,直接在Matlab[15]中模拟生成,然后存入Quartus II中的ROM IP核中,接着利用已设计好的SOPC系统进行CZT频谱分析算法的硬件仿真。图4为硬件仿真结果,幅度最大值对应的频率为50 Hz即为该基频信号的频率,图5为Matlab仿真结果。

图4 硬件仿真结果

图5 Matlab仿真结果

3 结束语

从实验结果来看,利用NiosII软核技术实现CZT频谱细化算法有较高的可行性,设计简单,能较好的分析电力系统基频信号。同时其具有在线可编程能力,能在不改动任何硬件条件下对系统进行修改和升级,以便扩展新功能,这将为数字信号处理领域带来便利。

[1] 丁康,张晓飞.频谱校正理论的发展[J].振动工程学报,2003,3(1):14-22.

[2] 李宪强.FPGA项目开发实战讲解[M].北京:电子工业出版社,2015.

[3] 王磊磊,陈潜.基于CZT的频率细化方法的FPGA实现[J].制导与引信,2010,31(1):29-32.

[4] 张辉.一种电力系统测频方法—CZT算 法[J].现代电力,2005,22(3):21-23.

[5] 吴小平.利用圆周卷积离散谱快速线性卷积[J].凯里学院报,2009,27(3):16-17.

[6] 刘顺兰,吴杰.数字信号处理[M].2版.西安:西安电子科技大学出版社,2009.

[7] 钟佑明,汤宝平,秦树人.离散傅里叶变换计算中的一些问题的的论证[J].重庆大学学报,2001,24(3):1-4.

[8] 何方白,张德民.数字信号处理[M].北京:高等教育出版社,2009.

[9] 周立功.SOPC嵌入式系统基础教程[M].北京:北京航天航空大学出版社,2006.

[10] 潘松,黄继业.EDA技术使用教程VHDL 版[M].4版.北京:科学出版社,2010.

[11] 方茁,陈卓文,彭澄廉.SOPC设计中的用户自定义逻辑[J].计算机工程,2004,30(17):42-44.

[12] 候建军,郭勇.SOPC技术基础教程[M].北京:清华大学出版社;北京交通大学出版社,2008.

[13] 张春生,苏开友.FPGA数字信号处理 与工程应用实践[M].北京:中国铁道出版社,2013.

[14] 程军.Intel80cp16单片机应用实践与C语言开发[M].北京:北京航空航天大学出版社,2002.

[15] 刘卫国.Matlab程序设计与应用[M].2版.北京:高等教育出版社,2006.

The Simulation Implementtation of CZT Spectrum Zooming Algorithm Based on NiosII

ZHU Huaiyi

(School of Electrial and Information Engineering,Changsha University of Science&Technology,Changsha 41000,China)

The principle of chirp Z transform (CZT) is presented. To solve the difficult problems of realizing CZT spectrum zooming algorithm in engineering programmes, a design method of a kind of embedded processor (Nios II soft core) is proposed, using Nios IDE platform, simulation experiment is processed on the FPGA development board to achieve the CZT spectrum zooming analysis of a certain power fundamental frequency signal in the specified frequency range. Experiment results show that the method has characteristics of simply designed ,high reliability, achieving of good effect,it has a good practical value.

chirp Z transform;Nios II soft core;Nios IDE;FPGA

2016- 06- 10

朱怀毅(1991-),男,硕士研究生。研究方向:信号检测与处理。

10.16180/j.cnki.issn1007-7820.2017.04.019

TP301.6

A

1007-7820(2017)04-076-03