一种低噪声交叉耦合结构集成石英晶体振荡器

谢海情+曾承伟+曾健平+唐俊龙+贾新亮+彭永达+王超

摘 要:通过改进电路结构,采用CMOS交叉耦合结构提供负阻,设计一种20 MHz的集成石英晶体振荡器.在该振荡器中,采用共模反馈使其输出稳定的直流电平,并增加RC高通滤波器和预抑制电路降低其相位噪声.基于NUVOTON 0.35 μm CMOS工艺,利用Cadence Spectre对电路进行仿真,结果表明,在电源电压为3.3 V,偏置电流约400 μA时,该振荡器的起振时间约为1.5 ms,输出波形峰峰值为1.08 V,输出直流电平约为801.6 mV.输出信号频率为19.95 MHz,相位噪声分别可以达到-155 dBc/Hz@1 kHz,-164 dBc/Hz@10 kHz.

关键词:晶体振荡器;相位噪声;交叉耦合;RC高通滤波

中图分类号:TN432 文献标志码:A

A Low Noise Cross-coupled Integrated Quartz Crystal Oscillator

XIE Haiqing1, ZENG Chengwei1, ZENG Jianping2, TANG Junlong1,

JIA Xinliang1, PENG Yongda1, WANG Chao1

(1. School of Physics & Electronic Science, Changsha University of Science & Technology, Changsha 410114,China;

2. College of Physics and Microelectronics Science, Hunan University, Changsha 410082,China)

Abstract:By improving the circuit structure and adopting the CMOS cross-coupled structure to provide negative resistance, a 20 MHz integrated quartz crystal oscillator was proposed. In this oscillator, the common-mode feedback was adopted to achieve stable DC output, and the RC high filter circuit and the pre-rejection circuit were designed to reduce the phase noise. With NUVOTON 0.35 μm CMOS process, the circuit was designed and simulated by the Spectre in Cadence. Under the supply voltage of 3.3 V and the bias current of 400 μA, the results indicated that start-up time of the oscillator was about 1.5 ms, the peak value of the output waveform was 1.08 V, the DC output was about 801.6 mV, the frequency of output was 20 MHz, and the phase noise reaches -155 dBc/Hz@1 kHz and -164 dBc/Hz@10 kHz, respectively.

Key words:crystal oscillator; phase noise; cross-coupled; RC high pass filter

在全球定位系统、通信、导航、时间与频率计量等领域,晶体振荡器作为系统的基准参考频率源,一直是一个不可缺少的器件.随着信息技术的快速发展,对基准频率源的精确度、稳定度提出了越来越高的要求.相位噪声作为信号源的重要参数指标之一,对通信设备的性能有着重要意义[1].目前,石英晶体振荡器主要由分立元器件组成.常见的三点式石英晶体振荡器主要有以下3种:皮尔斯(Pierce)振荡器,科尔皮兹(Colpitts)振荡器和克拉普(Clapp)振荡器[2-4].杨骁等人[5]对三点式振荡器的起振条件和相位噪声进行了详细分析,提出了一种带增益控制环路的振荡电路,降低了起振时间,并提高振荡器的相位噪声性能.在晶体振荡电路中,振荡器的相位噪声是振荡器性能的关键参数.唐路等人[6]提出了一种PMOS差分结构降低相位噪声.Siwiec[7]提出了一種双反馈回路结构降低相位噪声.Wang等人[8-9]利用噪声模型指导低噪声振荡电路的设计.三点式振荡器虽然在结构、可靠性和噪声性能等方面具有优势,但是只能输出单端信号.差分电路结构在调节线性度、共模噪声抑制、环境噪声抑制以及电源噪声抑制等方面都有明显优势,在压控振荡器中应用广泛.本文基于差分对称输出的交叉耦合结构,并增加共模反馈模块和RC滤波模块,设计一种低相位噪声交叉耦合结构的集成石英晶体振荡器.

1 传统石英晶体振荡器电路分析

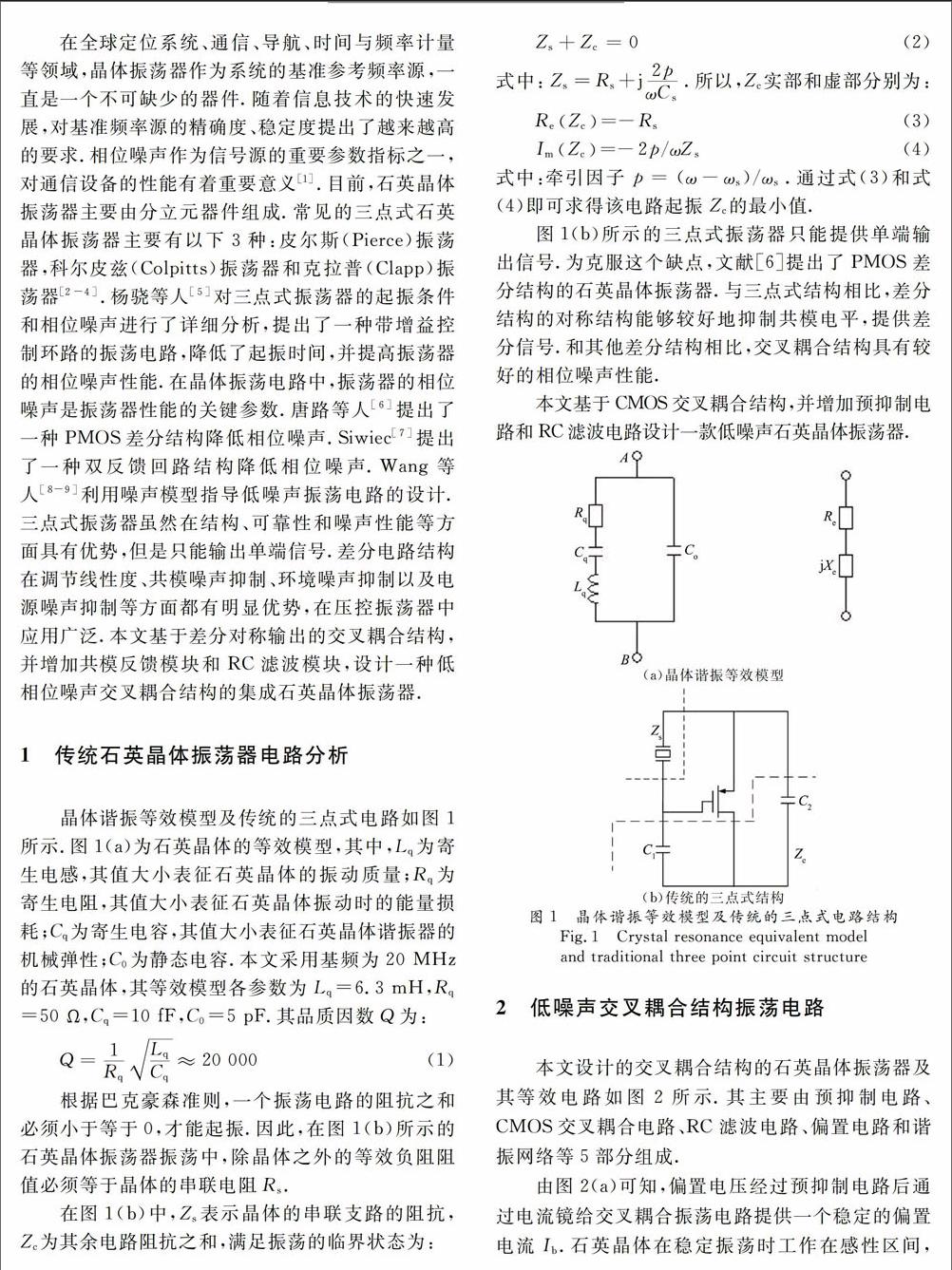

晶体谐振等效模型及传统的三点式电路如图1所示.图1(a)为石英晶体的等效模型,其中,Lq为寄生电感,其值大小表征石英晶体的振动质量;Rq为寄生电阻,其值大小表征石英晶体振动时的能量损耗;Cq为寄生电容,其值大小表征石英晶体谐振器的机械弹性;C0为静态电容.本文采用基频为20 MHz的石英晶体,其等效模型各参数为Lq=6.3 mH,Rq=50 Ω,Cq=10 fF,C0=5 pF.其品质因数Q为:

Q=1RqLqCq≈20 000 (1)

根据巴克豪森准则,一个振荡电路的阻抗之和必须小于等于0,才能起振.因此,在图1(b)所示的石英晶体振荡器振荡中,除晶体之外的等效负阻阻值必须等于晶体的串联电阻Rs.

在图1(b)中,Zs 表示晶体的串联支路的阻抗,Zc为其余电路阻抗之和,满足振荡的临界状态为:

2 低噪声交叉耦合结构振荡电路

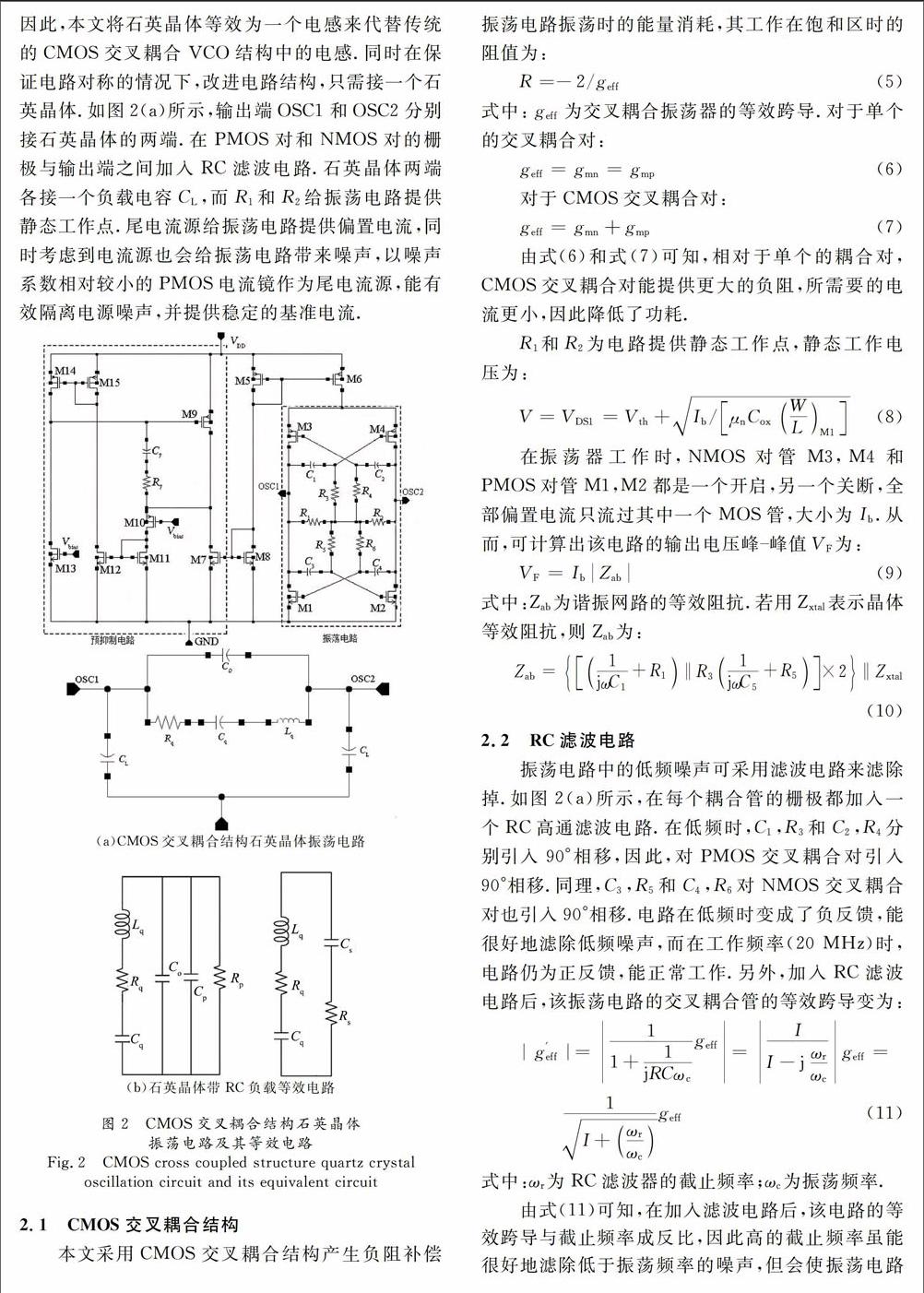

本文设计的交叉耦合结构的石英晶体振荡器及其等效电路如图2所示.其主要由预抑制电路、CMOS交叉耦合电路、RC滤波电路、偏置电路和谐振网络等5部分组成.

由图2(a)可知,偏置电压经过预抑制电路后通过电流镜给交叉耦合振荡电路提供一个稳定的偏置电流Ib.石英晶体在稳定振荡时工作在感性区间,因此,本文将石英晶体等效为一个电感来代替传统的CMOS交叉耦合VCO结构中的电感.同时在保证电路对称的情况下,改进电路结构,只需接一个石英晶体.如图2(a)所示,输出端OSC1和OSC2分别接石英晶体的两端.在PMOS对和NMOS对的栅极与输出端之间加入RC滤波电路.石英晶体两端各接一个负载电容CL,而R1和R2给振荡电路提供静态工作点.尾电流源给振荡电路提供偏置电流,同时考虑到电流源也会给振荡电路带来噪声,以噪声系数相对较小的PMOS电流镜作为尾电流源,能有效隔离电源噪声,并提供稳定的基准电流.

2.1 CMOS交叉耦合结构

本文采用CMOS交叉耦合结构产生负阻补偿振荡电路振荡时的能量消耗,其工作在饱和区时的阻值为:

R=-2/geff (5)

式中:geff为交叉耦合振荡器的等效跨导.对于单个的交叉耦合对:

geff=gmn=gmp (6)

对于CMOS交叉耦合对:

geff=gmn+gmp (7)

由式(6)和式(7)可知,相对于单个的耦合对,CMOS交叉耦合对能提供更大的负阻,所需要的电流更小,因此降低了功耗.

R1和R2为电路提供静态工作点,静态工作电压为:

V=VDS1=Vth+Ib/μnCoxWLM1(8)

在振荡器工作时,NMOS对管M3,M4和PMOS对管M1,M2都是一个开启,另一个关断,全部偏置电流只流过其中一个MOS管,大小为Ib.从而,可计算出该电路的输出电压峰峰值VF为:

VF=IbZab (9)

式中:Zab为谐振网路的等效阻抗.若用Zxtal表示晶体等效阻抗,则Zab为:

Zab=1jωC1+R1‖R31jωC5+R5×2‖Zxtal (10)

2.2 RC滤波电路

振荡电路中的低频噪声可采用滤波电路来滤除掉.如图2(a)所示,在每个耦合管的栅极都加入一个RC高通滤波电路.在低频时,C1,R3和C2,R4分别引入90°相移,因此,对PMOS交叉耦合对引入90°相移.同理,C3,R5和C4,R6对NMOS交叉耦合对也引入90°相移.电路在低频时变成了负反馈,能很好地滤除低频噪声,而在工作频率(20 MHz)时,电路仍为正反馈,能正常工作.另外,加入RC滤波电路后,该振荡电路的交叉耦合管的等效跨导变为:

|g′eff|=11+1jRCωcgeff=II-jωrωcgeff=

1I+ωrωcgeff(11)

式中:ωr为RC滤波器的截止频率;ωc为振荡频率.

由式(11)可知,在加入滤波电路后,该电路的等

效跨导与截止频率成反比,因此高的截止频率虽能很好地滤除低于振荡频率的噪声,但会使振荡电路难以起振.经仿真折衷,取截止频率为10 MHz,R3= R4 =R5 =R6=5 kΩ,C1=C2=C3=C4=3 pF.

2.3 谐振网络

石英晶体的高Q值是保证晶体振荡器低相位噪声的根本条件.当谐振器接入振荡电路后,会引入附加损耗,使谐振器的有载Q值降低.图2(a)所示的振荡电路可等效为石英晶体带RC负载的谐振网络,如图2(b)所示.其中,输出阻抗Rp=2Rin(Rin为OSC1的等效输入电阻),Cp=CL/2(CL为负载电容).将Rp和C0+Cp由并联改为串联后,等效电阻和等效电容分别为:

Rs=Rp1+ω2c(Co+Cp)2R2p(12)

Cs=1+ω2c(Co+Cp)2R2pω2c(Co+Cp)2R2p(13)

则有载品质因数Qe为:

Qe=ωcLq/(Rs+Rq) (14)

将式(12)代入式(14),可得有载Q值与负阻的关系为:

Qe=ωcLq+Lqω3c(Co+Cp)2R2pRp+Rq+Rqω2c(Co+Cp)2R2p

(15)

根据式(15)可知,电路的有载Qe值随输出阻抗增大而增大,因此可通过增大电路的输出阻抗Rp来提高Qe值.而CMOS交叉耦合结构的输出阻抗为:

Rp=ron‖rop‖1gmn+gmn(16)

由式(16),可以得出:

Rp∝1(W/L) (17)

由公式(15)和(17)可知,电路有载Qe值随MOS管的宽长比的增大而减小.但MOS管的宽长比减小会导致其跨导减小,不仅使提供的负阻较小,而且使电路难以起振.根据计算和仿真,本文取NMOS管的宽长比为(W/L)n=140/3,PMOS管的宽长比为(W/L)p=320/1.5.

通过式(12)也可看出,增加石英晶体的负载电容也可以增加电路的有载Q值,但负载电容过大会导致电路频率的偏移和难以起振,经仿真折衷,我们取负载电容值CL=30 pF.

2.4 预抑制电路

为了更一步降低电源噪声,抑制电源纹波,我们增加了预抑制电路.如图2(a)所示,預抑制电路由PMOS管M9,M10,M14,M15;NMOS管M11,M12,M13;电容C7和电阻R7组成.

在預抑制电路中,M10可以将VGS10钳位在阈值电压附近,M11,M12,M13,M14,M15,M9和M10构成反馈调节电路.当Vbias增大时,M9的过驱动电压由于反馈而减小,该反馈环路的直流开环增益很大,从而将偏置电压Vbias钳位到一个恒定的值,使得Vbias随电源电压变化非常小.C7和R7构成密勒补偿电路稳定该反馈环路,通过设置合适的元件参数可以极大地抑制尾电流源的噪声.

3 版图设计与仿真分析

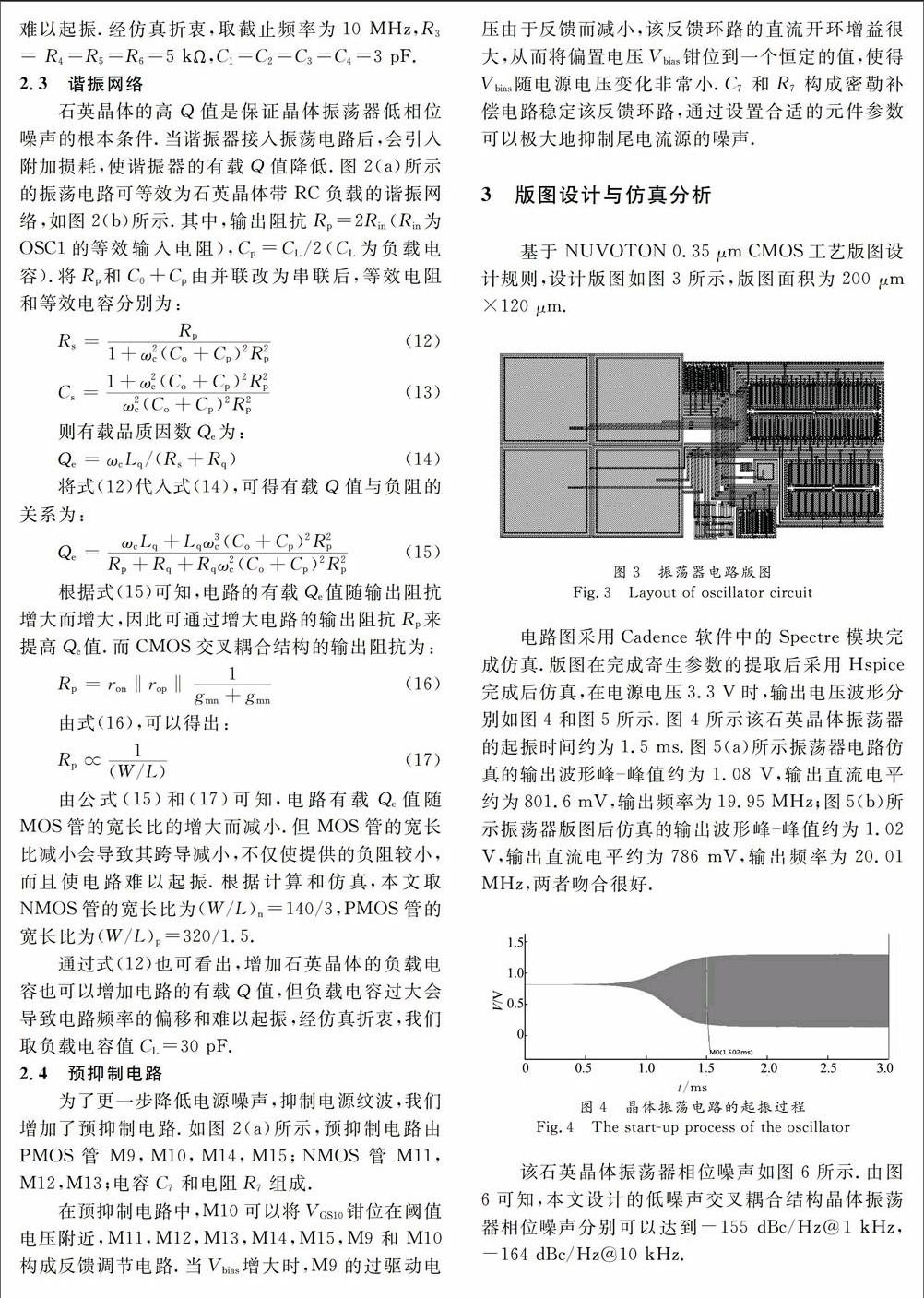

基于 NUVOTON 0.35 μm CMOS工艺版图设计规则,设计版图如图3所示,版图面积为200 μm×120 μm.

电路图采用Cadence 软件中的Spectre模块完成仿真.版图在完成寄生参数的提取后采用Hspice完成后仿真,在电源电压3.3 V时,输出电压波形分别如图4和图5所示.图4所示该石英晶体振荡器的起振时间约为1.5 ms.图5(a)所示振荡器电路仿真的输出波形峰峰值约为1.08 V,输出直流电平约为801.6 mV,输出频率为19.95 MHz;图5(b)所示振荡器版图后仿真的输出波形峰峰值约为1.02 V,输出直流电平约为786 mV,输出频率为20.01 MHz,两者吻合很好.

该石英晶体振荡器相位噪声如图6所示.由图6可知,本文设计的低噪声交叉耦合结构晶体振荡器相位噪声分别可以达到-155 dBc/Hz@1 kHz,-164 dBc/Hz@10 kHz.

表1给出了本文设计的石英晶体振荡器的相位噪声与其他文献的对比.从表1中可以看出,该石英晶体振荡器由于采用CMOS交叉耦合结构,以及增加了RC滤波电路和预抑制电路,使该振荡器的相位噪声良好,尤其在低频处相位噪声有较大的改善.

4 结 论

本文基于NUVOTON 0.35 μm CMOS工艺,采用共模反馈和RC高通滤波模块,提高输出直流电平的稳定性和输出波形的对称性,并增加预抑制电路降低相位噪声,实现了一种具有差分输出的低相位噪声CMOS交叉耦合石英晶体振荡器.在电源电压为3.3 V,偏置电流为400 μA时,该振荡器的起振时间约为1.5 ms,输出19.95 MHz的稳定频率信号,两路输出信号波形具有良好的对称性,峰峰值约为1.08 V,输出直流电平约为801.6 mV.相位噪声分别可以达到-155 dBc/Hz@1 kHz,-164 dBc/Hz@10 kHz.

参考文献

[1] 刘利辉,曾健平,张智.100 MHz低噪声恒温石英晶体振荡器研制[J]. 湖南大学学报:自然科学版,2009,36(4):53-56.

LIU Lihui, ZENG Jianping, ZHANG Zi. Development of 100 MHz low noise constant temperature quartz crystal oscillator [J]. Journal of Hunan University: Natural Sciences, 2009, 36 (4):53-56. (In Chinese)

[2] IGUCHI S,FUKETA H,SAKURAI T, et al. Variation-tolerant quick-start-Up CMOS crystal oscillator with chirp injection and negative resistance booster[J]. IEEE Journal of Solid-State Circuits,2016,51(2):496-508.

[3] 武振宇,马成炎,叶甜春.一种低功耗快速起振晶体振荡器[ J].微电子学,2010,40(1):45-49.

WU Zhenyu, MA Chengyan, YE Tianchun. A low power consumption fast oscillating crystal oscillator[J]. Microelectronics,2010,40(1):45-49. (In Chinese)

[4] ZHAO Wei, LU Lei, TANG Zhangwen. A low-phase noise digitally controlled crystal oscillator for DVB TV tuners[J]. Journal of Semiconductor,2010,31(7):1-6.

[5] 杨骁,齐骋,王亮,等.一种低相位噪声CMOS晶体振荡器的设计[J].微电子学,2012,42(5):642-645.

YANG Xiao, QI Cheng, WANG Liang, et al. Design of a low phase noise CMOS crystal oscillator[J]. Microelectronics,2012,42(5):642-645.(In Chinese)

[6] 唐路,王志功,曾贤文,等.一种用于射频调谐器的低相位噪声低功耗晶体振荡器[J].东南大学学报:英文版,2012,28(1):21-24.

TANG Lu, WANG Zhigong, ZENG Xianwen, et al. A low-phase-noise and lower-power crystal oscillator for RF tuner[J]. Journal of Southeast University:English Edition,2012, 28(1):21-24.

[7] SIWIEC K. Crystal oscillator with dual amplitude stabilization feedback loop[C]//Proceedings of the 19th International Conference Mixed Design of Integrated Circuits and Systems (MIXDES).Warsaw, Poland: Institute of Electrical and Electronics Engineers, Inc,2012:231- 234.

[8] WANG Yan, HUANG Xianhe.Analysis and design of low phase noise crystal oscillators[C]//Proceedings of 2012 IEEE International Conference on Mechatronics and Automation.Chengdu, China: Institute of Electrical and Electronics Engineers, Inc,2012:19-23.

[9] HUANG Xianhe,CHEN Pingping, FU Wei,et al. Prediction, simulation, and verification of the phase noise in 80 MHz low-phase-noise crystal oscillators[J].IEEE Transactions on Ultrasonics, Ferroelectrics and Frequency Control, 2015, 62(9): 1599-1604.