基于FPGA的UDP点对点传输协议实现

付高原,郭 臣,潘进勇,施 雪

(河海大学 计算机与信息学院,江苏 南京211100)

基于FPGA的UDP点对点传输协议实现

付高原,郭 臣,潘进勇,施 雪

(河海大学 计算机与信息学院,江苏 南京211100)

基于提升数据传输速率,提高数据传输实时性的目的,提出了一种基于UDP协议的点到点数据传输方案,并采用现场可编程逻辑门整列(FPGA)和以太网PHY芯片RTL8211EG实现点到点的UDP高速数据传输。通过对比传统TCP/IP协议的工作原理,并结合相应的理论分析,得出该系统在数据传输速率上具有一定的优势,且系统复杂度低,便于实现的结论。

UDP;FPGA;点到点;高速数据传输

随着高清视频影像,及视频监控等领域的需求越来越大,涉及高清视频,音频等大数据量数据传输的应用项目越来越多,在这一类对实时性及传输速率有一定要求的项目当中,网络终端对于数据传输的处理能力成了制约此类项目发展的重要因素,对比发现,UDP协议相较于TCP协议而言,在可靠性上虽有欠缺,但在传输速率上占有一定优势,更加适合高速率数据传输的场景[1-2]。而基于FPGA的应用相较于传统的软件实现而言可以节省CPU资源,并且可使系统集成度得到一定的提升。

1 UDP协议及基于FPGA实现的优点

TCP协议与UDP协议同属于TCP/IP结构体系的传输层协议,但相比于UDP协议,TCP协议不适合高速远距离网络[3]。研究人员在TCP协议的基础上提出了许多改进方案,用以提高其传输性能,但受限于TCP协议本身复杂的拥塞控制机制和流量控制机制,TCP协议的改进型在高速远距离网络中的传输性能并不理想[4]。相比于TCP协议,UDP协议是一种不可靠的传输协议,数据传输的可靠性需要上层接口中的应用程序保证,在数据传输开始前,UDP协议不需要像TCP协议那样通过三次握手建立连接,也没有TCP协议复杂的拥塞控制机制和流量控制机制,UDP协议只保证通信间进程的最基本要求,所以采用UDP这种非面向链接的不可靠传输协议能够很好的解决数据传输的实时性及传输速率问题。与受内部CPU控制的串行结构不同,FPGA的并行结构不受指令周期的影响,可以进一步提高终端对于数据传输的处理能力。通过Verilog语言灵活编写UDP协议栈的控制结构,物理连接简单且不需要外设驱动与大量的外围控制电路,大大简化了系统实现的难易程度,且运用灵活,可移植性强,系统集成度高。

2 系统原理及具体实现方法

2.1 系统原理

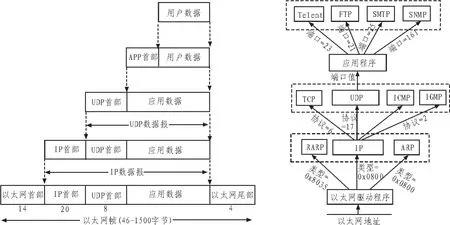

基于UDP/IP模型的层次划分及收发流程如图1所示。

图1 UDP/IP协议栈收发过程示意图

在整个收发过程中,传输层协议按照前面所分析的结论,为提高数据传输速率,只采用UDP协议。因实现的是点到点的单一路径数据传输,因此在不存在路径选择的问题,因此,也就不用实现ARP及RARP协议,降低了系统实现难度。

发送过程:发送过程实际是一个数据打包的过程,按照以太网帧结构由内到外的顺序,以及TCP/IP模型各层协议的规定依次添加应用程序端口号、UDP首部、IP首部、以太网帧首部等结构。当源主机的应用程序需要发送数据给目的主机时,会将数据包发送到UDP/IP协议栈中进行处理,首先数据包在传输层添加传输层首部信息,然后将添加了传输层首部的UDP数据包发送到网络层添加网络层首部生成IP数据包,然后将IP数据包发送给数据链路层添加以太网帧首部及尾部,然后将打包好的以太网帧发送到物理层通过网络发送出去。

接收过程:当目的主机接收到网络中的以太网帧时,目的主机将接收到的以太网帧中所带的地址信息与自身地址信息进行匹配,并对匹配的以太网帧进行解包处理。以太网驱动程序首先根据以太网帧首部中的相关字段确定该数据帧的类型,然后交给相应的协议进行解包处理,解出相应的网络层数据包,然后将网络层数据包发送到网络层进行相应的解包,解出相应的传输层数据包然后发送到传输层进行下一步处理,直到根据数据段中封装的端口号将封装的用户数据交给相应的应用程序,整个接收过程结束。

2.2 具体实现方法

根据各层协议的相关规定及收发流程,将整个系统划分为以下4个模块[5]:

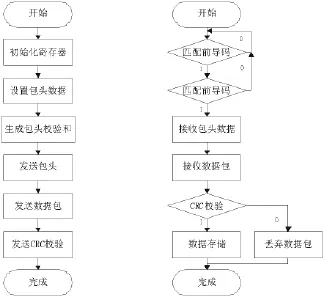

发送模块:发送模块主要包含UDP发送状态机及发送数据缓存两部分功能组成。针对本文所设计的点到点的数据传输,目的IP地址和MAC地址及源IP地址和MAC地址均为已知,所以不需要ARP协议等相关的寻址解析协议,只需要将已知的IP地址及MAC地址在发送模块中直接添加到UDP数据包外层即可[6]。经过发送模块处理后的数据包就是一个完整的以太网数据帧,其格式如图1中发送部分所示。UDP发送状态机包含七个状态,分别是空闲状态、起始状态、生成首部校验和、发送MAC地址、发送IP首部、发送UDP数据包及发送CRC校验码。Verilog程序流程图如图2所示。

接收模块:接收模块主要包含UDP接收状态机及接收数据缓存两部分功能组成,其中UDP接收状态机包含8个状态,分别是空闲状态、等待状态、起始状态、接收MAC地址、接收IP类型码、接收IP地址、接收UDP数据包、CRC校验及数据存储,其中数据存储状态要求对不满4byte的数据进行补0处理,并将这4byte数据存入RAM中。Verilog程序流程图如图2所示。

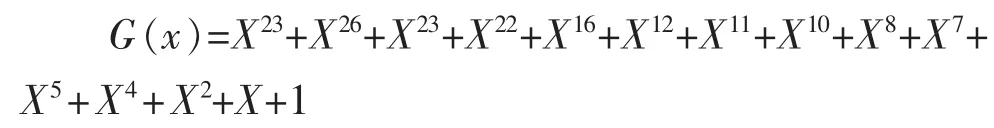

CRC检验模块[11]:本系统在数据传输的速度上有一定的要求,因此CRC校验模块相较于传统的串行CRC校验,为提高校验码生成的速度,采用并行CRC校验,数据每次一个字节8位并行输入进行校验。CRC校验的生成多项式采用CRC-32标准形式[12],具体为:

图2 收发流程图

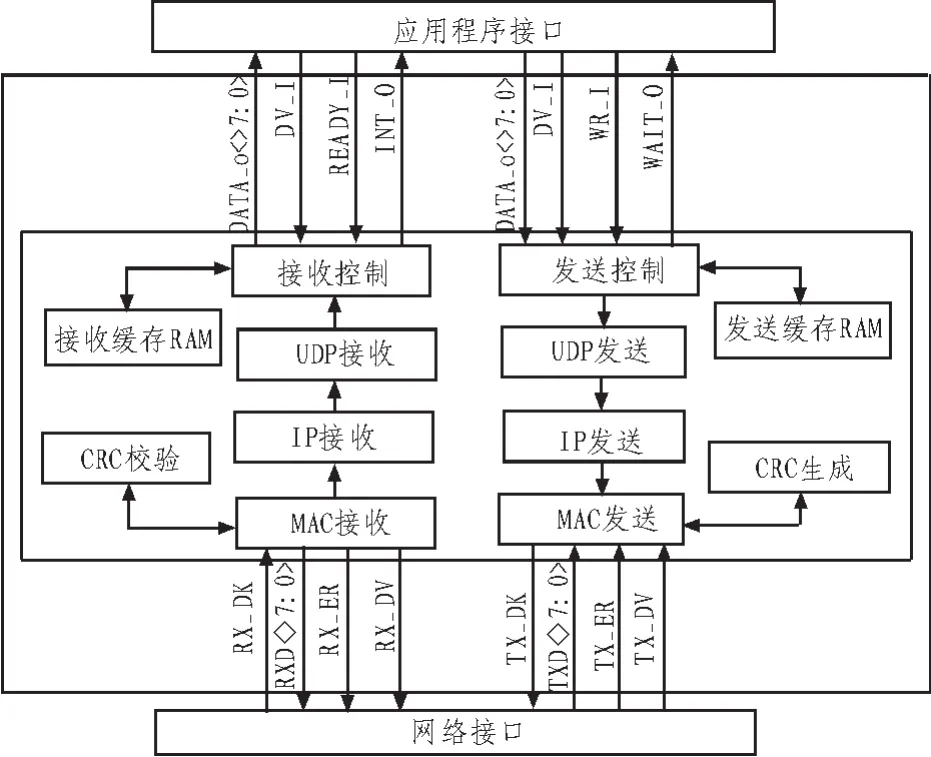

顶层模块:顶层模块对发送模块,接收模块及CRC校验模块进行例化,将3个模块整合,形成一个统一的系统,同时例化一个双端口RAM,读写的位宽是32bit,深度是512,双端口RAM用来做数据缓存用。按照前述要求编写各模块Verilog代码[15]。具体UDP/IP协议栈结构框图如图3所示。

图3 UDP/IP协议栈结构框图

3 FPGA仿真测试及硬件调试

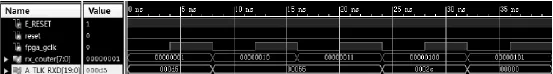

编写测试程序,得到测试波形如图4所示。

图4 仿真波形

从图中可以看出,测试程序给发送模块以相应激励,在接收计数器的相应计数单位上可以看到接收到的发送数据波形,仿真结果符合系统要求。

结合上述分析及各模块Verilog代码及编写的UCF约束文件设计系统原理图,硬件电路设计主要将芯片RTL8211EG的外部接口引出,同时配置好相应的外部电阻电容以及外部晶振。芯片的外部接口主要有两类:一类为FPGA通信的接口,通过40针排针连接;另一类为与RJ45通信接口的相连接口。模块由3.3 V电源供电,通过40针排针的上下两端的接口提供电压。芯片要求外部25 M晶振,且一直处于工作状态,只要有信号需要传输,就可以立即传输。根据设计的原理图绘制PCB板并制板,然后将编写好的程序烧写到FPGA中,并将制好的板与PC通过网线链接,通过网络调试助手向FPGA发送数据,可以在接收端窗口接收到发送的数据,系统功能正常。

4 结束语

相比于TCP协议而言,UDP协议在可靠性上有所欠缺,但其在传输速率及系统复杂度上的优势十分明显。而基于FPGA的网络传输系统开发相较于传统的由软件来实现传输协议的项目开发来说,节约了CPU的资源,提升了系统的整体性能,并且便于移植,系统的集成度也得到了一定的提高。基于FPGA的UDP点到点传输协议在点到点的高速远距离数据传输的运用中有着一定的优势。

[1]王军,吕海宝,许国梁.基于UDP协议的视频图像传输的研究与实现[J].现代计算机:专业版,2002(9):18-20.

[2]张维勇,钱军,王建新.基于UDP协议的视频图像可靠传输的研究和实现 [J].合肥工业大学学报:自然科学版,2008,31(5):698-700.

[3]赵飞,叶震.UDP协议与TCP协议的对比分析与可靠性改进 [J].计算机技术与发展,2006,16(9):219-221.

[4]李勇,戴瑜兴.基于UDP协议的实时监控系统[J].电子技术,2003,30(11):37-40.

[5]Hsiao Y M,Chen M J,Huang K C,et al.High speed UDP/IP ASIC design[C]//Intelligent Signal Processing and Communication Systems, 2009. ISPACS 2009.International Symposium on.IEEE,2009:405-408.

[6]张恺.基于UDP的可靠文件传输协议的设计与实现[D].西安电子科技大学,2014.

[7]靳建平,杨红雨.基于UDP的可靠数据传输协议仿真研究[J].计算机技术与发展,2010,20(5):1-4.

[8]Wolfinger B E,Zaddach M,Heidtmann K D,et al.Analytical modeling of primary and secondary load as induced by video applications using UDP/IP[J].Computer Communications,2002,25(s 11-12):1094-1102.

[9]富元,吕建新.基于UDP的可靠传输协议的研究与实现[J].光通信研究,2009(5):17-19.

[10]Alachiotis N, Berger S A, Stamatakis A.A versatile UDP/IP based PC?FPGA communication platform [C]//Reconfigurable Computing and FPGAs(ReConFig),2012 International Conference on.IEEE,2012:1-6.

[11]伍方辉,方安安.CRC的FPGA设计与实现[J].中国新通信,2009(13):63-65.

[12]Herrmann F L,Perin G,De Freitas J P J,et al. A Gigabit UDP/IP network stack in FPGA.[C]//Electronics,Circuits,and Systems,2009.ICECS 2009.16th IEEE International Conference on.IEEE,2009:836-839.

[13]王珏,何秋燕,王露凯.基于UDP改进的可靠传输协议研究与实现 [J].电脑知识与技术,2015(9):71-73.

[14]Lofgren A,Lodesten L,Sjoholm S,et al.An analysis of FPGA-based UDP/IP stack parallelism for embedded Ethernet connectivity[C]//NORCHIP Conference,2005.23rd.IEEE,2005:94-97.

[15]徐文波,田耘.Xilinx FPGA开发实用教程[M].2版.清华大学出版社,2012.

Implementation of point-to-point transmission based on UDP protocol with FPGA

FU Gao-yuan,GUO Chen,PAN Jin-yong,SHI Xue

(School of Computer and Information,Hohai University,Nanjing 211100,China)

In order to enhance the data transmission rate and improve real-time performance of data transmission,propose a point-to-point data transmission scheme based on UDP protocol.And use the Field-Programmable Gate Array(FPGA)and PHY chip(RTL8211EG)to achieve the point-to-point UDP high speed data transmission.Compared the traditional TCP/IP protocol working principle,and combined with the corresponding theoretical analysis.It is concluded that the system has some advantages in data transmission rate,low complexity of the system,and convenient to realize.

UDP;FPGA;point-to-point;high speed data transmission

TN99

:A

:1674-6236(2017)02-0181-04

2016-01-21稿件编号:201601195

付高原(1990—),男,湖北宜昌人,硕士。研究方向:信号与信息处理。