大容量同步双端口SRAM的仿真方法

(中国电子科技集团公司第58研究所,江苏无锡214072)

大容量同步双端口SRAM的仿真方法

周云波,李晓容

(中国电子科技集团公司第58研究所,江苏无锡214072)

根据大容量同步双端口SRAM(静态随机存储器)功能多、时序严格、存储单元数目巨大的特点,提出了一套用于功能复杂的大容量SRAM仿真验证的激励生成和后仿真验证方法。该方法不仅克服了Hsim仿真激励文件编写耗时、不易修改的缺点,而且解决了大容量双端口SRAM后仿真速度缓慢、占用大量硬件资源的问题,在很大程度上缩短了设计周期,保证了投片成功。芯片采用中芯国际0.13 μm CMOS工艺流片,实测结果验证了该仿真方法是准确有效的。

双端口同步SRAM;激励文件;层次化;关键路径

1 引言

随着集成电路加工工艺越来越先进,与之密切相关的SRAM(静态随机存储器)也得到了迅速的发展。存储容量越来越大,工作频率越来越高,实现的功能越来越多,体系结构也越来越复杂,更新换代的速度更是越来越快[1]。为了保证生产流片的成功率、缩短上市时间,就需要对仿真验证的覆盖率和速度提出更高的要求。目前,在同步双端口SRAM设计中,验证工作已经占据总体工作量的50%以上,而且随着器件规模的增大和功能的增多,其验证的复杂度就越高,耗时也越长。在这种情况下,如何在保证验证覆盖率的前提下提高验证速度,就成为缩短研发周期的关键,也成为了设计开发的难点。目前,在同步双端口SRAM的仿真验证过程中,所面临的问题主要表现在以下两点。

(1)功能多、时序严格,导致激励文件过长。

同步双端口SRAM具有左、右两个端口,每个端口都有各自的数据总线、地址总线、控制信号和时钟信号,可以独立进行读写操作和工作模式选择。同步双端口SRAM一般支持3种工作模式:Flow-through(直通)、Pipelined(流水线)和Burst(突发)模式[2]。直通模式和流水线工作模式下,其地址、数据和控制信号的建立、保持时间不同,器件复位所要的时钟周期不同,数据输出延迟时间也不同。在突发工作模式下,除了进行读/写操作以外,还具有步进选择、计数/屏蔽寄存器回读、中继发送、保持操作和寄存器复位等功能。因此,在进行全参数仿真验证时,如果对照功能逐条手工编写激励文件的话,将是一项既耗时又易出错的工作。

(2)仿真时间及硬件资源的消耗增加。

对于大规模的双端口SRAM,其存储单元数目巨大,并且双端口SRAM一般采用8管单元,因此存储器的晶体管数量可达千万级。如果想遍历所有的存储单元进行仿真验证,即使采用高速Spice仿真软件,其所需要的仿真时间也不容小觑。在深亚微米工艺条件下,器件的寄生参数增多[3],后仿真验证时产生的数据容量超过硬件资源所能容纳的范围,仿真会在运行过程中被迫停止。

针对以上这些问题,结合存储器的结构特点,本文对同步双端口SRAM的仿真验证进行了深入的研究,为电路的仿真验证工作提出了便利而准确的方法。

2 激励文件

在大容量高速SRAM电路仿真时,一般要求必须达到较高的验证覆盖率,即功能验证需要实现各种工作模式、遍历整个器件的存储单元;时序验证需要保证地址、数据和每个控制信号的建立时间、保持时间以及器件的复位时间都满足时序要求。在使用Hsim仿真工具进行仿真时,以上这些要求将使得测试激励文件相当繁琐、冗长,单纯在Hsim的仿真文件中逐条编写几乎不可行。文中通过编写一个简单的Verilog程序,就可以将复杂而准确性较低的操作变成简单的命令,快捷、方便而且满足验证覆盖率的问题。

Verilog是硬件描述语言的一种,用于数字系统设计[4]。设计者可以用它进行各种级别的逻辑设计,也可以用它进行数字逻辑系统的仿真验证、时序分析和逻辑综合等。

根据功能和时序验证的具体要求,本文在UNIX的环境下,通过编写Verilog程序生成后缀为.vec的激励文件,然后,在Hsim仿真工具的.sp仿真文件中,引用此激励文件进行仿真验证。定义时间标尺为100 ps,定义InFlagA和InFlagD,以下是部分功能的激励文件。2.1 流水线模式下的读周期(任一端口)

在流水线模式下,从数据线上读取输出数据前,输出数据被存储在寄存器内。时钟切换前,控制信号必须在tS(建立时间)内存在并且有效,另外时钟切换后要在tH(保持时间)内保持为有效状态,在时钟上升沿上,地址被寄存,并且开始读周期。

Verilog语言描述如下:

for(i=0;i<n;i=i+1)

begin

#23 Clk=1;//在时钟上升沿加载地址

#6 InFlagA=0;//地址保持6 ns

#24 Clk=0;

#7 InFlagA=1;AI=2**i;

end

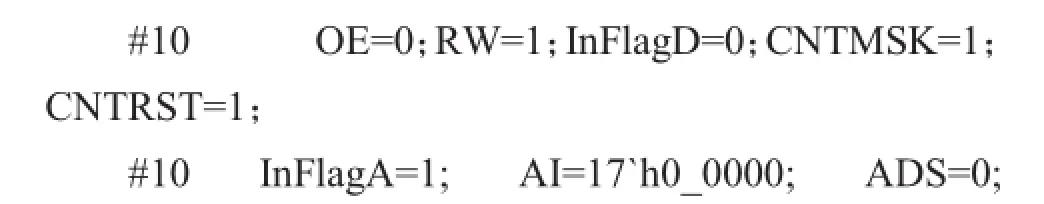

2.2 突发模式下的读周期(任一端口)

器件的每个端口都包含一个可编程的突发地址计数器。突发计数器包含4个寄存器:1个计数寄存器,1个屏蔽寄存器,1个镜像寄存器和1个忙地址寄存器。突发模式下只加载连续序列地址中的第一个地址,并且通过递增芯片中的地址计数器来完成后续访问。

Verilog语言描述如下:

CNTEN=0;//从地址线加载地址到突发计数器和镜像寄存器

for(i=0;i<n;i=i+1)

begin

#30 Clk=1;

#6 InFlagA=0;ADSR=1;//内部计数地址步进

#24 Clk=0;

end

2.3 计数器中继功能(任一端口)

在计数器公开位累加至全1时,如果计数器要继续累加,计数器中断标志位置低,当计数器累加为其他任一数值时,该信号释放。该信号可以由计数器复位、计数器加载、屏蔽复位、屏蔽加载信号控制。

Verilog语言描述如下:

#50 InFlagA=1; AI=17`h0_000E; ADS=0; CNTEN=0;CNTMASK=0;CNTST=1;//加载地址线上的地址到屏蔽寄存器,并定义计数器步进

#23 Clk=1;

#6 InFlagA=0;ADS=1;CNTEN=1;

#24 Clk=0;

#7 InFlagA=1; AI=17`h0_0004; ADS=0; CNTEN=0;CNTMASK=1;CNTRST=1;//从地址线加载地址到突发计数器和镜像寄存器

for(i=0;i<n;i=i+1)

#23 Clk=1;

#6 InFlagA=0;ADS=1;CNTEN=1;

#24 Clk=0;

#7 CNTENT=0;

end

生成测试文件的主要指令如下:

begin

$fdisplay(vec_file,“ ”);//对vec文件进行定义,其中signal定义vec文件的端口信息,radix定义vec文件数据位宽,io定义vec文件端口类型,tunit定义vec文件时间单位,slope定义vec文件信号上升/下降延迟,vih/vil定义vec文件逻辑高/低电平。

end

vec_file=$fopen(“文件名.vec”);

$fmonitor(vec_file,“ ”);//定义vec文件数据类型或进制

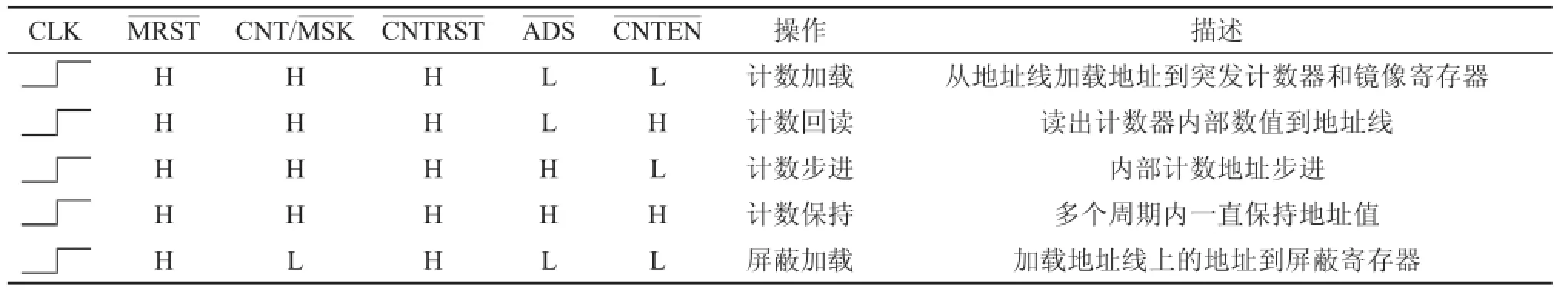

表1 突发计数器和屏蔽寄存器控制操作(任一端口)

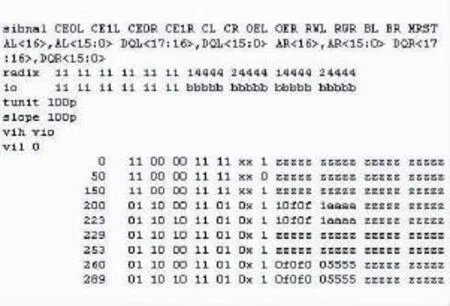

运行Verilog程序,自动生成相应的测试文件,如图1所示。然后在Hsim仿真文件中,采用.param hsimvectorfile=“文件名.vec”语句将其引用即可[5]。

这种方式事半功倍,产生的激励文件信息完备、覆盖率高,且易于修改和纠错,大大减少了运行仿真前准备工作的工作量和时间。

3 后仿真验证

目前,常用的基于大规模电路晶体管级的Spice高速仿真软件主要有Hsim(Nassda公司)、Ultrasim(Candence公司)、Nanosim(Synopsys公司)等。但是,在进行SRAM后仿真验证时,其速度并不令人满意,主要有两方面的原因。其一是由于SRAM容量和端口的增加。例如,对于本文中容量为4 Mb的双端口SRAM来说,其含有4 718 592个存储单元,并且此SRAM是双端口器件,采用的是8管存储单元设计,因此仅存储阵列就包含有37 748 736个晶体管。其二,随着工艺尺寸的不断减小,器件的寄生参数也不断增多。当工艺特征尺寸≤0.13 μm时,后仿真连线的延迟已经接近器件的延迟,金属连线以及晶体管的寄生效应非常明显。将4 Mb双端口SRAM整体版图的所有寄生参数进行提取并加以统计可知,其中的寄生电阻、电容数量已经远远超出了晶体管本身的数目,很大程度上增加了后仿真网表文件的容量。这两方面的原因使得那些高速的Spice仿真软件要想得到精确的仿真结果就不得不进行更加繁复的公式计算,最终导致仿真速度仍然缓慢。

面对上述问题,本文依据双端口SRAM的电路结构特点,提出了一套加快后仿真验证速度的方法。3.1 寄生参数的提取

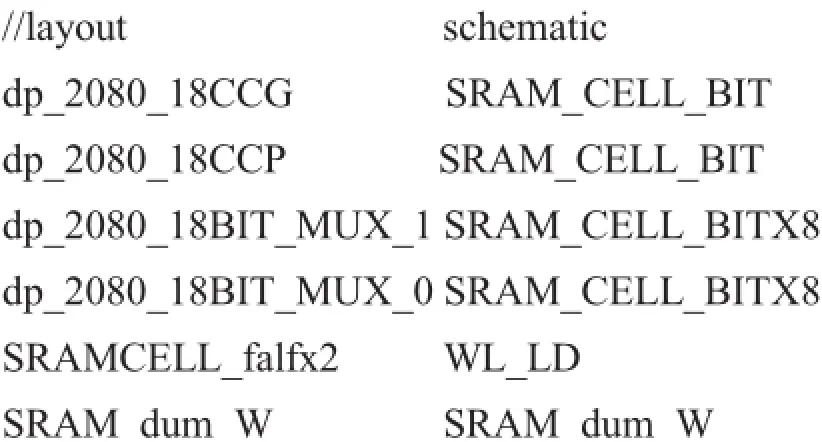

双端口大容量SRAM的版图信息量大且较为复杂,在进行其寄生参数的提取时,可以采用编写Hcell(Hierarachically Corresponding Cell)文件的方法层次化对应的单元,以达到简化逻辑和版图层次、缩短calibre LVS运行时间的目的。

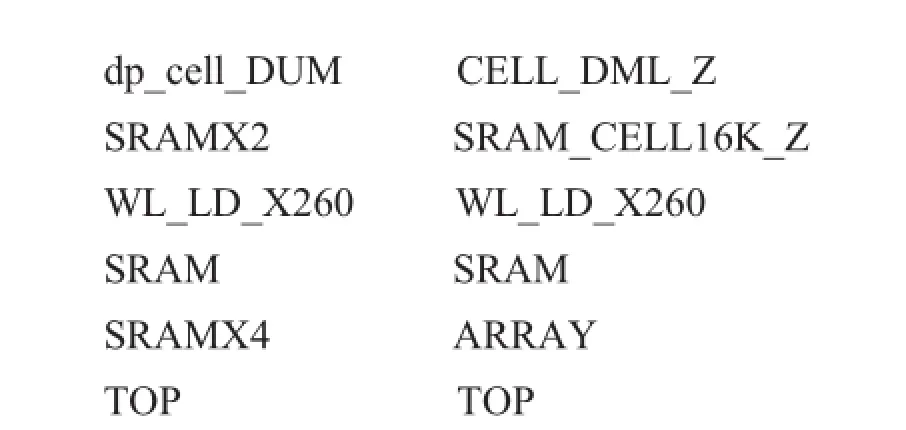

一般情况下,Hcell文件应该尽量简单,复杂的Hcell列表也会增加calibre LVS运算的工作量,适得其反。本文中编写的Hcell文件如下所示:

图1 部分.vec测试文件

在Hcell文件中,版图和逻辑的名字可以相同也可以不一致,可以指定一个版图名字对应多个逻辑,也可以指定多个版图名字对应一个逻辑。

通过编写成Hcell文件使得版图单元名与逻辑单元名一一对应,将版图进行层次化,再进行全参数提取。然后在.sp文件中采用.param hsimspf=“后仿真参数”语句将版图提取的参数反标至逻辑网表,形成最后所需的信息完整的后仿真网表。

3.2 关键路径的选择

本文中的双端口SRAM的存储容量较大,如若是遍历所有存储单元进行验证,则数据量太大,消耗过多的硬件资源,且仿真周期太长。根据SRAM存储阵列的结构和外围电路的布局,可以通过选取关键路径的方法对部分存储单元进行验证。此方法中,关键路径如何选取将直接影响到仿真验证的覆盖率和准确度。

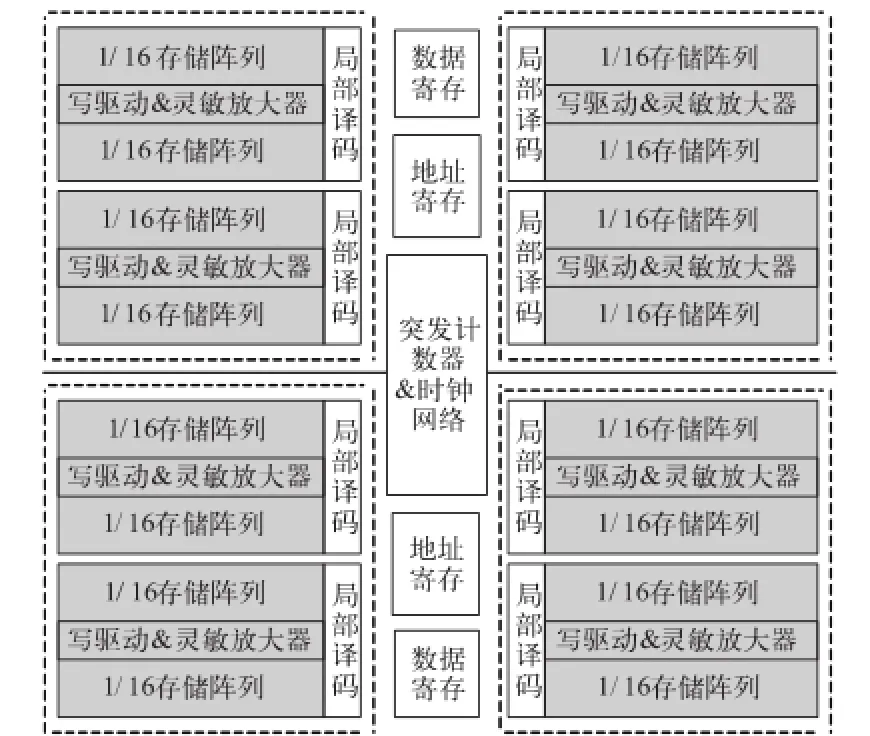

4 Mb同步双端口SRAM电路的存储单元阵列与外围电路的布局如图2所示。此结构中,占据绝大部分面积的是数据通路、地址通路和时钟网络,其中数据通路主要包含数据寄存逻辑、写驱动电路、灵敏放大器和存储单元阵列;地址通路主要包含数据寄存逻辑、用于突发工作模式的突发计数器和译码逻辑。整个存储单元阵列分为16个小块,每一块都有局部译码进行字线、位线的选择。每1/16块阵列中相邻的8列单元左、右端口各共用一个灵敏放大器和写驱动;每条位线均有一个位线预充电路。

图2 4 Mb同步双端口SRAM布局图

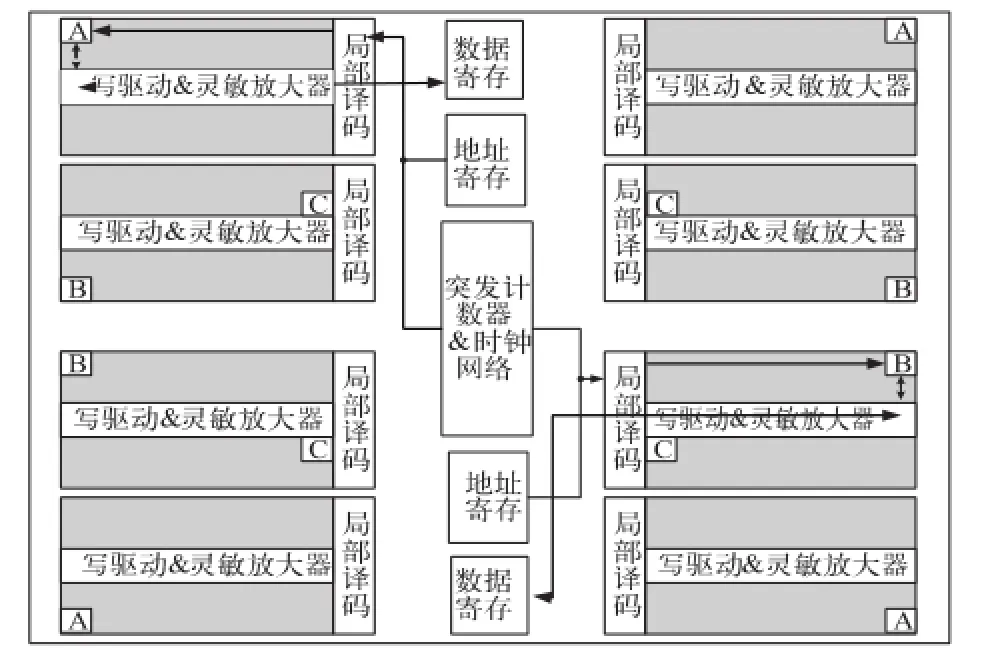

如果要计算一个写操作的时间,就选取写操作的最长路径。如图3所示,单元模块A距离写驱动和局部译码电路都是最远的,因此字选信号和数据到达单元的时间也就最长、信号最弱。此外,由于时钟信号从整个版图的中部引出,因此对于处于边角的单元模块A,其写驱动和局部译码的触发时间也最长。同时A模块这一行的单元也是距离灵敏放大器最远的,因此单元模块A的读/写通路可作为关键路径之一。

同理,单元模块B所处的位置,不仅距离局部译码、写驱动和灵敏放大器最远,而且其对应的写驱动和灵敏放大器也是距离数据控制逻辑最远的模块,因此,单元模块B的读/写通路也是一条关键路径。单元模块C处于整个版图的中部,与外围电路距离较短,其读/写通路也应该作为考核的对象。

图3 关键路径示意图

4 仿真技术验证

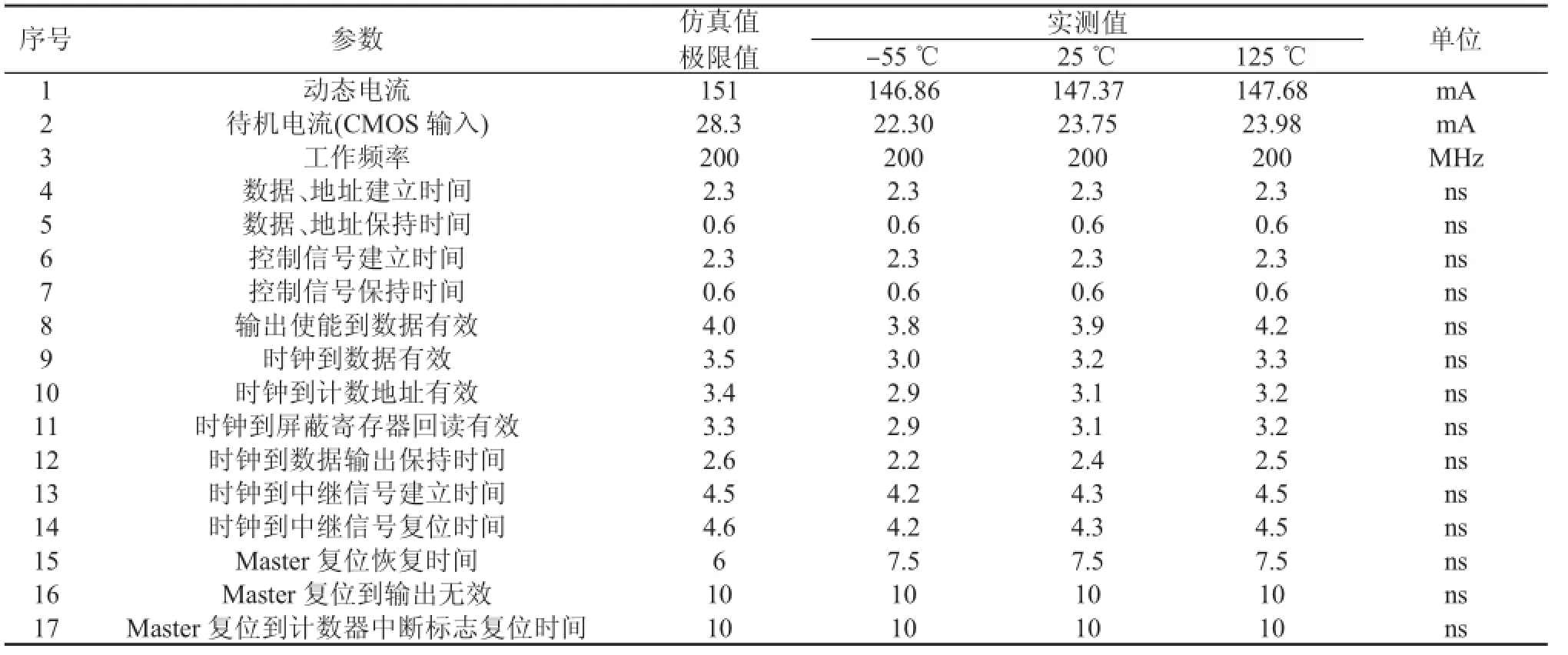

本文中的4 Mb同步双端口SRAM采用SMIC 0.13 μm CMOS工艺流片。后仿真验证过程中,寄生参数文件由约4.0 GB降至394.5 MB,减小约90%,LVS验证时间缩短96%以上,大大提高后仿真验证的效率,减少硬件资源的消耗。三温实测结果表明其功能完整,性能稳定,工作频率可以达到200 MHz以上,仿真数据和实测数据误差小于5%,充分说明了激励文件的完成性、仿真方法的准确性,部分参数的仿真结果与测试数据对比如表2所示,其中因为仿真采用的是SS工艺角、125℃和FF工艺角、-55℃等极限条件,所以实测结果优于仿真结果。

5 结论

随着SRAM进入高速、大容量、多端口的阶段,准确、完备、快速的设计验证将是设计成功的关键。本文论述的仿真激励生成和后仿参数提取的方法,不仅缩短了仿真验证周期、节约了大量的硬件资源,而且覆盖率高、数据完整,保证了投片的一次性成功,在实际应用中具有推广价值。

表2 4 Mb同步双端口SRAM电路全参数(VDD=3.3 V±0.165 V,GND=0 V)

[1]中商情报网公司.2013—2017年中国SRAM市场调查及发展趋势研究报告[R].2013.

[2]了解同步双端口RAM[EB/OL].http://www.cypress.com.

[3]R Jacob Baker,Harry W Li,et al.CMOS Circuit Design, Layout,and Simulation [M].New York:The Institute of Electrical and Electronic,Inc.1997.

[4]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2004.

[5]Hsim Simulation Reference[P].SYNOPSYS,2009.

[6]刘树林,张华曹,柴常春.半导体器件物理[M].北京:电子工业出版社,2009.

作者简介:

鲍宜鹏(1985—),男,江苏宿迁人,硕士研究生,研究方向为SOC设计方法学。

Research on Simulation Method of Large Capacity Synchronous Dual-port SRAM

ZHOU Yunbo,LI Xiaorong

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214072,China)

The large capacity synchronous dual-port SRAM is usually of multi-function,critical time sequence and huge number of storage units.The paper proposes the method of simulation sources generation and parameter extraction for SRAM.The method not only overcomes the shortcomings of the conventional 'HSIM'tool but also increases the speed and saves hardware resources during post-layout simulation of large capacity dual-port SRAM.It greatly shortens the design cycle.The chip is manufactured by SMIC 0.13 μm CMOS process.The experiment results verify the accuracy and effectiveness of the simulation method.

dual port SRAM;simulation sources;Hcell;critical path

TN402

A

1681-1070(2016)12-0035-05

周云波(1984—),女,河南郑州人,2012年江南大学微电子专业博士毕业,现主要从事存储器研发工作。

2016-6-14