一种采用单双跳变的低功耗确定性BIST方案

张建伟, 丁秋红, 周 彬, 滕 飞, 马万里, 王政操, 陈晓明, 李志远

(1.大连理工大学 电子科学与技术学院, 辽宁 大连 116024;2.哈尔滨工业大学 空间基础科学研究中心,哈尔滨 150001;3.黑龙江大学 电子工程学院, 哈尔滨 150080)

一种采用单双跳变的低功耗确定性BIST方案

张建伟1, 丁秋红1, 周 彬2, 滕 飞1, 马万里1, 王政操1, 陈晓明1, 李志远3

(1.大连理工大学 电子科学与技术学院, 辽宁 大连 116024;2.哈尔滨工业大学 空间基础科学研究中心,哈尔滨 150001;3.黑龙江大学 电子工程学院, 哈尔滨 150080)

为实现低功耗和高故障覆盖率,基于单跳变测试技术和2-bit扭环计数器,提出一种新型的单双跳变的确定性测试向量产生器. 首先,与一般的确定性测试方案直接存储确定性种子不同,利用ROM存储控制信号并通过单双跳变生成确定性种子和确定性测试向量,这样控制信号的长度约为确定性种子的1/2,有利于降低功耗并节约存储空间. 其次,2-bit减法计数器合理地过滤了冗余向量,大大缩短了测试时间并降低总体能耗. 最后,为了适应不同的测试需求,还设计了相应的测试向量压缩算法和三种x指定算法. 实验结果表明,平均功耗分别降低了42.36%、32.32%、38.94%,测试长度分别减少了77.6%、86.1%、84.3%,测试数据分别压缩了79.4%、65.2%、68.1%.

扭环计数器; 低功耗;确定性;测试向量生成器; 单跳变

近些年来,由于制造工艺不断减小,测试规模不断加大,这些都增加了ATE测试平台的硬件需求,如测试通道个数和测试向量存储空间的大小. 在这样的背景下,内建自测试BIST(built-in self-test)技术被提出. 为了降低面积开销并快速的实现较高的故障覆盖率[1],线性反馈移位寄存器LSFR(linear feedback shift register)被广泛使用在BIST技术中. 但是它的开关活动性过高,导致测试功耗远远高于正常工作状态时的功耗,进而影响芯片的可靠性.

为了解决这个问题,提出了多种测试方案. 比如通过修改或使用新型的测试向量生成器TPG(test pattern generation)结构来减少TPG的跳变次数,从而降低测试功耗. 如文献[2-4]中的LT-LFSR, DS-LFSR和多级LFSR等. 文献[5-6]通过修改被测电路内部的测试结构同样也能达到减少功耗的目的.

除此之外,由于单跳变技术卓越的低功耗特性,近些年来被广泛运用在TPG设计中. 比起多跳变测试向量,单跳变测试向量能够更好地检测到多种故障类型,例如延迟故障[7-8]. 基于该特性,许多伪随机单跳变RSIC (random single input change) 测试方案被提出[9-11]. 文献[9]将LFSR和2-bit 扭环计数器TRC(twisted ring counter)结合起来生成了一种新型的单跳变测试向量生成器. 它利用控制信号可以灵活地实现LFSR与TRC模式的来回切换. 当处于TRC模式下,由L-stage LFSR指定2-bit TRC发生单跳变;当进入LFSR模式后,电路会生成新的相关性较低的伪随机种子,从而更快速地提高故障覆盖率. 不过与确定性测试[12]技术相比,伪随机测试技术既无法达到ATPG所能达到的故障覆盖率,同时为了实现较高的故障覆盖率又需要耗费较长的测试时间,增加测试能耗.

因此,本文对文献[9]进行了改进,采用单双混合跳变技术和单双跳变SDIC(single/double input change)单元来实现一种新型的确定性测试向量生成器. 为了减小面积开销,优化不同的测试性能需求,本文还提出了对应的种子压缩算法和3种不同的x指定算法. 以ISCAS’85测试电路为例,实验结果表明,在保证ATPG故障覆盖率的前提下,该测试方案能够有效地减少测试时间,压缩存储种子的个数并最大化地降低测试功耗.

1 设计动机

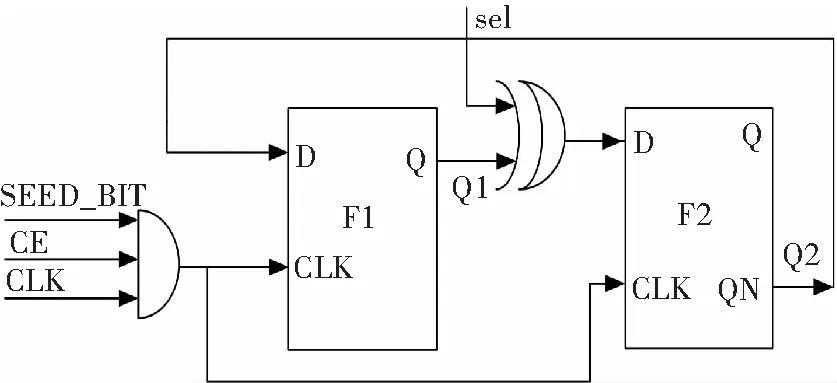

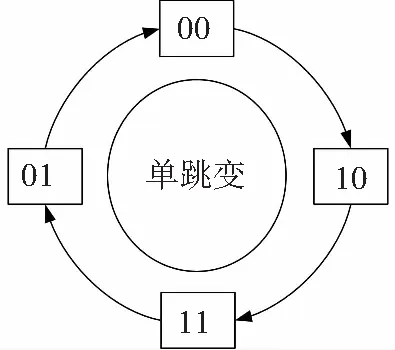

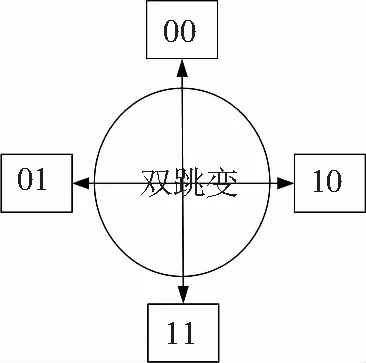

为了实现单双混合跳变的切换,本文对2-bit TRC进行改进. 图1所示为测试向量生成器基本单元SDIC的结构框图,它增加了一个异或门和一个sel信号. 当sel为1时,SDIC进行双跳变;当sel为0时,SDIC进行单跳变. 单双跳变的状态图如图2和图3所示. 此外,在重播种过程中,为了生成确定性种子和测试向量,电路被划分为两个工作状态:种子生成状态和向量生成状态. 当电路工作在种子生成状态时,每个SDIC的CE会被轮流选中,此刻只有对应的SEED_BIT信号有效时,SDIC才能发生跳变,且跳变模式由sel信号决定;当电路进入向量生成状态时,SEED_BIT信号始终保持为1,sel保持为0. 随着每个SDIC的CE轮流有效,每个单元轮流发生单跳变,见表1.

图1 SDIC的内部结构

以ISCAS’85中的C17为例,使用本文和文献[9]中的测试向量生成器,分别生成10个测试向量,对比两者的测试结果,见表2. 从表2看,除了需要额外的面积开销来存放种子以外,无论是测试时间,平均功耗,峰值功耗还是故障覆盖率,本文的实验结果都明显优于文献[9]的实验结果.

图2 SDIC单跳变变化

图3 SDIC双跳变变化

当前状态CESEED_BITsel模式01/01/0不变种子生成状态101/0不变110单跳变111双跳变向量生成状态010不变110单跳变

表2 SDIC 和AM2B-TRC[9]测试结果对比

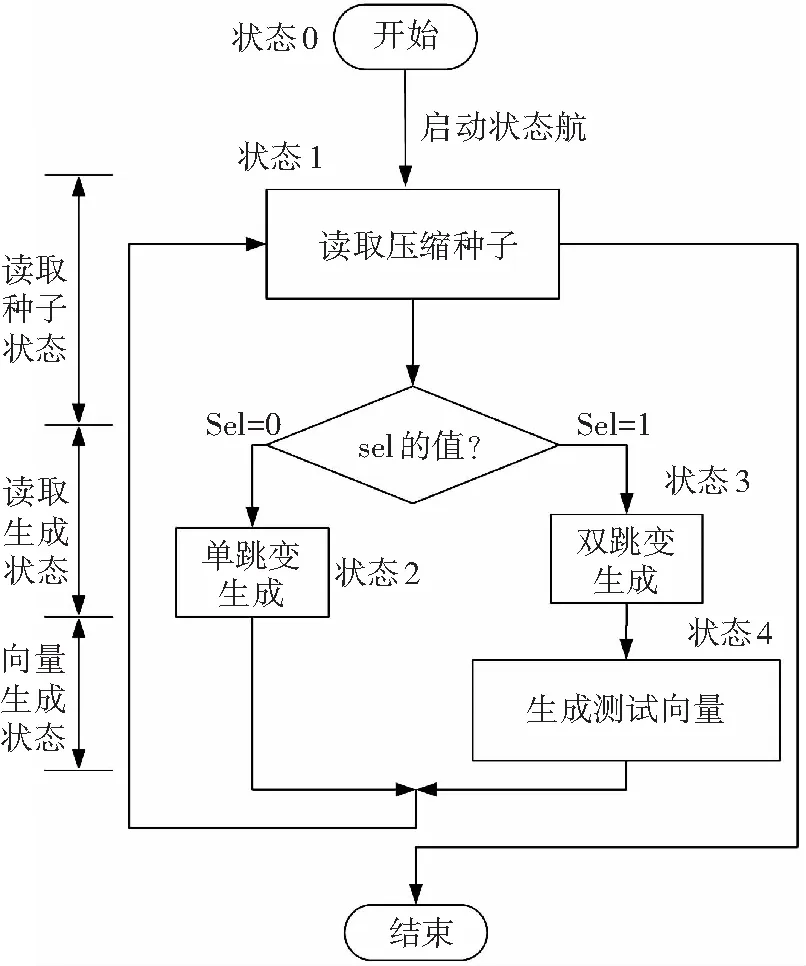

2 测试电路的结构

图5对测试电路的工作流程进行了说明. 电路可以通过两种方式来生成确定性种子. 若sel为1,电路进入状态3,通过双跳变的方式来生成新的种子. 反之,则电路会进入状态2,完成一轮单跳变后直接跳回状态1重新读取新的存储数据,然后再进入状态3生成最终的确定性种子. 这两种方式的最大区别在于第一种方式只需要一个存储数据就可以生成目标种子,而后者则需要读取两个.

图4 低功耗测试向量生成器的结构图

图5 状态机工作图

具体的工作流程是先启动状态机,从存储器中读取存储数据. 然后进入种子生成状态,读取sel信号的值,确定种子的生成方式. 假设sel为1,电路进入双跳变模式. 读取前n/2位存储数据作为该状态下的SEED_BIT[n/2-1:0]输出,启动减法计数器并使能移位寄存器,移位寄存器的初始值为0…01. 随着移位寄存器串行移位,每个SDIC的CE轮流有效,这时由SEED_BIT[i]信号来确定SDIC是否发生跳变. 当移位寄存器为0…01时,状态机进入向量生成状态. 读取第n/2+1 ~n/2+2位存储数据作为减法计数器的初始值,重新使能移位寄存器. 之后,每个SDIC轮流发生单跳变. 每当一轮移位完成后,2-bit减法计数器减一. 当且仅当2-bit减法计数器的值小于0时,移位寄存器使能关闭,状态机跳入下一个状态. 总结如上的跳变规律可发现,向量生成状态最多可以生成2n个不同的测试向量. 一旦超过这个数值电路就会生成重复的向量,测试效率将大大地降低. 并且,这2n个向量也并非全部有效. 因此本文通过2-bit减法计数器合理地约束有效向量生成,从而达到减少测试时间、降低测试能耗的目的.

综上所述,本文的电路可以总结出以下特点. 1)大部分确定性种子只需要n/2+3位存储数据就可以生成,当n比较大时,可以节约近一半的面积开销. 2)与文献[9]通过LFSR结构生成伪随机种子相比,本文通过单双跳变来生成确定性种子,这样既可以降低TPG生成功耗也可以降低被测电路的测试功耗. 3)电路中采用了2-bit减法计数器来约束SDIC单跳变周期,减少了冗余向量的生成,降低了测试时间和测试能耗.

3 种子压缩算法和x指定算法

如图2所示,SDIC单元内的取值一共有4组,分别为00-10-11-01. 若要从00->10,一次单跳变就可以实现;若要将00->11,则需要进行一次双跳变. 若要将00->01则需要分别进行一次单跳变和一次双跳变. 由此可以发现:通过两个存储数据便可以实现两个向量之间的任意切换. 其中一个存储数据用于控制SDIC单跳变翻转,另一个实现双跳变翻转. 而要实现翻转,只需要前n/2位存储数据SEED_BIT[n/2-1:0]的对应位上为1便可.

基于该特性,设计出对应的种子压缩算法,如图6所示. 第一步,先根据被测电路生成确定性测试向量集Tpx. 将000…0作为确定性种子,并从确定性测试集中挑选出与确定性种子完全相容的目标向量,将它们从Tpx中删除. 这里与种子完全相容的意思是该向量可以由确定性种子经过m*n/2(m<=4)次单跳变产生的. 确定完相容的测试向量之后便可确定2-bit减法计数器的周期m,以及生成的确定性测试向量的个数,将这些保存到all_pat测试集中.

图6 种子压缩算法流程图

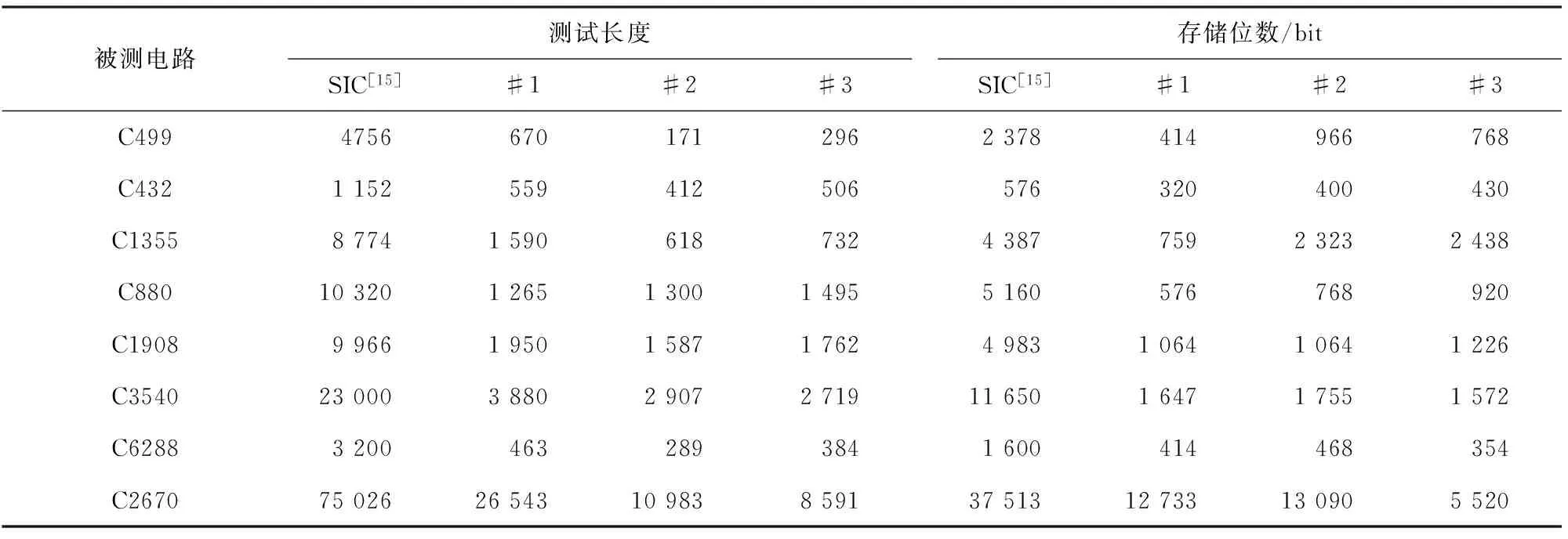

第二步,选择并确定下一个确定性种子. 为了减少存储数据的个数,在选择下一个种子时尽量挑选仅通过一轮双跳变就能生成的向量作为候选的确定性种子. 首先,将确定性测试集Tpx中需要通过p(p 在这个过程中,本文还采用了另一个压缩技巧. 即一旦获得新的all_pat测试集,便采用Atlanta工具仿真生成新的故障覆盖率和新的待压缩的确定性测试集Tpx. 换而言之,在整个过程中,Tpx都在实时更新. 这样做可以最大化地利用中间向量,提高压缩效率. 在实验中可以指定工具生成包含x态的确定性测试集,如Fastscan和Atlanta. 一般情况下,x的含量越大,则压缩效率会越高[13]. 而如何指定x则会影响到电路的整体性能. 本文从三个角度出发,分别提出了3种不同的x指定算法. 实验教学是教学过程中的重要组成部分,能使毕业生提高动手操作能力、创新能力、吃苦耐劳能力,提高在实验中发现问题、分析问题、解决问题的能力,掌握了这些技能会使毕业生被很多用人单位看重,同时,实验教学也对教学质量的提高发挥着至关重要的作用。 3.1 提高确定性种子的向量压缩率 x位指定算法1如图7所示,在指定x时,保证生成的确定性种子能够尽可能多地与测试集Tpx中的向量完全相容. 图7 x指定算法1 首先从候选种子集中挑选出候选种子i,从确定性向量集Tpx中找出与之完全相容的测试向量集Tpx_i. 然后,从第1个SDIC开始指定,一边用上一个确定性种子和Tpx_i指定第j个SDIC,一边筛选出与指定后的候选种子完全相容测试向量集Tpx_i,保证当n/2个SDIC被指定完后Tpx_i能与之完全相容. 最后从候选种子中挑选出最大相容量的作为下一个确定性种子. 这种算法可以尽可能多地压缩测试集Tpx中的测试向量,减少确定性种子的个数,从而减少面积开销. 3.2 减少冗余向量的个数 通过控制SDIC单/双跳变来生成下一个确定性种子. 在这个过程中,每次有且仅有一个SDIC会发生单/双跳变. 如此,从上一个种子的最后一个状态到下一个种子的过程中,许多无用的中间状态将生成. 为了尽量压缩中间状态的个数,可以从候选种子集中挑选出与上一个状态汉明距离最小的向量作为确定性种子,具体如图8所示. 图8 x指定算法2 3.3 基于变游程编码对种子进行再压缩 为了进一步减少面积开销,本文采用了变游程编码算法[14]对原存储数据进行再编码压缩. 这个算法压缩效率高,解压器结构简单. 当然,为了提高种子的再压缩率,必须依照变游程的编码特性来指定x. 如下为一个随机向量变游程编码前和编码后的结果. 编码前: TD = 00001 11111111110 0000001(23位) 编码后 : TE = 0111 110101 001001(16位) 对比编码前后可以发现:相邻相同连续的向量个数越多,编码效率越高. 如图9所示,首先,先用上一个确定性种子来指定候选种子i1,这样可以保证i1可以通过p次双跳变直接生成. 其次,对i1进行双跳变编码分段生成i2. 除了x以外,i2中每段有且只有一个0->1或1->0跳变. 指定i2中的x,保证它们与每段中的最后一个值相反,与前k个值完全相同. 最后,根据指定后的i2反向指定i1的x值. 指定结束后,将i2变游程编码生成i3,变游程压缩效率最高的i2作为下一个确定性种子. 图9 x指定算法3 为了验证提出算法的有效性,使用ISCAS’85测试电路作为测试对象,使用Atlanta工具生成ATPG测试向量,利用Matlab编程,实现向量压缩算法和三种x指定算法,通过计算被测电路内部节点的扇出和跳变次数来得出等效的总跳变次数. 实验完成后,一共获得了三种测试数据. 分别用#1,#2,#3来表示算法1,算法2和算法3. 每种算法的峰值功耗、平均功耗、总体能耗、测试长度以及存储位数等参数如表3所示. 其中本文使用跳变次数来描述峰值功耗、总体能耗和平均功耗,使用存储位数来描述存储空间大小. 从表3的结果看来,算法1在功耗和面积开销方面有较为显著的优势. 平均功耗和峰值功耗都相对较低,且当测试电路规模较小时,存储空间最小,但它的测试时间较长. 相对而言,算法2的测试时间较短,从而可以降低总体能耗,但是无论功耗特性和面积压缩效率都表现一般. 而算法3整体性能指标较高,无论是测试长度、总体能耗、平均功耗、峰值功耗,还是存储空间都有较好的结果. 特别当被测电路规模越大,向量压缩效率便越高. 但它需要额外的变游程解码器,增加面积开销. 表4对比了算法1、算法2、算法3和AM2B-TRC[9]的平均功耗. 前者是基于后者为基础进行的改进,但考虑到AM2B-TRC[9]采用的伪随机测试方案,因此只对比了两者的平均功耗. 结果表明,算法1、算法2、算法3的平均功耗远低于AM2B-TRC的平均功耗,平均分别可以降低42.36%、32.32%、38.94%. 表5中分别对比了3种算法和确定性SIC[15]的测试长度及存储空间. 其中测试长度(测试时间)分别平均减少了77.6%、86.1%、84.3%,而存储位数也减少了79.4%、65.2%、68.1%. 表3 3 种x指定算法的测试结果对比 注:由于单位跳变所产生的能耗是相同的,因此使用跳变次数来表述总体能耗和峰值功耗,而平均功耗=总体能耗/测试长度. 表4 3种x指定算法和文献[9]平均功耗的对比 表5 3种x指定算法和文献[15]关于测试长度和存储位数的对比 基于单/双跳变技术的确定性BIST压缩方案和3种不同的x指定算法总体性能都有了很明显提升,其中平均功耗分别降低了42.36%、32.32%、38.94%,测试长度分别减少了77.6%、86.1%、84.3%,测试数据分别减少了79.4%、65.2%、68.1%,整体上性能得到了较大的提升. [1]高燕. 基于寄存器传输级层次模型的测试生成研究[D].北京:中国科学院研究生院, 2003. GAO Yan. Test Generation based on Hierarchy Model at Register Transfer Level [D].Beijing: Graduate University of Chinese Academy of Sciences, 2003. [2] WANG S, GUPTA S K. LT-RTPG: A new test-per-scan BIST TPG for low switching activity[J]. Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on, 2006, 25(8): 1565-1574. [3] WANG S, GUPTA S K. DS-LFSR: A new BIST TPG for low heat dissipation[C]//Test Conference, 1997. Proceedings. International. [S.l.]: IEEE, 1997: 848-857. [4] ROSINGER P, AL-HASHIMI B M, NICOLICI N. Dual multiple-polynomial LFSR for low-power mixed-mode BIST[J]. IEE Proceedings-Computers and Digital Techniques, 2003, 150(4): 209-217. [5] GHOSH S, BASU S, TOUBA N. Joint minimization of power and area in scan testing by scan cell reordering[C]//VLSI, 2003. Proceedings. IEEE Computer Society Annual Symposium on. [S.l.]: IEEE, 2003: 246-249. [6] ABU-ISSA A S, QUIGLEY S F. Bit-swapping LFSR and scan-chain ordering: A novel technique for peak-and average-power reduction in scan-based BIST [J]. Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on, 2009, 28(5): 755-759. [7] VIRAZEL A, DAVID R, GIRARD P, et al. Delay fault testing: choosing between random sic and random mic test Sequences [C]//Test Workshop, 2000. Proceedings. IEEE European. [S.l.]: IEEE, 2000: 9-14. [8] LI Xiaowei, CHEUNG P. High-level BIST synthesis for delaytesting[C]//Defect and Fault Tolerance in VLSI Systems, 1998. Proceedings. 1998 IEEE International Symposium on. [S.l.]: IEEE, 1998: 318-323. [9] ZHOU Bin, WU Xinchun. A Low Power Test-per-Clock BIST Scheme through Selectively Activating Multi Two-Bit TRCs[C]//Instrumentation and Measurement, Computer, Communication and Control (IMCCC), 2014 Fourth International Conference on.[S.l.]: IEEE, 2014: 505-509. [10]VIRAZEL A. On hardware generation of random single input change test[J]. Journal of Electronic Testing: Theory and Applications, 2002, 18: 145-157. [11] LEI Shaochong, Hou Xueyan, Shao Zhibiao, et al. A class of SIC circuits: theory and application in BIST design [J]. Circuits and Systems II: Express Briefs, IEEE Transactions on, 2008, 55(2): 161-165. [12]曹贝. SoC 低功耗测试技术和温度意识测试规划研究[D]. 哈尔滨:哈尔滨工业大学, 2010. CAOBei. Research on low power test technology and temperature aware test scheduling for system-on-chip [D]. Harbin: Harbin Institute of Technology, 2010. [13]周彬, 吴新春, 叶以正. 二维测试数据压缩的优化[J]. 计算机研究与发展, 2015, 46(4): 637-643. ZHOU Bin, WU Xinchun, YE Yizheng. Optimization of two dimensional test data compression [J] Journal of Computer Research and Development, 2015, 46 (4): 637-643. [14]彭喜元, 俞洋. 基于变游程编码的测试数据压缩算法[J]. 电子学报, 2007, 35(2): 197-201. PENG Xiyuan, YU Yang. A test set compression algorithm based on variable-run-length code [J]. Acta Electronica Sinica, 2007, 35 (2): 197-201. [15] XIAO Liyi, CAO Bei, WANG Yongsheng. Seeds optimization algorithm of SIC test sequences in low power BIST[C]//Laser Physics and Laser Technologies (RCSLPLT) and 2010 Academic Symposium on Optoelectronics Technology (ASOT), 2010 10th Russian-Chinese Symposium on. [S.l.]: IEEE, 2010: 352- 355. (编辑 王小唯 苗秀芝) Low power deterministic BIST based on SDIC ZHANG Jianwei1, DING Qiuhong1, ZHOU Bin2, TENG Fei1, MA Wanli1, WANG Zhengcao1, CHEN Xiaoming1, LI Zhiyuan3 (1. School of Electronic Science and Technology, Dalian University of Technology, Dalian 116024, Liaoning, China;2. Space Basic Science Research Center, Harbin Institute of Technology, Harbin 150001, China;3. School of Electronic Engineering, Heilongjiang University, Harbin 150080, China) In order to obtain low power consumption and high fault coverage, a new single-double input change deterministic test pattern generator is presented based on a single input change technology and 2-bit twisted ring counter. Firstly, unlike traditional deterministic test schemes storing the deterministic seeds, the presented scheme saves the control signal bits in ROM. With these bits, the deterministic seeds and patterns are generated by single-double input change. It is beneficial for power consumption and area overhead because the length of control signal bits are just about 1/2 of deterministic seed’s. Secondly, 2-bit down counter can reasonably filter redundant vector, and it greatly shorten test time and reduce overall energy consumption. At last, considering different needs, the test pattern compression algorithm and three kinds of x assignment algorithm are proposed. Experimental results show that the average power reductions are up to 42.36%,32.32%,38.94%,and the test length reductions are up to 77.6%,86.1%,84.3%, and then the test data storages are decreased by 79.4%,65.2%,68.1%, respectively. twisted ring counter; low power; deterministic; test pattern generator; single input change 10.11918/j.issn.0367-6234.2016.11.015 2016-01-06 国家自然科学基金(61306091, 61100031, 61340050, 61204132); 中央高校基本科研业务费专项资金资助(DUT15QT46); 黑龙江省高校重点实验室开放课题 张建伟(1978—),男,副教授 周 彬, zbhit@hit.edu.cn TN79+1 A 0367-6234(2016)11-0096-07

4 实验结果与分析

5 结 论