一种基于FPGA的多通道脉冲检测系统设计与实现

摘 要 介绍一种多通道脉冲检测系统设计方法。该系统运用Verilog HDL作为硬件描述语言,采用FPGA作为硬件平台,进行软件编程和硬件设计,完成射频信号的射频检波,A/D模数转换、DAC控制、时序控制和网络传输等功能,实现了多通道射频信号的脉冲检测。以发射老炼检测系统为应用背景,脉冲检测系统的测试结果显示,所设计的脉冲检测系统达到了理想的功能。

【关键词】脉冲检测 射频检波 A/D模数转换 DAC控制 FPGA

随着电子技术的不断发展,在通信、雷达、遥测遥感等领域中,检测技术得到越来越广泛的应用。其中,发射机的输出功率是一个重要的技术指标。通常发射机输出功率采用功率计测量,只能测量单通道射频信号功率,不能够测量多通道射频信号的功率等。其次在具体发射机系统的测试和维护中,需要对射频信号进行脉冲检测,然后将检测到的数据进行实时分析处理,从而提高系统的可靠性。因此,脉冲检测成为测试系统中至关重要的部分。鉴于对发射机信号的脉冲检测需求,本文设计了基于一种FPGA(Field Prrogrammable Gate Array)多通道脉冲检测系设与实现,其研究射频信号的功率、脉宽及周期等,具有很强的应用性,从而满足在发射老炼检测系统中的应用。

1 多通道脉冲检测系统的工作原理

多通道脉冲检测系统主要完成发射机射频信号的射频检波、A/D数模转换、DAC控制、时序控制和网络传输等功能。其原理图如图1,来自多路的射频信号经过射频检波出视频信号。视频信号经过信号调理电路分为两路,一路直接在FPGA中脉宽周期检测。另一路送A/D模数转换,在FPGA内进行多通道数据采集,检测出射频信号功率值。两路信号在FPGA内进行数据融合,融合的数据进行缓存,按TCP/IP通讯协议组帧。再通过网络接入PC机中。系统运用上位机软件显示多通道射频信号的功率值和脉宽周期的信息。

2 主要硬件电路设计及接口设计

2.1 主要硬件电路设计

其系统主要硬件电路包括:射频检波、A/D模数转换、DAC控制、网络接口芯片和FPGA电路设计。FPGA具有极大的灵活性和通用性,具有数字信号并行处理能力,开发效率高,成本低,工作稳定可靠。系统选用ALTERA公司CycnloneⅢ系列EP3C25F256C8芯片,该芯片资源丰富,体积小,接口电平多,主要完成ADC配置、DAC控制和数据融合等,可以完全满足小型微波测试系统的设计要求。射频功率测量方法多种多样,其中射频检波是检测射频信号功率的一个重要方法之一。系统选用AD公司AD8318作为射频信号的检波芯片,其频率范围可测量8Ghz以内的射频信号,动态范围精度高,芯片可以0dBm到-60dBm的射频信号进行检波,输出视频信号电平为0.3到2v。ADC控制是模数转换器,系统选用AD公司的AD7490芯片,采样精度为12位,16通道串行输出的方式,最高提供采样速率为1 MSPS。完全满足本系统需求,并方便扩展应用。根据基本采样理论,

fs≥2fH (1)

式(1)中,fs为采样率;fH为待采信号最高频率,fs选取1MS/S,这样的理论可以采样最高频率小于0.5 Mhz,对于本系统还有不少余量。DAC是数模转换器,系统选用了4片AD公司的AD5307芯片,每片芯片共有四路输出,每路输出信号最大控制电平范围可在0到2.048v,实现了视频信号的调零和门限控制。系统同时提出基于TCP/IP通讯协议。系统选用已太网控制芯片W5100,W5100是Wiznet公司推出的一款实用单片网络接口芯片[4]。W5100能够自动识别全双工或半双工的传输模式,兼容10M/100M 以太网络。其外部接带有网络变压器的RJ45座时,可实现与PC机的通讯。

2.2 接口设计

脉冲检测系统设计时,射频通道数多,控制时序复杂,集成电路接口丰富,FPGA管脚资源有限,为减少FPGA管脚资源,系统多采用串行总线和直接总线的方式。AD7490带有高速的串行接口SPI。SPI接口主要应用在A/D或者D/A转换器中,其接口占用FPGA管脚资源少,接线十分简单,不需要任何其他外接设备。网络接口芯片W5100选用直接总线模式,系统与PC机通讯时,W5100的以太网物理单元通过接收RXIP/RXIN和发送TXOP/TXON,连接到以太网中。

3 主要软件设计

脉冲检测系统是在Quartus软件环境下调试的,采用Verilog HDL语言对各硬件配置设计。上位机采用LABVIEW软件实现数据处理。系统软件框图如图2,FPGA片内逻辑的锁相环生成系统的工作时钟和采样时钟。系统工作时钟40MHz,16通道视频信号直接输入给FPGA脉宽周期检测,检测结果送到数据融合。软件产生时序去控制AD5307,改变DIN的参数值可实现视频信号的调理工作。FPGA按AD7490时序要求配置ADC,使其工作在A/D转换和数据转输周期内。W5100的控制软件使用有限状态机等,进行其硬件初始化,网络配置,查询状态,建立TCP通讯网络连接,使网络接口芯片工作在TCP/IP通讯协议下。系统具有故障报警和远程数据传输功能。

4 测试结果

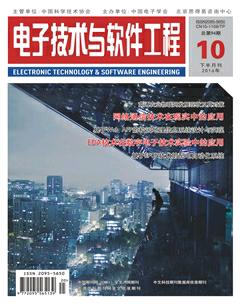

为验证脉冲检测系统,提供脉冲调制信号源,脉冲发生器和万用表等设备,设置射频输入信号脉宽100 us,周期2ms,峰值2V。系统通过SignalTap逻辑分析器验证了整个软件设计的正确性,测试单通道脉冲信号一个周期内,脉冲周期结果是2ms。脉宽测试结果如图3所示。

图3中,测试脉冲信号的幅度,设置采样时钟、采样深度和观察需要的信号。量化值为3377,脉冲信号幅度值为2.06V。用万用表测试AD电路输入为2 V。

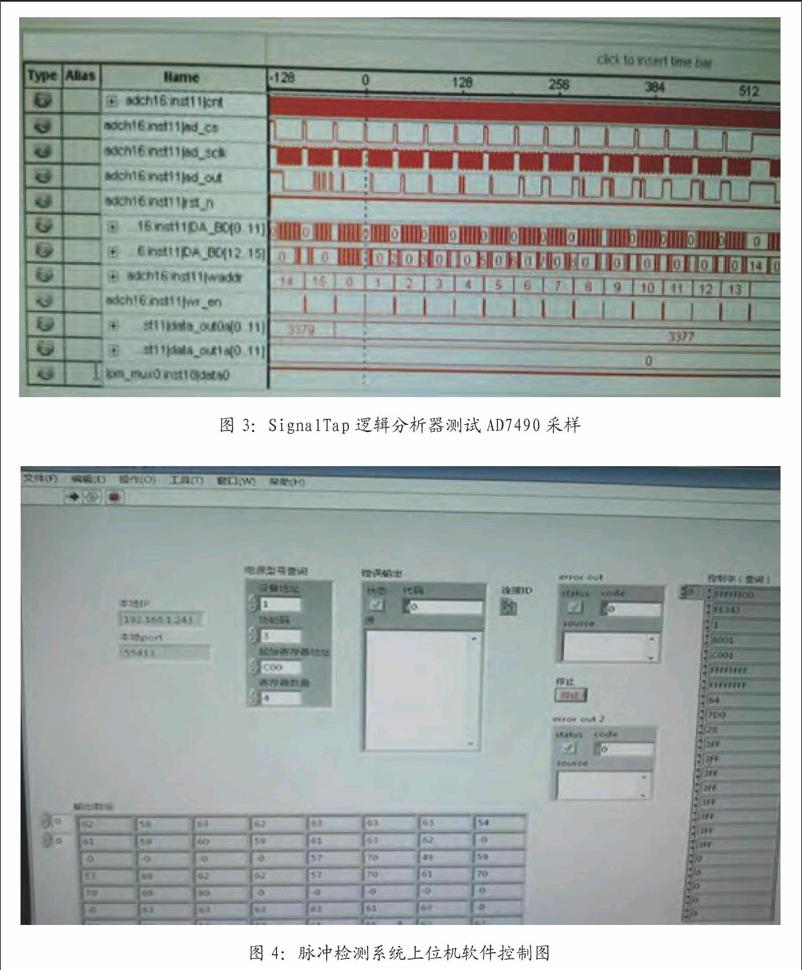

为了验证TCP/IP 通讯协议是否连接,测试网络状态等。如图4。上位机软件自动进入网络配置,计算机采用ping IP地址的方式 ,检测了系统电路设计与上位机通讯稳定可靠。

5 结语

从上述设计仿真测试结果看出,以FPGA实现多通道脉冲检测设计为平台,Verilog HDL作为开发语言,对脉冲检测进行时序控制和数据融合。以LABVIEW软件设计上位机实现数据处理和远程数据传输。其硬件设计简单,软件编程极其灵活方便,系统给出了实验结果。本系统已经成功应用发射老炼检测系统中,达到了预期的功能。整个系统具有集成度高,实用性强,适应性广的特点。

参考文献

[1]卢建良,金西,胡群超.基于FPGA的CELPACK信号采集系统设计[J].电子测量技术,2010(05):87-90.

[2]邓磊,唐高第,王锋等.基于AD8318的对数检波接收机设计[J].信息与电子工程,2007(06):190-193.

[3]杨小牛,楼才义,徐建良.软件无线电原理与应用[M].电子工业出版社,2001(01):8-11.

[4]陈实,王琪,张铁军等.一种基于W5100数据传输系统[J].电子应用技术,2013(39)9:54-56.

[5]徐伟,胡志忠,肖前贵等.AD7490与AT91RM9200的SPI接口及其驱动程序的实现[J].计算机测量与控制,2009(10):2089-2091.

作者简介

邢连营(1980-),男,主要研究方向为数字接收机及高速数据采集。

作者单位

中国电子科技集团第三十八研究所 安徽省合肥市 230088