ARINC659总线系统设计与实现*

刘宁宁,王 瑶,索高华,颜 哲

(1.中航工业西安航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点实验室,陕西 西安 710068;3.西安翔腾微电子科技有限公司,陕西 西安710068)

ARINC659总线系统设计与实现*

刘宁宁1,2,王瑶3,索高华3,颜哲1,2

(1.中航工业西安航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点实验室,陕西 西安 710068;3.西安翔腾微电子科技有限公司,陕西 西安710068)

ARINC659背板总线是一种高可靠、高容错的线性多节点串行通信总线,具有总线传输时间确定性的特点,主要用于航空电子系统中在线可更换模块 (LRM)之间的数据通信。在结合背板总线技术协议的基础上,阐述了ARINC659背板总线的体系架构,给出了在设计过程中符合 ARINC659背板总线协议规范的通信机制,并对 ARINC659背板总线设计中的关键技术进行了重点研究分析,概括了ARINC659背板总线所具备的技术特点及市场应用前景。

ARINC659;背板总线;LRM;航空电子系统;通信机制

0 引言

随着综合化航空电子系统的发展,资源共享程度越来越高,对系统的安全性、实时性也提出了更加严峻的挑战。背板总线是综合化航空电子系统中一个关键的共享资源,它不仅要具有高度的分布式处理能力和高吞吐率,还要具有各种抗干扰能力,以提高其在恶劣环境中的生存能力和安全性。ARINC659背板总线的高可靠性、高完整性等特点使其在航空计算机总线系统中更显优势,是综合化模块化航空电子系统的关键技术[1-2]。它已成为民用航空电子系统的标准背板总线,为众多民用飞机提供了新型背板总线,在国外,ARINC659背板总线技术已经相当成熟,国内对ARINC659背板总线的研究刚刚起步。

在先进综合的航空电子系统中,实现可靠、有效、通用的数据传输是其关键技术之一,ARINC659背板总线在多节点串行通信总线传输时间上具有确定性,在时间和空间上满足鲁棒子性,其特有的总线通信机制为在线可更换模块(LRM)之间的数据传输提供高可靠性保障[3-4]。

本文立足于ARINC659背板总线协议,对ARINC659背板总线体系架构进行了介绍,并阐述了ARINC659背板总线的通信机制,在此基础上着重研究分析了ARINC659背板总线系统设计与实现的关键技术,为ARINC659背板总线在我国航空电子系统中的广泛应用提供了技术保障。

1 ARINC659背板总线体系架构

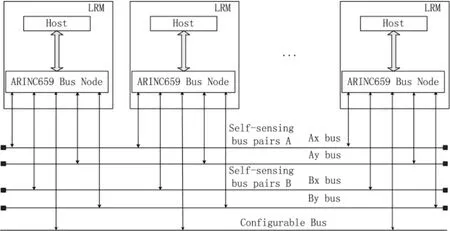

ARINC659背板总线协议中定义了 ISO/OSI模型中的物理层和数据链路层两层模型,由多个在线可更换模块(LRM)共同构成了航空电子综合化系统的体系结构,LRM之间基于ARINC659背板总线进行数据通信。

ARINC659背板总线是一个半双工传输串行数据的线性多点通信总线,系统由多个LRM模块构成,处理器模块与ARINC659总线节点共同组成LRM模块,每个LRM模块之间通过底板总线进行数据通信。图1所示为多个LRM模块构成的ARINC659背板总线体系架构,其中每个LRM模块功能包括主机接口功能、基本消息传输功能、主后备消息传输功能、总线数据容错功能。其中基本消息传输在设计中适用于选取一个模块作为数据源,其他一个或多个作为目的源之间进行通信;主后备消息设计中选用最多两个备用数据源、一个目的源之间进行通信。

图1 ARINC659背板总线的体系结构

ARINC659背板总线的 LRM模块的 ARINC659总线接口采用“双-双”余度配置的结构,包括 ARINC659总线接口单元(Bus Interface Unit,BIU)、表存储器、模块内存储器、ARINC659总线收发器等部分组成;每个LRM包含BIUx和BIUy两个总线接口单元,每个总线接口单元由A、B总线对组成,BIUx由x(Ax、Bx)总线发送数据,BIUy经由y(Ay、By)总线发送数据,每个BIU均接收来自4条总线的所有数据,且各总线分别有一条时钟线和两条数据线,因此完整的总线组由12条线组成,在数据传送过程中每条总线每次可传送2个数据位。

2 ARINC659背板总线通信机制分析

ARINC659背板总线是支持多节点的串行通信总线,其通信是采用表驱动均衡访问(TDPA)的机制,使用4条串行总线同时半双工传输和交叉校验的通信方式。设计中需要首先设计主机控制BIU收发的操作命令,再用命令表配置工具生成对应的命令表,通过编程线缆加载至外部存储器,上电后BIU自动加载命令表并按其预定的时间命令表进行总线操作。ARINC659背板总线数据通信的这种机制具备一定的同步作用,另有全分辨总线时间寄存器辅助同步机制完成,该寄存器用于计数每一位总线时间。

ARINC659背板总线数据通信功能包括:基本消息操作、主/后备消息操作;同步操作手段包括长同步消息操作、短同步消息操作。

ARINC659背板总线数据通信中基本消息用于点到点的数据传输或单LRM模块到多LRM模块的数据传输,基本消息在窗口起初就开始传输数据,其模块之间基本消息传输的数据结构如图2所示。主/后备消息用于单LRM模块和其多个备用LRM模块(最多3个)到单LRM个或多LRM模块的数据传输,主/后备消息在发送过程中采用一种简单的仲裁机制,LRM模块在通信过程中具有优先级顺序,则只有当主LRM以及其他优先级高的后备LRM模块在命令表中预定的时间内无操作时,优先级低的后备LRM才通过该窗口开始向总线发送数据,且在整个过程中对于ARINC659背板总线消息窗口,只能有一个LRM通过该窗口发送数据。

ARINC659背板总线数据通信中同步机制是表驱动均衡访问(TDPA)协议实现的基础和关键,在系统初始化总线后,短同步用于修正 BIU(总线接口单元)之间振荡器漂移,维持总线上所有BIU的同步。长同步是总线上失去同步的BIU再次与总线进行同步,按照功能可划分为初始化同步、切入同步、帧切换。初始化同步用于系统上电后或故障0后进行初始化,使总线上失去同步状态的BIU同步到初始帧的帧头;切入同步使非同步的LRM模块与当前帧同步;帧切换则用于使命令表中不同帧之间进行切换[5-6]。

图2 ARINC659背板总线介质访问机制

3 ARINC659背板总线设计关键技术

ARINC659背板总线系统设计由多节点进行数据通信,第1节中介绍了ARINC659背板总线系统的体系架构,本节首先对ARINC659总线的工作原理进行了分析介绍,再重点对ARINC659总线节点和ARINC659背板的各关键电路设计、电气特性、接口信号、物理层规范对底板和总线接口的物理隔离等特性进行了详细分析说明,以保证信号的可靠传输,确保ARINC659背板总线在遵循其协议规范的基础上达到有效应用[6]。

3.1ARINC659总线工作原理

在系统设计中,需要按照预先设定好的数据收发操作命令用ARINC659总线配置工具生成对应的命令表,通过配置总线将完整命令表的所有数据加载至系统各LRM模块的外部PROM中。当系统上电后,各LRM模块的BIU自动将外部PROM中的命令表搬到内部存储器中,加载完命令表后,BIU开始初始化,预译码命令开始按照命令表的内容执行命令[7]。

ARINC659背板总线上各LRM模块按照命令表预规定的命令进行总线数据编码、校验及传输。命令表按指令内容将总线时间划分为具有固定时间段的窗口,以满足ARINC659背板总线数据传输的同步机制。按照线协议规定,各LRM模块的4条总线(Ax、Bx、Ay、By)按照不同的编码方式进行独立的数据传输,其具体编码规则如表1所示,完成编码后将接收到的数据进行解码后并按照如表2所示的ARINC659总线数据校验表的规则再进行交叉校验,以避免来自相同BIU的总线数据可能产生关联错误而导致数据失效。

表1 ARINC659背板总线数据编码规则

表2 ARINC659总线数据校验表

在数据收发过程中,也需要对收发的数据进行自校验,即发送LRM可接收自身发送至总线上的数据按照交叉校验的方法进行自检测,如检测到不可更正的错误时,发送LRM立即保持沉默,此时次低优先级的LRM将继续向总线上发送数据;接收LRM同时接收来自4条总线上的数据并进行比较,产生的瞬时故障会立即被检测出来,且单个错误会立即被纠正,遇到不可纠正的错误时,LRM模块会立刻停止接收数据。ARINC659背板总线的这种校验机制使得总线数据在传输过程中具有高可靠性和高容错性。

3.2ARINC659总线节点设计关键技术

ARINC659总线节点包括 ARINC 659总线接口单元、时钟控制单元、表存储器、脉冲发送、接收模块等部分,在系统设计时部分设计应遵循一定的设计要求。

3.2.1时钟设计要求

ARINC659总线节点上每个BIU应使用独立的总线时钟。总线时钟频率为30 MHz,总线介质上的位传输率受每个BIU所驱动的本地时钟信号控制。系统集成者必须规定总线时钟振荡器的时钟质量和温度稳定性,即在一些温度下的精确度以及此精确度在整个温度范围内的变化范围,在整个温度范围内,时钟质量应确保总的漂移不超过50 ppm。

3.2.2表存储器单元设计要求

ARINC659总线节点设计时应使用独立通道实现表存储器维护。总线节点上的每个BIU单元单独使用1个表存储器,存储用于实现机架内LRM模块通信的ARINC659总线命令表,其两个BIU的2个表存储器可采用菊花链的方式进行总线命令表固化。

3.2.3协议处理器、收发器使能单元设计要求

在节点设计中,每个节点上必须包含的收发器使能信号应由BIU交叉控制。BIUy(控制数据线Ay和By的总线接口单元)控制 Ax、Bx总线收发器的传输使能;BIUx控制 Ay、By总线收发器的传输使能,每条总线(Ax、Ay、Bx、By)必须使用独立的收发器。不同BIU不能使用同一时钟、表存储器和任何影响总线时序的硬件。每个BIU必须有各自的时钟、外部存储器及其所有控制元件。

按照物理层规范,2个BIU在物理和电气上应被最大程度分隔开,它们之间的任何信号线都应在电气上隔离;BIU与收发器之间的任何信号线都应在电气上隔离;且每个收发器的带隙参考引脚必须经一个独立的通道和除此之外没有其他连接的连接器引脚连接到其所对应的总线地平面;返回地的信号和带隙线都必须以可能的最低阻抗通道从收发器连接到其总线的地平面。

3.3ARINC659背板设计关键技术

在ARINC659总线系统中,底板用于实现各LRM模块通过ARINC659总线通讯。ARINC659总线收发器接口和信号线连接如图3所示,包括双自检总线对和端接器,总线上每个模块中的4个收发器分别连接到4条独立的总线中的一条,且每条总线使用单独的电源。

图3 ARINC659总线收发器接口和信号线连接示意图

3.3.1ARINC659总线背板电源要求

ARINC659总线背板上端接器电源线的走线必须由一个介入其间的地平面隔开。每条总线每一端都需要通过一个单独的阻值与总线负载阻抗±5%相等的端接电阻上拉到 2.1 V±0.1 V。所有的总线线路的上拉都需要由独立的电源提供电压,从而限制了单一电源失效影响整个总线的可能性,如图4所示为底板总线端接示意图。

图4 底板总线端接示意图

3.3.2ARINC659总线背板地信号设计要求

ARINC659总线设计中应为每条总线设计单独的地平面,在尽可能范围内,这些地平面承载仅与此总线有关的电流(即仅通过此总线的收发器和端接器的电流)。所有导致地平面内的返回电流的信号线走线必须在保持总线阻抗的同时与地平面尽可能接近,且总线中任何一条信号线在0.304 8 cm以内的传输导体只能是电源、地或BTL信号,这样做是为了保证完整性和减小串扰,图5所示为ARINC659底板总线地平面设计示意图。

图5 ARINC659底板总线地平面设计示意图

4 结束语

随着技术的进步,航空电子系统不断朝着更高综合化、更深模块化的方向发展,其对系统设计的可靠性、容错性、完整性等性能有更高的要求,ARINC659背板总线是在具备通用背板总线协议规范的基础上,通过对背板总线设计过程中的关键技术分析研究,使其在采用双-双余度配置的低复杂度总线结构的设计中具有较高容错性和传输时间确定性的特点,在不降低系统可靠性的前提下降低了系统体积、重量和功耗,可以满足航空电子系统对于高可靠性、高故障容忍度、高容错性、系统小型化等要求,非常成功地实现了高度的功能综合化[8-9]。本文研究分析 ARINC659背板数据总线系统设计中的关键技术并得以实现,能够为其在我国航空航天电子系统的应用提供必要的技术保障,对于提高我国航空航天电子系统的可靠性具有重要意义,使ARINC659总线在新型航空电子、下一代空间飞行器、工业控制等领域的安全关键系统中有广阔的应用前景[3,6-8]。

[1]徐文辉.ARINC659底板总线简介[J].航空电子技术,1999,30(2):22-27.

[2]RAMAKER R,KRUG W,PHEBUS W.Application of acivil integrated modular architecture to military transport aircraft[C].The 26thDigital Avionics Systems Confer-ence(DASC) IEEE 2007:2.A.4-1-2.A.4-10.

[3]张喜民,魏婷.ARINC659背板数据总线应用研究[J].航空计算技术,2011,41(5):241-246.

[4]张喜民.ARINC 659背板数据总线协议初探[J].电光与控制,2013,20(3):93-97.

[5]李宝羽.ARINC659总线协议同步机制的研究与实现[J].航空计算技术,2009(3):42-45.

[6]田泽,刘宁宁,郭亮,等.ARINC659底板数据总线及关键技术[J].计算机应用,2013,33(S2):49-53.

[7]曹朋朋,田泽,许宏杰.ARINC659命令表配置工具设计与实现[J].计算机技术与发展,2012,22(7):178-180.

[8]刘海旭.ARINC659通信总线的设计与实现[D].北京:北京交通大学,2010.

[9]孟锐.ARINC659背板总线协议处理单元的设计[D].西安:西北工业大学,2008.

Design and realization of ARINC659 bus system

Liu Ningning1,2,Wang Yao3,Suo Gaohua3,Yan Zhe1,2

(1.AVIC Computing Technique Research Institute,Xi′an 710068,China;2.Aviation Key Laboratory of Science and Technology on Integrated Circuit and Micro-System Design,Xi′an 710068,China;3.Xi′an Xiangteng Microelectronics Technology CO.,LTD,Xi′an 710068,China)

ARINC659 backplane bus is a high level reliability and a fault tolerant cabinet linearity multi-drop communication bus,that the transmission time on bus is determinate.In the avionics electronic systems,it is used on the data transmitting between line replaceable modules.This paper introduces ARINC659 backplane bus system architecture at first,that bases on the technology protocol of the backplane bus,and gives the data bus communication mechanism which accords with the protocol specifications.Then the key technologies are analyzed as a keystone in the designing of ARINC 659 backplane bus.Finally,this paper summaries the feature and application trend of ARINC 659 backplane bus.

ARINC659;backplane bus;LRM;avionic system;synchronization mechanism

TN913

A

10.16157/j.issn.0258-7998.2016.10.040

航空科学基金(2015ZC51036);中国航空工业集团公司创新基金(2010BD63111)

(2016-07-19)

刘宁宁(1983-),女,硕士,高级工程师,主要研究方向:集成电路设计。

王瑶(1987-),男,硕士,主要研究方向:嵌入式系统硬件设计与开发。

索高华(1985-),女,本科,助理工程师,主要研究方向:集成电路设计与验证。

颜哲(1984-),男,硕士,工程师,主要研究方向:集成电路设计。

中文引用格式:刘宁宁,王瑶,索高华,等.ARINC659总线系统设计与实现[J].电子技术应用,2016,42(10):153-156.

英文引用格式:Liu Ningning,Wang Yao,Suo Gaohua,et al.Design and realization of ARINC659 bus system[J].Application of Electronic Technique,2016,42(10):153-156.