基于FPGA和USB2.0协议的通用数据传输设计

徐 超,刘 冲,王永纲

(中国科学技术大学 近代物理系,安徽 合肥 230026)

基于FPGA和USB2.0协议的通用数据传输设计

徐超,刘冲,王永纲

(中国科学技术大学 近代物理系,安徽 合肥 230026)

FPGA因其具有高度的灵活性与强大的数据处理能力而被广泛应用于数据采集与处理系统中。USB2.0因其数据传输速率快和接口的多样化而广泛使用。以USB2.0控制器CY7C68013A为接口设计和实现了上位机与FPGA中FIFO与寄存器之间的读写。经测试表明,该设计达到了47 MB/s的数据传输速率,接近USB2.0控制芯片的最高速率48 MB/s。

FPGA;USB2.0;CY7C68013A;数据传输

引用格式:徐超,刘冲,王永纲. 基于FPGA和USB2.0协议的通用数据传输设计[J].微型机与应用,2016,35(16):41-43.

0 引言

目前,系统设备不断向高速化、集成化、低功耗的方向飞速发展。而现场可编程门阵列FPGA经过这些年的发展,已经成为实现数字系统的主流平台之一。FPGA具有高度的灵活性和强大的数据处理能力,常被用来定制外设的控制器以及前端处理模块。但FPGA并没有提供和上位机之间直接通信的接口,为了更方便地对数据进行后续的分析和保存,就需要解决FPGA和上位机之间的数据传输的接口问题。

USB2.0已经广泛使用于个人电脑中,USB2.0相比于以前的USB版本在速度上有两个很大的提升。USB2.0协议具有以下优点:(1)速度快,在高速块传输,最大数据字段的模式下,最高可以达到60 MB/s[1],本文设计的块传输,512 B数据字段的模式下,可达53.2 MB/s; (2)连接简单,可即插即用;(3)可支持多设备采用“级联”方式连接外设。

本文通过USB2.0 的外设控制器CY7C68013A,实现了FPGA 和上位机之间数据传输接口的设计[2-4],经测试,该设计能够接近理论上的传输速度。

1 系统结构

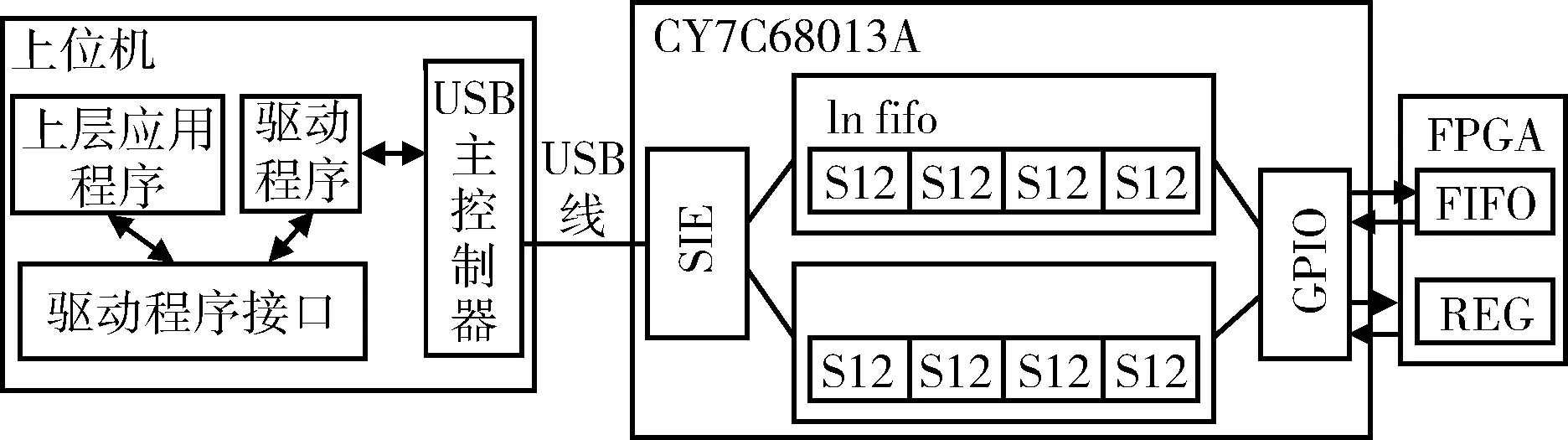

USB系统是一个主从系统,所有的命令是由主设备(上位机)发出,从设备接收到命令后,执行所要求的操作。在主设备要求读数据时,从设备才会向主设备发送数据。图1给出了整个设计的系统结构图。

图1 系统结构图

系统读写时,由上位机的应用程序发起请求,通过驱动程序接口(API)调用驱动程序。驱动程序控制USB控制器向CY7C68013A发送数据,CY7C68013A的SIE模块对数据进行解析,然后根据内部的固件程序通过GPIF模块向FPGA发送时序波形并读写数据。在对FPGA进行读写FIFO或者Register时,FPGA与USB芯片之间的控制信号由内部的GPIF决定。

2 系统软硬件组成

2.1USB2.0接口

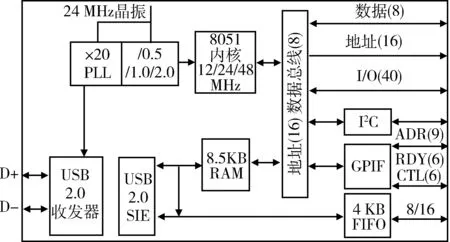

USB2.0[5]的接口芯片采用CY7C68013A。该芯片包含了USB2.0的集成微控制器,内部集成了一个增强型的8051CPU,该芯片负责配置芯片的工作方式、数据流的控制等,一个串行接口引擎SIE,解析USB协议,实现对上位机的收发,以及可编程的其他外围接口。该芯片还提供了一种独特的架构,是USB接口和应用环境共享Slave FIFOs,微控制器不需要参与数据的传输,这样就大大提高了整个系统的数据传输速率。本文采用GPIF的模式,通过对GPIF的编程实现数据的传输。EZ-USB FX2的内部结构图如图2所示。

图2 FX2内部结构图

2.2FPGA的接口设计

FPGA不仅需要和内部其他逻辑模块连接,还需要对USB的GPIF进行数据的收发。因此,为通用起见,设计FPGA接口实现对寄存器的读、写和FIFO的读、写操作。

GPIF对FPGA的控制信号CTL只有三位,能区分8种不同的状态。为了让FPGA能区分寄存器读、写(包括地址和数据)以及FIFO的读、写、空闲等7种不同的状态,CTL控制线的每种编码决定了唯一的操作状态。

2.3芯片固件程序设计

固件设计的核心是GPIF的设计[6-7],GPIF设计不当以及上位机调用不合理会导致系统的整体速度不高。

GPIF电路工作在48 MHz时钟下,数据线有16位,两个周期实现一次FIFO的读写,故理论上能够达到48 MB/s的传输速率。

本文采用了“量子FIFO”的处理结构,很好地解决了USB高速模式的带宽问题。

在GPIF高速数据传输中,GPIF波形的描述符决定了整个数据传输过程的时序。通常用Cypress公司的GPIF工具进行配置,在GPIF方式下,所有的读写和控制逻辑都可以通过软件编程的形式实现,具有很大的灵活性。

由于GPIF的状态机只能由一个状态跳转到两个不同的状态,而在FIFO读写过程中需要检测的变量和跳转的状态比较多,有时就需要进行多级跳转,这样严重限制了数据的传输速度。为解决这个问题,本文在分析了所有的跳转情况后,将正常读写FIFO的跳转次数减少,而将特殊情况跳转次数增加,使得两个时钟周期内进行一次读写操作,这样保证了功能的实现,且保证了48 MB/s的读写速度。

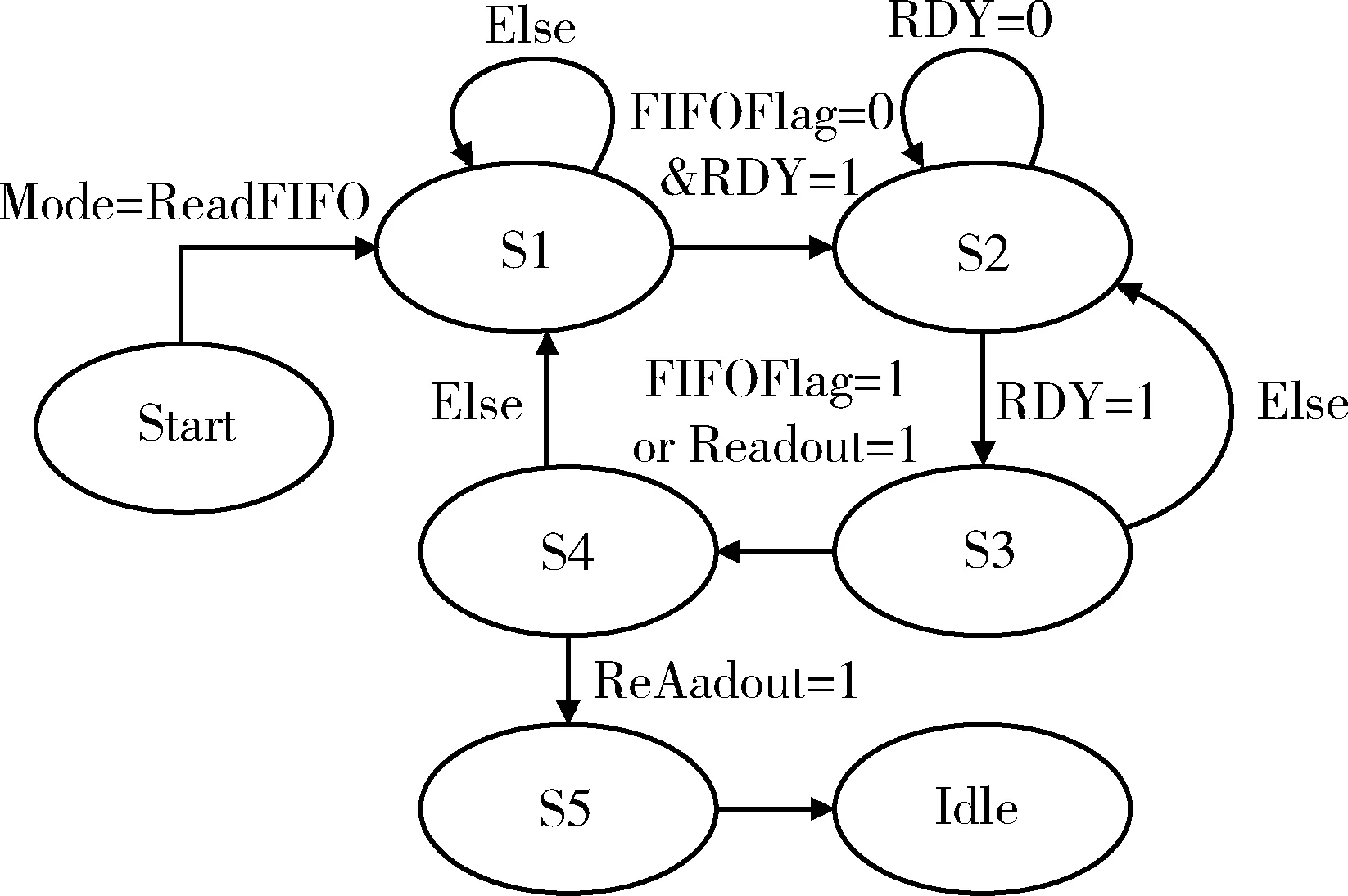

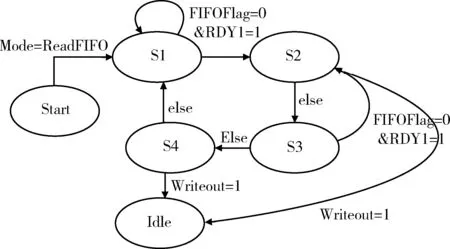

图3给出了FIFO读操作模式下设计的GPIF的状态转换示意图。当USB控制线设置为FIFO读模式时,系统进入状态S1,此时,申请FIFO数据线驱动USB数据总线,此时如果GPIF内部的FIFO没有问题且FPGA给出以准备好的信号,进入S2状态, S2申请读FIFO,FIFO可读,则进入状态S3,向USB总线发送数据,如果GPIF的FIFO没有问题且未读完,则回到状态S2,如此循环,直到数据读完。读完数据后,最终会回到空闲状态,表明本次数据传输完成。

图3 FIFO读的状态图

从上面的过程中可以看出,在两个时钟周期内完成了一个16 bit数据的传输,充分利用了USB2.0的数据带宽,提高了数据传输速率。

图4给出了FIFO写操作模式下的GPIF的转换图,与上面的分析类似,两个周期内就能够完成一次数据传输。

图4 FIFO写的状态图

2.4驱动和应用程序设计

Cypress 提供了Windows系统下的驱动,并以C++静态链接库的形式提供了调用驱动的函数库。设计中在此基础上封装了读寄存器、写寄存器、读FIFO、写FIFO四个函数,并以DLL形式提供给用户。上层使用的是MATLAB平台,需要在该平台上配置MEX编译器,并使用loadlibrary函数以加载动态链接库,加载后便可以调用DLL里提供的读写函数了。DLL也能被其他平台调用。

3 性能测试

为了验证该设计方案,本文在带有CY7C68013A和XILINX ARTIX-7 的电路板上对数据传输的正确性和传输速度进行了测试。

3.1测试方法

对寄存器的读写验证比较简单,只需先通过DLL中的读写寄存器函数对不同地址的寄存器进行写操作,然后读出来进行比对即可。

而对FIFO读操作验证,需要在FPGA的内部例化一个FIFO和一个计数器,并将计数器输出的数据从0到65 535依次写入到FIFO中,然后上层MATLAB中读到的FIFO的值就应该是从0到65 535依次递增的序列。而通过测量读取一定数目的数据的时间就可以计算出USB的读出速度。FIFO写操作的验证与FIFO读类似,不过在将数据写进FIFO后,需要由FPGA将FIFO中的数据与期望的数列比较。

3.2测试结果

本文在MATLAB平台上进行了验证,对寄存器和FIFO的读写操作完整正确,对FIFO进行读写的实测速度达到了47 MB/s,接近于理论上的48 MB/s。

4 结论

本文在USB2.0协议的基础上,设计并实现了FPGA与上位机之间的高速数据传输系统,验证了该方案传输数据的正确性并且实测速度能够达到47 MB/s,接近于理论上的48 MB/s传输速度。该方案具有稳定、高速以及调用方便的优点,目前已经应用于多个实验装置中。

[1] 王成儒, 李英伟. USB2.0 原理与工程开发[M]. 北京: 国防工业出版社,2004.

[2] 谭安菊,龚彬. USB2.0控制器CY7C68013与FPGA接口的Verilog HDL实现[J]. 电子工程师,2007,33(7):52-55.

[3] 吴振宇,常玉保,冯林. 基于FPGA和USB2.0的高速数据采集系统[J]. 仪器仪表学报,2006,27(S1):125-126.

[4] 安荣,任勇峰,李圣昆. 基于FPGA和USB2.0的数据采集系统[J]. 仪表技术与传感器,2009(3):49-51.

[5] 钱峰. EZ-USB FX2 单片机原理、编程及应用[M].北京: 北京航空航天大学出版社,2006.

[6] EZ-USB®Technical Reference Manual[EB/OL]. (2014-05-02)[2016-03-30]http://www.cypress.com/?rID=38232.

[7] Cypress CyAPI Programmer's Reference[EB/OL]. (2011-xx-xx)[2016-03-30]http://www.cypress.com/?docID=41365.

Design of general data transmission based on FPGA and USB2.0 protocol

Xu Chao, Liu Chong, Wang Yonggang

(Department of Modern Physics, University of Science and Technology of China, Hefei 230026, China)

FPGA is widely applied in the data collecting systems and data processing systems due to its high flexibility and strong ability of processing data. USB2.0 is widely used because of its high rate of data transmission and diverse interfaces. This paper designs and implements data transmission between the PC and the FIFO and registers in the FPGA which is based on the peripheral chips CY7C68013A of USB2.0. And the test shows that the data transmission rate can be up to 47 MB/s, which is very close to 48 MB/s, the highest rate of the controlling chip of USB2.0.

FPGA; USB2.0; CY7C68013A; data transmission

TP334

A

10.19358/j.issn.1674- 7720.2016.16.012

2016-03-30)

徐超(1990-),通信作者,男,硕士研究生,主要研究方向:数字电路。E-mail:xuhaimin@mail.ustc.edu.cn。

刘冲(1989-),男,博士,主要研究方向:数字电路。

王永纲(1965-),男,教授,主要研究方向:医学成像。