基于FPGA的ADC时序设计

刘亚亚

(商洛学院数学与计算机应用学院,商洛 726000)

基于FPGA的ADC时序设计

刘亚亚

(商洛学院数学与计算机应用学院,商洛 726000)

随着机器视觉领域的快速发展,图像实时处理的需求越来越迫切,而软件实现图像处理无法满足实时性的需求,且基于专用集成芯片的实现开发周期过长,开发难度过大。针对此提出一种基于FPGA的ADC时序设计。该设计以现场可编程门阵列(FPGA)为核心,在ISE10.1和ModelSim仿真软件环境下开发,在Xilinx的XC4VSX55硬件平台上实现。最终搭建图像采集与处理系统的平台,很好地实现图像的实时与处理。

FPGA;ADC;图像采集;仿真

0 引言

随着现代通信技术的发展,ADC信号的实时采样和有效处理在数字化接收机中起到重要作用[1],FPGA提供逻辑控制,虽然以传统的DSP或单片机作为CPU 的AD采样系统控制简单,但它们不适合完成对复杂的外围电路的逻辑控制,而且软件运行速度较低,而FPGA电路设计易于软件仿真,可同时进行采样控制和信号的处理[2],且能简化硬件电路,提高系统工作速度,缩短产品研发周期。针对此,基于FPGA的ADC时序设计,能更有效地提高宽带数字化接收技术,更容易硬件实现。同时该设计还具有比较好的通用性。

1 基于ADC128的时序设计系统

1.1ADC128的时序信号

ADC12要正常工作,必需获取好的时序驱动信号,而时序信号的产生需要各种频率的时钟,而系统时钟只有一个,因此,设计时钟产生功能是ADC128时序设计的基础。该模块主要用来产生内部的全局清零信号和ADC128工作所需的时钟信号。

上电初始时刻需对FPGA进行清零,清除FPGA上电初始时刻的不稳定态以使FPGA避开外围电路的不稳定状态[3-4]。接着产生系统需要的时钟信号,时钟产生模块 (CLK_CTRL)接口框图如图1所示:

图1 时钟模块接口图

FPGA工作时钟为40MHz时钟,全局异步上电复位信号和ADC128等各个模块所需的时钟信号如表1所示。

该模块内部模块分为内部上电复位信号和时钟分频模块,下面详细介绍内部模块的结构和设计。

(1)内部上电复位信号模块设计

该模块主要用来产生内部的全局清零信号。上电初始时刻对FPGA进行清零,清除FPGA上电初始时刻的不稳定态以使FPGA避开外围电路的不稳定状态。

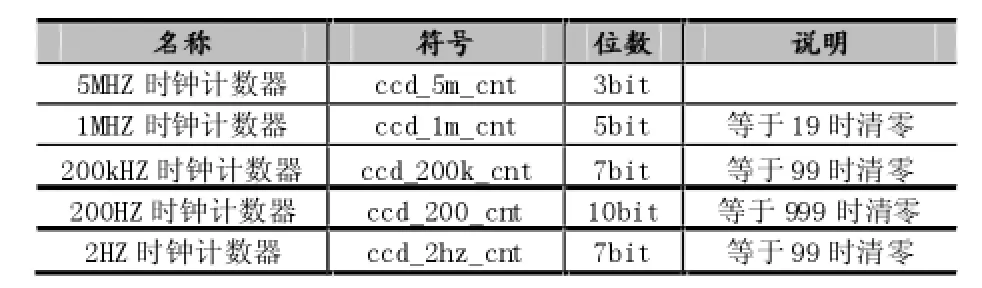

表1 信号说明

输入数据:

内部上电复位信号程序设计中用g_rst_x复位10bit的计数器,当计数器满时,即复位后又延时1024单位时间启动所有时钟。将全局时钟和内部上电复位信号均放置在全局网络上,以提高系统速度和可靠性。系统使用的中间时钟信号如表2所示:

表2 系统中间所使用的时钟信号

设计过程:

(1)5MHz时钟 (ccd_5m_clk)是对输入全局时钟——40MHz时钟进行8倍分频。每当5MHz时钟计数器(ccd_5m_cnt)的第二位的非为5MHz时钟的当前状态。即每4个40MHz时钟时间ccd_5m_clk状态变一次,周期为5MHz。

(2)1MHz时钟 (ccd_1m_clk)是对输入全局时钟_40MHz时钟进行40倍分频。每当1MHz时钟计数器(ccd_1m_cnt)记录到19时 (从零开始),即每20个40MHz时钟时间 ccd_1m_clk状态变一次,并且对1MHz时钟计数器清零,周期为1MHz时钟。

(3)200Hz时钟(ccd_200_clk)是通过输入全局时钟——40MHz时钟进行200倍分频得到200kHz时钟计数器,再对200kHz时钟计数器进行1000倍分频得到。每当200kHz时钟计数器(ccd_200k_cnt)记录到99时(从零开始),即每100个40MHz时钟时间ccd_200_cnt时钟计数器加1,并且对200kHz时钟计数器 (ccd_200k_cnt)清零,周期为400kHz时钟。每当200Hz时钟计数器(ccd_200_cnt)记录到999时(从零开始),即每1000个400kHz时钟时间ccd_200_clk状态变一次,并且对200Hz时钟计数器清零,周期为200Hz时钟。

(4)2Hz时钟(ccd_2hz_clk)是对 200Hz时钟(ccd_200_clk)进行100倍分频。每当2Hz时钟计数器(ccd_2hz_cnt)记录到99时(从零开始),即每100个400Hz时钟时间ccd_2hz_clk状态变一次,并且对2Hz时钟计数器清零,周期为2Hz时钟。

(5)内部上电复位信号(g_rst_x)为零时,所有信号清零。

在设计中的约束主要考虑时钟信号在时钟沿的一致性,在所有生成时序中都是以系统时钟的上升沿和上电复位的下降沿为变化的触发信号,这样就保证了时序的一致性。

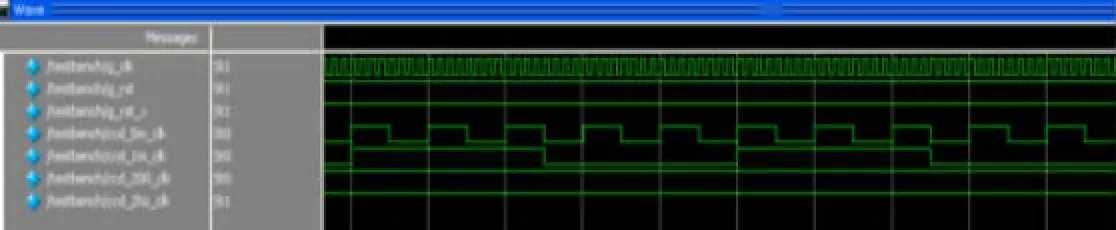

用ModelSim作的仿真结果如图2所示,可示看出结果和设计要求一致。

图2 时钟仿真结果

1.2ADC128的串行接口及实现原理

一种操作的时序图和一个串行接口时序图中显示为:ADC128S102的时序图部分。CS为片选信号,启动转换和串行帧数据传输。SCLK为串行时钟控制信号,控制转换过程和串行数据的时序。串行数据输出的串行数据输出引脚,其转换的结果是一个串行发送数据流,MSB是开始第一个数据。要写入的数据ADC128S102控制器放在DIN引脚,即串行数据输入引脚。新的数据写入DIN引脚进行转换[5]。

串行帧的开始时在CS信号的下降沿端的上升沿,每一个串行帧必须包含16个上升的SCLK边缘信号。当CS信号为高电平时ADC的DOUT引脚处于高阻状态,否则DOUT引脚处于输出状态。因此,CS相当于一个输出使能端。同样,当CS为高电平时,SCLK关闭不工作。

表3 控制寄存器位

在SCLK的前三个周期,ADC处于跟踪模式可以获取输入电压。在后来的13个SCLK周期转换的完成,数据同步输出。SCLK的第1到4个下降沿输出是0,从第5个开始一直到第16个输出的是AD转换结果,高位先输出,低位后输出。假如有多个数据需要转换,ADC将在16个时钟的整数倍处的下降沿处开始新数据的转换,再过4个时钟,进入转换结果输出阶段。

ADC128S102会在三种情况下进入跟踪模式[6]。第一种情形,当CS为低电平,SCLK为高电平时,ADC在SCLK的第一个下降沿时会进入跟踪模式。第二种情形,当CS变低电平SCLK为低电平,ADC会自动进入跟踪模式而CS的下降沿可被看做是SCLK的第一个下降沿。第三种情形,当CS和SCLK同时为低电平时,与此同时,ADC进入跟踪模式。虽然关于CS和SCLK的下降沿来说没有定时限制,但从表2中可以看出当SCLK在上升沿时为,为了建立和保持CS的低电平有效时还是有一定的条件限制。

每一次的转换中,数据是在8个SCLK上升沿CS为下降沿时存储到DIN引脚的一个控制寄存器中。控制寄存器装载指示:要转换的输入通道的数据的随后的转换。如表3,表4,表5所示。虽然ADC128S102能够获得输入信号的全分辨率的第一转换,即立即上电后第一个转换结果将是一个随机选择的通道。因此,用户需要将一个虚拟的转换设置所需要的通道,将用于所后的转换。

表4 控制寄存器位描述

表5 输入通道选择

具体的数据采集的过程如图3所示,图4所示为图3的部分放大图。当使能端(en)有效CS信号为低电平时,运用3bit可以选择6(000-101)路数据,进入转换器ADC128中进行转换。在使能端(en)有效时,ADC开始转换数据。在数字输入引脚DIN中按照一个时间周期来采集输入的数字信号,两个是一个地址。在数据输入所表示的12bit数据地址中的第3,4,5位表示数据输入的地址,取出其地址中的数据并保存在数据缓存器里,可以发现本次注入,下次转换才有效,所以从时序关系看是参数注入晚于数据输出。

图3 数据采集过程

图4 数据采集过程放大图

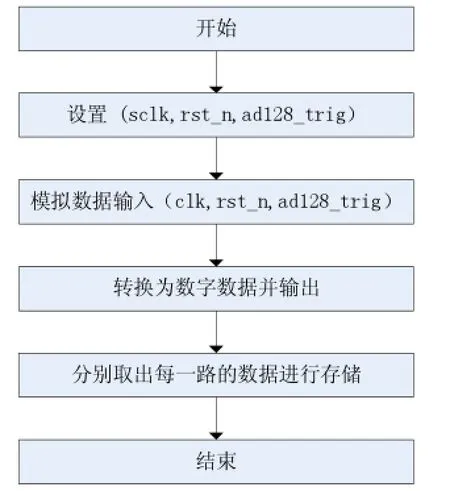

1.3程序流程图

图5所示表示的是进行程序设计的流程图。叙述了程序进行到哪一步所要执行的主要职责和作用。

2 基于FPGA的硬件实现

ISE的主要功能包括设计和规划,设计输入、综合建设网表、功能仿真、实现和下载到硬件电路中,涵盖了FPGA开发的全过程,从功能上讲,其工作流程无需借助任何第三方EDA软件[7]。

设计和规划:设计FPGA所要实现的功能然后规划模块及模块接口[8]。

图5 程序流程图

设计输入:用Verilog HDL硬件语言来描述硬件电路所要实现的功能,并把它加载到模拟仿真软件中。

综合建设网表:把Xilinx本身自带的综合工具和其他公司的综合工具进行无缝链接。

功能仿真:把模块好的硬件语言加载到ISE中,实现仿真,验证是否可以实现功能仿真。

实现:把实现好的程序加载到硬件电路中,查看其在ADC128工程运行的硬件环境。

3 结语

本文根据彩色图像采集系统的发展趋势,结合实际工程项目,研究并设计了一套基于FPGA的ADC时序设计图像实时采集系统,系统性能优良,开发难度较小。因此,具有广阔的应用空间。

[1]王志刚.基于FPGA的高速数字化接收机与处理技术[D].南京:南京信息工程大学,2009:1-2.

[2]许孟杰,刘文臣,刘云.基于FPGA的AD采样设计[J].舰船电子工程,2015,35(1):34-36.

[3]贺秋实,郝国法,钱龙.基于FPGA的高速AD转换[J].电子设计工程,2012,20(8):122-124.

[4]王晓.宽带数字监测接收机算法研究及硬件实现[D].成都:电子科技大学,2011.

[5]李华.基于FPGA的图像发生器的设计[J].商洛学院学报,2015,29(4):15-19.

[6]李戈,夏威,李雷.基于FPGA的ADC的自检系统[J].仪表技术与传感器,2015(2):51-53.

[7]侯伯亨,顾新.VHDL硬件描述语言与数字逻辑电路设计[M],1999:3-7.

[8]肖文娟.基于FPGA的多高分辨率彩色实时成像系统设计[[J].半导体光电,2015,36(2):293-298.

Design of ADC Timing Based on FPGA

LIU Ya-ya

(College of Mathematics and Computer Application,Shangluo University,Shangluo 726000)

Along with the rapid development in the field of machine vision,the requirements of real-time image processing has become more and more urgent,and unable to meet the needs of real time image processing software,and based on the realization of the special integrated chip development cycle is too long,difficult to develop.Proposes a ADC timing design based on FPGA,the design takes the field programmable gate array(FPGA)as the core,uses ISE10.1 and ModelSim simulation software environment,in Xilinx XC4VSX55 on the hardware platform.Eventually sets up a platform for the image acquisition and processing system,realizes the real-time and processing of the image.

FPGA;ADC;Image Acquisition;Simulation

1007-1423(2016)27-0046-05DOI:10.3969/j.issn.1007-1423.2016.27.012

刘亚亚(1981-),女,陕西商州人,硕士,讲师,研究方向为计算智能和模式识别

2016-07-05

2016-09-15

陕西省教育厅自然科学研究计划项目(No.2013JK0597)、陕西教育科学“十二五”规划2014年课题(No.SGH140749)