一种CMOS工艺高速端口的ESD保护设计

孙云华,邹家轩,2

一种CMOS工艺高速端口的ESD保护设计

孙云华1,邹家轩1,2

(1.中国电子科技集团公司第58研究所,江苏 无锡 214035;2.西安电子科技大学微电子学院,西安 710071)

随着CMOS工艺的不断深化,CMOS器件开启速度越来越快,有利于设计出更高速的电路及相关接口器件。但随着CMOS工艺深化的同时,器件的栅氧厚度也越来越薄,栅氧的击穿电压大大降低,使得器件更容易受到ESD损伤。采用传统的ESD结构会显著增加节点电容,节点电容的增加会限制电路接口速率的增加。采用中芯国际(SMIC)0.13μm工艺,设计实现了一种ESD保护电路,I/O端口翻转速率达到2 Gbps,对人体模型耐压达到2000 V。经过仿真验证、流片验证,设计的结构达到了该芯片抗静电能力以及端口高速传输速率的要求。

ESD;高速端口;GGNMOS;NTNMOS

1 引言

伴随着CMOS工艺的深化、技术的进步以及工艺的改进,微电子器件的特征尺寸越来越小[1],集成度越来越高,越来越多的功能器件,如高密度计算、网络通信、密集图像处理、海量数据传输等器件被设计出并得到广泛的应用。然而,随着工艺的改进,栅氧厚度越来越薄[3],使得栅氧的击穿电压能力显著降低[6],微电子元器件对静电变得更加敏感,ESD保护电路的设计成为集成电路可靠性设计的重要部分。

目前,ESD保护电路主要采用栅接电源、地GG-MOS电路,通过栅接地NMOS、栅接电源PMOS和可控硅实现[2],这种方法存在占用电路面积大、抗静电能力有限、端口寄生电容大等问题。

针对这些不足,为了保证高速传输芯片能够正常工作而不被静电损坏,本文采用中芯国际(SMIC)0.13 μm工艺,设计一种基于CMOS工艺的高速端口ESD保护电路来保护芯片,相比GG-MOS,在采用相同尺寸的情况下,明显大幅提高了芯片的ESD保护能力。同时,新型ESD保护电路占用的芯片面积更小,功耗更低。这样既能满足I/O端口传输速率达到2 Gbps高速的要求,又能满足对人体模型耐压达到2000 V的要求。

2 ESD保护电路工作原理

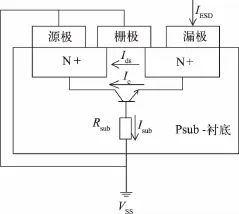

ESD是英文Electrostatic Discharge(静电放电)的简称[2],它的产生通常是由于摩擦作用使物体带上静电,当带电物体接近或者接触另一物体时,由于存在电势差,电荷便会由一个物体转移到另一个物体,在转移的过程中可能会发出响声甚至有电火花出现。目前在ESD保护电路中,应用最成熟、最广泛的结构是GG-MOS管,将NMOS管源级、栅极和衬底接到地(GG-NMOS),将PMOS管源级、栅极和衬底接到电源(GG-PMOS)。其电路结构如图1所示。重点介绍GG-NMOS,剖面图如图2所示。

图1 电路图

图2 GGNMOS剖面图

在正常情况下,晶体管GG-NMOS处于关断状态,不会影响电路的正常工作。当在I/O端口上施加一个正的ESD瞬态脉冲时,GG-NMOS的漏极和衬底之间的PN结开始反偏。随着电压的增加,当漏极和衬底之间的PN结两端反偏并发生雪崩击穿,漏极大量的空穴向衬底流动,形成了漏源电流Ids,导致衬底电位上升[1]。随着衬底电位的不断上升,源极和衬底间的电位差超过源衬之间的PN结导通电压。这时,衬底寄生的横向NPN晶体管就开始正向导通。随着ESD泄放电流Ic的增加,集电极电压开始下降,随着电压的降低晶体管进入回退区,这时晶体管的电阻很小,电流不断增加,对ESD瞬态电流进行放电。同时I/O端口上的电压被钳制到回退保持电压,保持电压小于栅氧的击穿电压[5],寄生NPN管开始自偏置工作,ESD电流中相当一部分由NPN管提供,ESD产生的电流从衬底向源极流动,电流的驱动能力比表面沟道到导通时要强很多,一直持续到NMOS发生二次击穿。要想使GG-NMOS结构的ESD电路具有更强的抗静电能力,需要设法降低开启电压并提高二次击穿电压[1]。降低开启电压是为了保护电路在ESD损伤内部电路之前起作用,避免内部电路受到损害;提高二级击穿电压是避免保护电路二次击穿而失效。同样,当I/O端口施加一个负的ESD瞬态脉冲时,晶体管GG-PMOS起作用,因此图1所示的ESD保护电路可以提供正向和负向两种方向的ESD保护能力[7~8]。

通常情况下,GG-MOS结构采用插指型晶体管多个并联结构以提高二次击穿点电压,由于工艺偏差,每个管子的开启速度不一样,导致有些管子还没开启,其他管子就已经二次击穿了[9],使得保护电路的抗ESD能力下降。因此必须使用栅耦合的方法来解决插指型GG-MOS开启速度不一致而降低抗ESD能力的问题,这样就增加了芯片的面积,增加了寄生电容,不利于芯片端口高速数据的传输。

3 新型高速端口ESD保护设计

在高速传输电路中,端口的传输速率较高,对电容的敏感度大大增加,端口电路结构的寄生电容严重影响了电路的传输速率。本文提出的新型ESD结构如图3所示,采用NMOS触发NMOS结构(NTNMOS),能够有效解决高速传输端口的ESD防护问题,又能大大降低端口ESD保护结构带来的寄生电容影响端口的传输速率。

图3 NTNMOS电路结构

由图3分析得知,在正常工作状态下,M0、M1、M2、M3、M4都处于关断状态,不会产生漏电现象,影响电路正常工作。当遭受正向ESD脉冲时,静电电压将被施加M2、M3的漏极,使得漏极电压增大,漏衬之间的PN结反偏并产生雪崩击穿,大量的空穴向衬底流动,M3管子给M2提供衬底电位,导致了M2衬底电位迅速上升,源极和衬底间的电位差超过源衬之间的PN结导通电压时,衬底寄生的横向NPN晶体管就开始正向导通,下方ESD电流随着电流的增加,集电极电压开始下降,随着电压的降低晶体管进入回退区,这时晶体管的电阻很小,电流不断增加,对ESD电流进行泄放。同样,当端口遭受负向ESD脉冲时,同样能够对ESD电流进行泄放。

在传统的ESD保护电路设计中,为了降低GG-MOS管的击穿电压,提高ESD泄放电流速度以达到保护内部电路的目的,增加了漏区扩散区的面积,同时也增加了寄生电容,影响了端口的传输速度。对新型的ESD保护电路,由于采用NTNMOS结构,大大减少了衬底电位上升的时间,通过M3直接提供一个很高的衬底电位来触发M2寄生的NPN以泄放ESD电流。

相比较而言,GG-MOS结构需要采用GG-NMOS和GG-PMOS才能同时实现对ESD正负脉冲的保护,同时由于GG-PMOS的寄生PNP对电流处理能力更差,其对负脉冲的防护至少需要消耗2倍以上的版图面积。图3中NTNMOS结构在端口通过M1、M2、M3三个NMOS就可以同时实现ESD正脉冲及负脉冲的保护,而无需采用面积代价更大的GG-PMOS提供负脉冲防护,因此其典型工作模式下端口寄生电容更小。

通过仿真模拟新型ESD保护结构的ESD电流泄放能力,如图4所示。

表1 端口电容仿真对比

图4 ESD泄放能力仿真

从图4可以看出,在端口施加一个8 kV的脉冲波,该结构能够迅速泄放电流,泄放能力达到了5 A,与此同时端口电压迅速被钳位到NMOS栅氧击穿电压以下,验证了新型ESD保护电路泄放ESD电流的能力。

4 版图布局及流片后测试结果

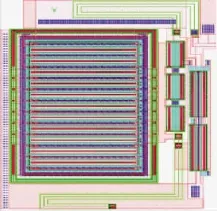

为了验证本文中设计的新型保护电路的性能,采用中芯国际(SMIC)0.13 μm工艺对电路进行流片(见图5),与相同宽长的GG-NMOS结构相比较,芯片面积减少了一半。

图5 新型ESD保护电路版图

在测试新型ESD保护电路和GG-NMOS的抗ESD能力时,测试结构分别如图6、7所示。对比两图可以发现,新型ESD保护电路相对于GG-MOS电路具有更低的开启电压,而且二次击穿电压比GG-NMOS电路有所增加,抗击ESD的能力明显增强,新型ESD保护电路的开启电压远小于二次击穿电压,这能够保证ESD保护电路自身安全地工作。

图6 NTNMOS结构ESD试验结果

图7 GG-MOS结构ESD试验结果

采用2 Gbps的翻转速率对GG-MOS保护的I/O口及NTNMOS保护的I/O口进行了抖动测试,测试结果如图8、图9所示,新型ESD保护电路NTNMOS结构的抖动更小,说明其端口电容更小,阻抗一致性更好。

图8 采用NTNMOS保护的I/O抖动测试结果

图9 采用GG-MOS保护的I/O抖动测试结果

5 结论

文中基于ESD保护电路的原理,设计了一种新型的ESD保护结构(NTNMOS),实现对ESD正负脉冲防护的结构;分析了该结构的工作原理,并通过仿真验证和流片验证。测试结果表明该结构比普通的GG-MOS具有更强的ESD保护能力,同时占用的面积明显减小;通过抖动试验验证了新型的ESD保护结构(NTNMOS)具有更小的端口电容,更利于高速端口的数据传输。该结构被应用于速率达2 Gbps的高速接口芯片中,经验证可以提供更好的ESD保护。

[1]沈放,陈魏,黄灿英,等.一种CMOS新型ESD保护电路设计[J].现代电子技术,2015(24):128-131.

[2]任志伟,崔艾东.栅接地NMOS管的ESD特性研究[J].微处理机,2015(1):5-6.

[3]王大睿.CMOS电路中ESD保护结构设计[J].中国集成电路,2007(6):37-41.

[4]徐伟,冯全源.多指条形GG-NMOS结构ESD保护电路[J].微电子学,2009(1):60-63.

[5]李志国,余天宇,张颖,等.基于RS触发NMOS器件的ESD电路设计[J].半导体技术,2014(8):579-583.

[6]赵丹.分析电子通信产品的ESD防护设计[J].科技展望,2015(14):173-174.

[7]王怡飞,胡新伟,郭立.CMOS片上电源总线ESD保护结构设计[J].半导体技术,2008,33(6):524-526.

[8]HEChuan,JIANG Ling,FAN Huang,et al.Increasing substrate resistance to improve the turn-on uniformity of a high-voltageulti-fingerGG-nLDMOS[J].JournalofSemiconductors,2013,1:1-3.

[9]刘瑶,高英俊.ESD应力下深亚微米GGNMOS二次击穿物理级建模仿真[J].微电子学,2015(6):804-807.

ESD Protection Design for CMOS High Speed I/O

SUN Yunhua1,ZOU Jiaxuan1,2

(1.China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214035,China;2.School of Microelectronic,Xidian University,Xi′an 710071,China)

While the development of deep-submicron process has been bring about possibilities for higher-speed CMOS ICs and interfaces,the plummeted VBR due to ever-lessening device gate oxide thickness may increase the risk of ESD damage.The application of the original ESD circuit will lead to a huge junction capacitance limiting the interface ports transmission rate.The article introduces an advanced ESD circuit using SMIC 0.13 μm process to enable 2 Gbps transmission rate and 2000 V ESD protection voltage against the human body model.The simulation and tape-out verify that the design meets the required standard.

ESD;high-speed I/O;GGNMOS;NTNMOS

TN432

A

1681-1070(2016)09-0014-04

孙云华(1987—),男,江苏丹阳人,工程师,现供职于中国电子科技集团公司第58研究所,主要从事大规模数字电路版图设计、ESD防护设计与研究工作;

2016-4-21

邹家轩(1982—),男,博士,就读于西安电子科技大学微电子与固体电子学院,供职于中国电子科技集团公司第58研究所,主要从事抗辐照高速串行接口设计与研究。