基于FPGA的JPEG编码器设计

陈双燕

(闽南理工学院电子与电气工程学院,福建石狮362700)

基于FPGA的JPEG编码器设计

陈双燕

(闽南理工学院电子与电气工程学院,福建石狮362700)

讨论了基于FPGA的JPEG编码器的设计原理,完成了各模块的设计,并在ModelSim平台上对代码进行了仿真,实现了图片的JPEG编码,最后在Quartus II平台上进行综合。仿真结果表明该设计方案能较好地实现图像压缩。

FPGA;JPEG编码器;2D-DCT

JPEG图像压缩技术,可以在不显著影响图片质量的前提下,减少图像的存储空间[1]。较之于相同图像质量的GIF、TIFF、PCX等图像文件格式,JPEG是压缩比最高的[2]。以JPEG压缩算法为核心的图像压缩芯片可以应用于数码相机、扫描仪、卫星通信中,具有良好的应用前景。由于FPGA具备现场可编程特性,用FPGA实现JPEG编码器,可缩短设计时间,实现实时信号处理[3]。

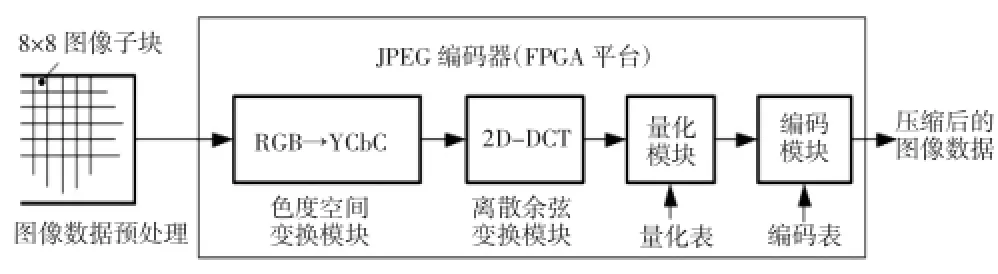

1 JPEG编码系统总体方案

JPEG编码系统由原始图像数据预处理、色度空间变换、二维离散余弦变换(2D-DCT)模块、量化模块和编码模块组成,如图1所示。其中原始图像数据预处理是在Maltab平台上完成的,JPEG编码器是用FPGA实现的,采用Verilog HDL硬件描述语言进行设计,并在ModelSim平台上进行仿真测试,在Quartus II平台上进行设计的综合。

图1 JPEG编码系统框图

2 JPEG编码器各模块设计

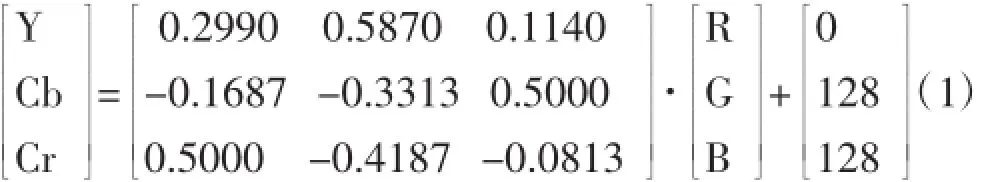

2.1色度空间变换模块

彩色图像的每个象素点一般具有RGB三个色彩分量。由于人眼对亮度变化比色彩变化更敏感,因此要进行色度空间变换,将RGB信号变换为亮度和色差信号YCbCr(Y为亮度分量,Cb为蓝色色度分量,Cr为红色色度分量)。转换公式如公式(1)所示。

由于在运算过程中包含小数,为避免不必要的FPGA资源浪费并提升运算速度,进行代码设计时,将系数乘以214,得到运算结果后,再将Y、Cb、Cr的值右移14位,输出到二维离散余弦变换模块。

2.2二维离散余弦变换模块

离散余弦变换能极大地去除图像元素在变换域中的相关性,为高效率的图像压缩奠定基础。设X(m,n)为二维图像信号数据矩阵,m、n为象素空间坐标,则其2D-DCT定义为[4]:

其中,M、N为图像子块的大小,对于8×8的图像子块,则M=8,N=8;u、v为象素频域坐标,u=0,1,…,N-1;v=0,1,…,M-1.

C(u)和C(v)为正交化因子,其是为了保证交换基的规范正交性而引入的,

在进行2D-DCT模块的FPGA设计时,以亮度分量Y为例,利用公式(3)进行2D-DCT.

其中,T是DCT系数矩阵;inv(T)是T的转置矩阵;Y是8×8图像子块的亮度分量矩阵;DY是经过2D-DCT运算后的结果。

由于T矩阵都是小数,为了避免浮点数的复杂运算,因此将T矩阵的值乘以214,然后将T与Y矩阵相乘。在计算DCT之前,一般要把输入图像的象素值减去128,令其取值范围从[0,255]移到[-128,127]。本次设计未将Y、Cb、Cr的值减去128。T矩阵的第一行系数都是0.3536,乘以214后是5793,最后将DY的第一行(即T矩阵的第一行与Y矩阵的8列相乘后的结果)减去5932032(128×8×5793)。由于T矩阵除了第一行外的其余七行的系数都具有具有对称性,每一行加起来之和为0,因此不需要减去5932032。因此,原本需要64次减法,就可以减为8次减法运算。

2.3量化模块

2D-DCT后的Y、Cb、Cr的值可用8×8的量化表进行均匀量化,量化表中的每个元素是1到255之间的整数,表示对应的量化步长。量化是有损压缩,用户可以修改量化表来控制压缩质量,以亮度分量Y为例,其按公式(4)进行量化,Q(u,v)为亮度量化表。

通常亮度分量和色差分量各有一张量化表,如图2所示[2],而且对色差分量的将忽略更多的高频成分。如果把图2中的量化步长除以2,那么图像质量就接近完美了。

图2 常用的亮度和色度量化表

为了验证该压缩编码器的性能,本次设计还采用了最低量化步长的量化表,即量化表中的元素全是1。

2.4熵编码模块

JPEG压缩的最后一步是对量化后的系数进行熵编码。这一步采用通用的无损数据压缩技术,对图像质量没有影响。

由于2D-DCT后低频系数集中在8×8矩阵的左上角,因此在进行熵编码之前,先采用“Z”字型扫描,将8×8矩阵变为一维数组,令低频系数在前,高频系数在后。因为高频系数中有很多“0”,为了节约空间,所以交流系数的“中间符号”用零行程码(Zero Run Length)表示。本次设计采用霍夫曼编码来减少熵[5-6]。

3 JPEG编码器的仿真验证

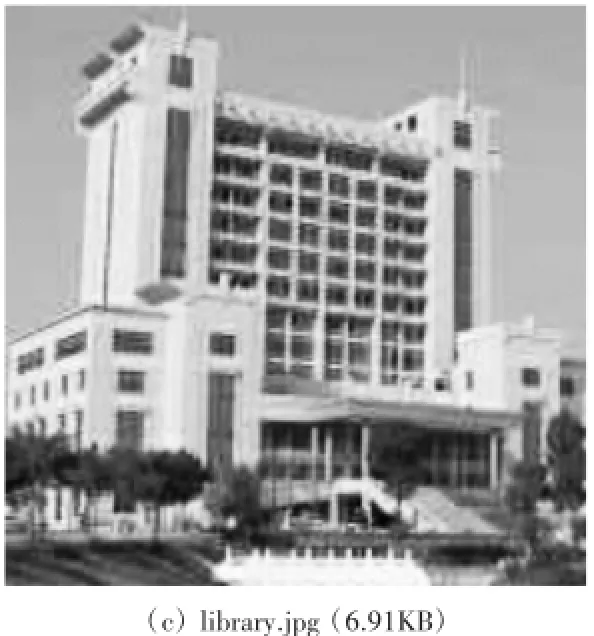

3.1原始图像数据预处理

选取一幅闽南理工学院图书馆的原始照片library.bmp(大小为91KB,尺寸为176×176象素),在Matlab平台中,将照片划分为8×8子块,再逐行逐列读取图像子块的RGB三个分量,每个分量是8bit,因此每个象素为24bit,以十六进制按顺序存储在library.mif文件中,如图3所示。library.mif文件开头说明了存储的数据个数、每个数据的宽度、存储地址和数据的进制格式。接着是图像数据,每一行是一个像素的RGB数据。

图3 原始图像数据

在Quartus II平台上生成一个ROM存储器(bmprom.v),存储空间为32768个数据,每个数据24位。在bmprom.v中,在altsyncram_component.init_file这一项中进行library.mif文件路径的设置,将library. mif导入存储器。

3.2 JPEG编码过程

JPEG编码器顶层模块(jpeg_top)包括jpeg_datain、bmprom、RGB2YCbCr、yd_q_h、cbd_q_h和crd_q_h几个模块,如图4所示。

图4 JPEG编码器的FPGA框图

由jpeg_datain模块产生读使能信号和地址信号进行bmprom数据的读取。读取规则如下:以64个图像数据为一组,当读到每组的最后一个数据时,令flag=1,接着等待16个系统时钟(等这一组的数据编码完成)后,令flag=0,再读取下一组64个图像数据。当将要读到最后一组图像数据时,令数据结束信号end_of_file_signal=1。

RGB2YCBCR模块负责图像数据的色度空间变换,yd_q_h、cbd_q_h和crd_q_h分别是Y、Cb、Cr分量的2D-DCT变换、量化、编码模块。

编码结果存放在JPEG_bitstream中,当数据有效信号data_ready为高电平时,JPEG_bitstream输出数据有效。JPEG_bitstream[31:24]是第一个编码后的数据,其次是JPEG_bitstream[23:16],接着是JPEG_bitstream[15:8],最后一个数据是JPEG_bitstream[7:0]。

3.3 JPEG编码结果

在代码测试文件中,将JPEG编码结果按顺序以十六进制存放在lib.txt中,每8位数据空一个空格。为验证编码结果是否正确,将JPEG编码器输出的数据加上JPEG表头和结尾(FF D9),另存为.jpg文件。图5(a)为原始图像;图5(b)为采用最小量化步长(量化表的值都为1)得到的压缩图像,压缩后的图像大小为原始图像的56%;图5(c)为采用图2所示的量化表得到的压缩图像,压缩后的图像大小为原始图像的7.59%.

(续下图)

图5 JPEG编码结果

3.4设计综合结果

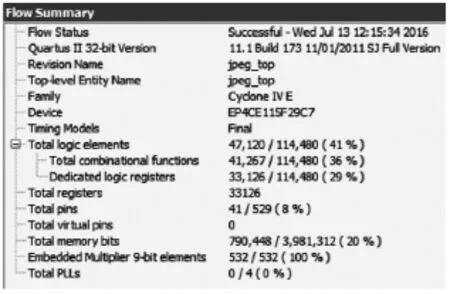

在Quartus II平台上进行了设计的综合,采用图2所示的量化表综合的结果如图6所示。

图6 JPEG编码器综合结果

4 结束语

本文详细阐述了基于FPGA设计的JPEG编码器,并在2D-DCT环节进行了优化运算,最后实现了图像的压缩,正常情况下,压缩后的图像大小为原始图像下的7.59%,并且在Quartus II平台上进行了设计的综合。

[1]龙燕,何东健,宋怀波.基于GAP-RBF神经网络的JPEG编码图像质量评价[J].小型微型计算机系统,2013,(1):185-188.

[2]王艳.基于FPGA的JPEG硬件解码器设计及实现[D].重庆:重庆大学,2011.

[3]徐洁.基于FPGA的JPEG图像压缩系统的实现[D].大连:大连理工大学,2013.

[4]云鹏.基于FPGA的图像采集与JPEG压缩编码的研究[D].呼和浩特:内蒙古大学,2010.

[5]马剑钊.基于FPGA的JPEG编码算法的优化设计与硬件实现[D].长沙:中南大学,2008.

[6]宫泽林.基于JPEG图像压缩及其仿真实现[J].中国科技信息,2013,(11):84.

Design of JPEG Encoder based on FPGA

CHEN Shuang-yan

(School of Electronics and Electrical Engineering,Minnan Institute of Technology,Shishi Fujian 362700,China)

The principle of JPEG Encoder based on FPGA was discussed in the paper.Each module of the JPEG encoder was designed,and the code was simulated in modesSim platform,then the JPEG encoding of the image was achieved,and finally the design was compiled successfully in quartus II platform.The simulation results showed that the design was able to achieve image compression well.

FPGA;JPEG encoder;2D-DCT

TN911

A

1672-545X(2016)08-0252-03

2016-05-19

福建省中青年教师教育科研项目资助(编号:JB14120)。

陈双燕(1986-),女,福建福清人,讲师,硕士,从事电子信息技术领域的教学与研究。