基于FPGA的图像采集无线传输系统的设计与实现

张玉江,李月强,祁凤

(北京信息科技大学仪器科学与光电工程学院,北京 100192)

基于FPGA的图像采集无线传输系统的设计与实现

张玉江,李月强,祁凤

(北京信息科技大学仪器科学与光电工程学院,北京100192)

0 引言

随着图像的采集处理在军事、医疗、工业、农业、安保监控领域的广泛应用,许多图像采集处理芯片也相继推出,这些芯片处理功能也越来越强大,当然使用起来也越来越方便。数据量大、耗时多是图像采集处理系统的特点,为了更好地解决这些问题,提高图像采集及处理传输的速度,本系统核心控制芯片采用功能强大的FPGA芯片EP4CE6E22C8,采用这款FPGA主要有以下几个优点,第一,支持与时钟频率相同的采样频率;第二,支持可重构技术;第三,系统外围电路简单,体积减小,使用方便。本系统一大优点是采用了无线传输模块,这使得在一些有线无法传输的情况下,本系统也可以实现图像的实时采集与传输,大大增强了本系统的实用性以及应用广泛性。本系统主要是通过MT9M9001 CMOS图像传感器采集图像通过FPGA控制,经USB2.0传输或无线传输把图像传输到PC进行图像进一步处理。

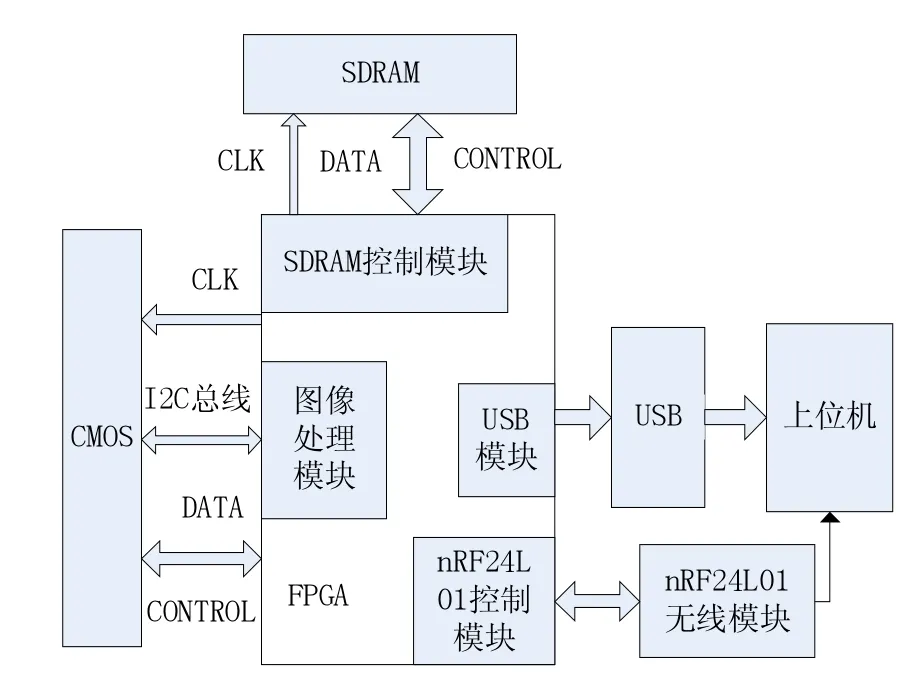

1 系统总体设计

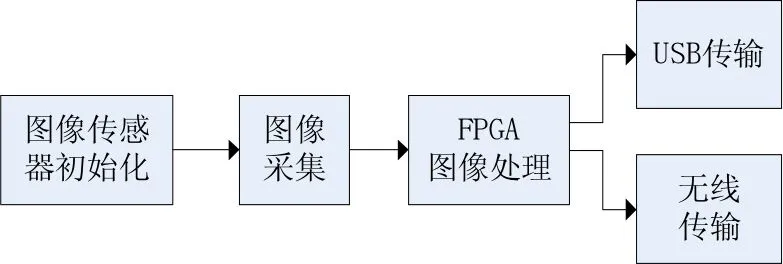

本系统采用Micron公司的MT9M001作为本系统的图像传感器,采用I2C总线作为核心控制芯片FPGA与CMOS图像传感器MT9M001的通信总线。采用美国ATERA公司的FPGA芯片EP4CE6E22C8作为整个系统的核心控制芯片,FPGA主要负责图像采集模块、图像处理模块和数据缓存模块、图像传输模块的控制。工作的整个流程首先FPGA通过I2C总线实现对图像传感器MT9M001的初始化配置,通过对其内部寄存器的参数配置设置图像的输出方式和图像格式,然后通过FPGA设计的时序驱动来控制MT9M001图像传感器的图像采集,图像采集到FPGA后通过线性插值图像处理方法进行图像处理,未处理的暂存到SDRAM内,实现帧缓存,最后通过USB2.0或nFR24L01无线传输模块传输图像至PC进行后续图像处理。本系统整体框图如图1所示。

图1 图像采集系统整体框图设计

2 硬件选型及设计

2.1图像传感器的选择及硬件电路设计

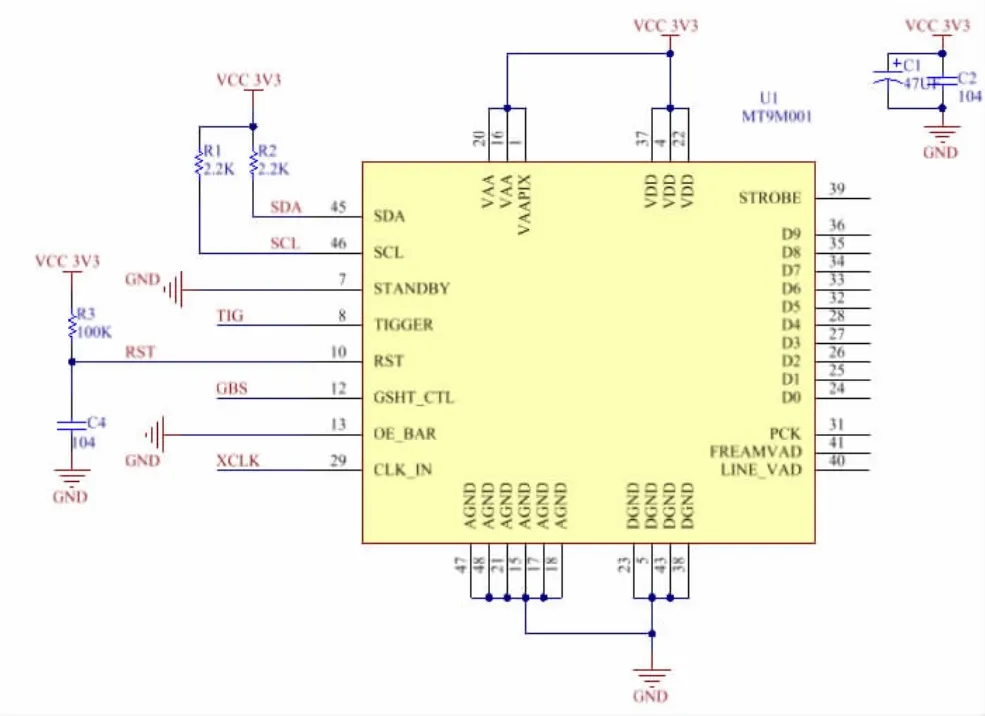

由于监控、安保。医疗使用环境都比较严苛,CMOS相比于CCD更容易适应严苛的环境,CMOS在集成方面的优势已经展现的非常明显,近几年CMOS工艺也在不断改进,在可靠性方面由于CMOS集成度高,所需的电路、器件一般都会集中在一块芯片上,与外界的焊点少,不容易出现问题,在灵敏度方面CCD的有效成像面积要大于CMOS,所以在灵敏度上一般也会大于CMOS,近几年,新一代CMOS在每个像元中都采用高增益互补放大电路,填充因子已大大提高,灵敏度已不亚于CCD,在功耗方面CMOS集成度高,体积也更小,在同样电路实现同样功能下,CMOS的功耗一般会更低,响应速度方面CCD采用穿行扫描工作方式,需要逐个读取电荷信息,这种工作方式响应速度相对比较慢。然而,CMOS采用单点信号传输,可以一次读出整帧的图像信息,所以响应速度就会比较快,CMOS的成本也显然更低,所以本系统采用CMOS图像传感器MT9M001作为本系统的图像传感器。

MT9M001芯片采用CLCC封装,共有48个引脚,主要包括:串行接口、数字逻辑控制、模拟I/O口、数字图像接口、系统时钟和电源线,它的像素值为130万,分辨率为1280H×1024V,最高每秒30帧,正常采图能达到25帧每秒,最大数据传输速率为48MPS,内置A/ D转换器分辨率为10位,工作功耗325mw,支持CIF、QVGA、QCIF、VGR等不同的输出格式,通过串行总线还可以调节帧频增益等参数。该芯片工作电压为3.0V-3.6V,一般情况下供电电压为3.3V。

图2 图像传感器电路图设计

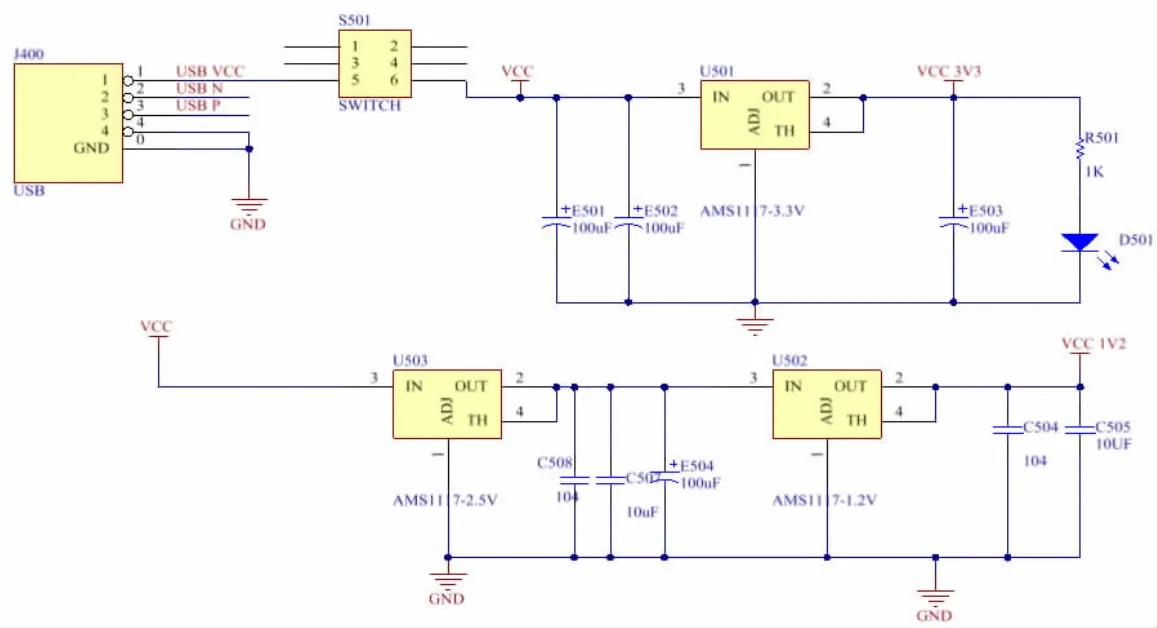

2.2电源模块设计

由于FPGA的电源需求通常很复杂,分别要为内核供电、I/O口供电以及辅助电压三路电源,根据设计要求分别为1.2V、2.5V、3.3V,另外SDRAM模块、USB模块、图像传感器模块供电电压都为3.3V,所以根据查阅资料,电源模块采用的是AS1117。AS1117是一款低压差的线性稳压器,当输入电流为1A时,输入输出的电压差典型值为1.2V,输出电压可调,可调电压范围为1.2V~13.8V,另外AS1117提供完善的过流保护和过热保护功能(正常工作环境温度为-50度-140度),确保芯片和电源系统的稳定性,输出电压与参考电压误差在1%范围内,完全满足本系统使用。

图3 系统电源模块设计

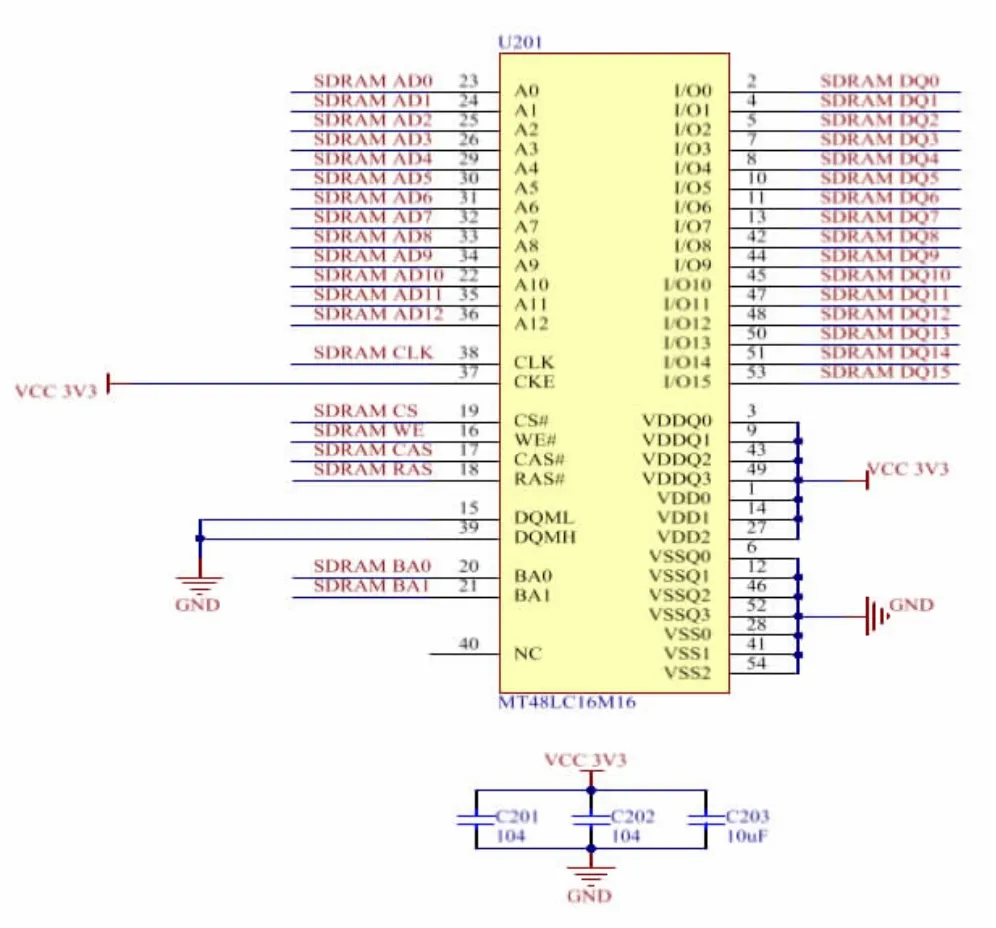

2.3SDRAM模块设计

本系统SDRAM采用容量为256Mb的MT48LC 16M16芯片,它是一种高速CMOS、动态随机存储器芯片,内部使用管线式架构,允许列地址被改变在每一个时钟周期内实现高速、完全随机存储。该芯片工作电压为3.3V,工作频率为100MHz,16位数据线,采用54脚的TSOP封装。

根据技术手册设计电路图如图4所示:

图4 SDRAM原理图设计

在电源与地的连接处加上高频去耦电容,滤除电源中的高频杂波以免产生自激,稳定电路工作状态。

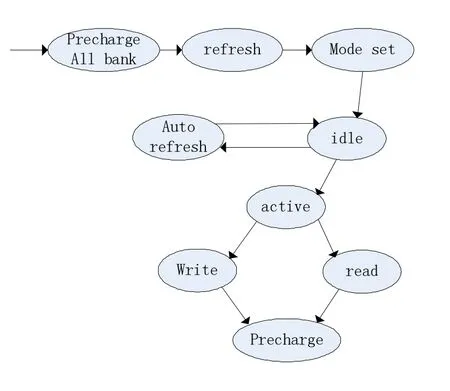

SDRAM是通过FPGA中的SDRAM控制器通过一个同步接口和若干个控制命令实现对其的控制,具体流程如下:

(1)正常情况下开始时必须要对SDRAM进行初始化,初始化其实就是系统的自检过程,这个过程持续的时间非常短,大约100至200微秒的时间,初始化过程完成之后,还必须要进行一次空操作命令,再进行一次预充电命令,最后在进行一次空操作指令来唤醒所有存储单元使其进入待机状态;前面都完成之后还要进行两次自刷新操作目的是使计数器进入工作状态,为MODE REGISTER初始化编程做好铺垫。

(2)其次是读写操作,读操作只有突发模式,写操作有突发跟全页写两种模式,读写操作在数据总线与地址总线在一系列控制命令下完成,其中突发模式带有预充电,突发长度有1/2/4/8四种,由MODE REGISTER控制,全页写模式不带预充电功能,可以任意控制一次能访问的列地址最大数。

(3)乒乓操作乒乓操作实际上是通过交错式控制实现各BANK之间的无空隙读写,其有三个优点:1.适用于流线性操作,能够实现数据无缝处理与缓存;2.有效节约缓存的空间;3.可以实现利用低速模块控制高速模块。

SDRAM工作状态图如图5所示:

图5 SDRAM状态转换图

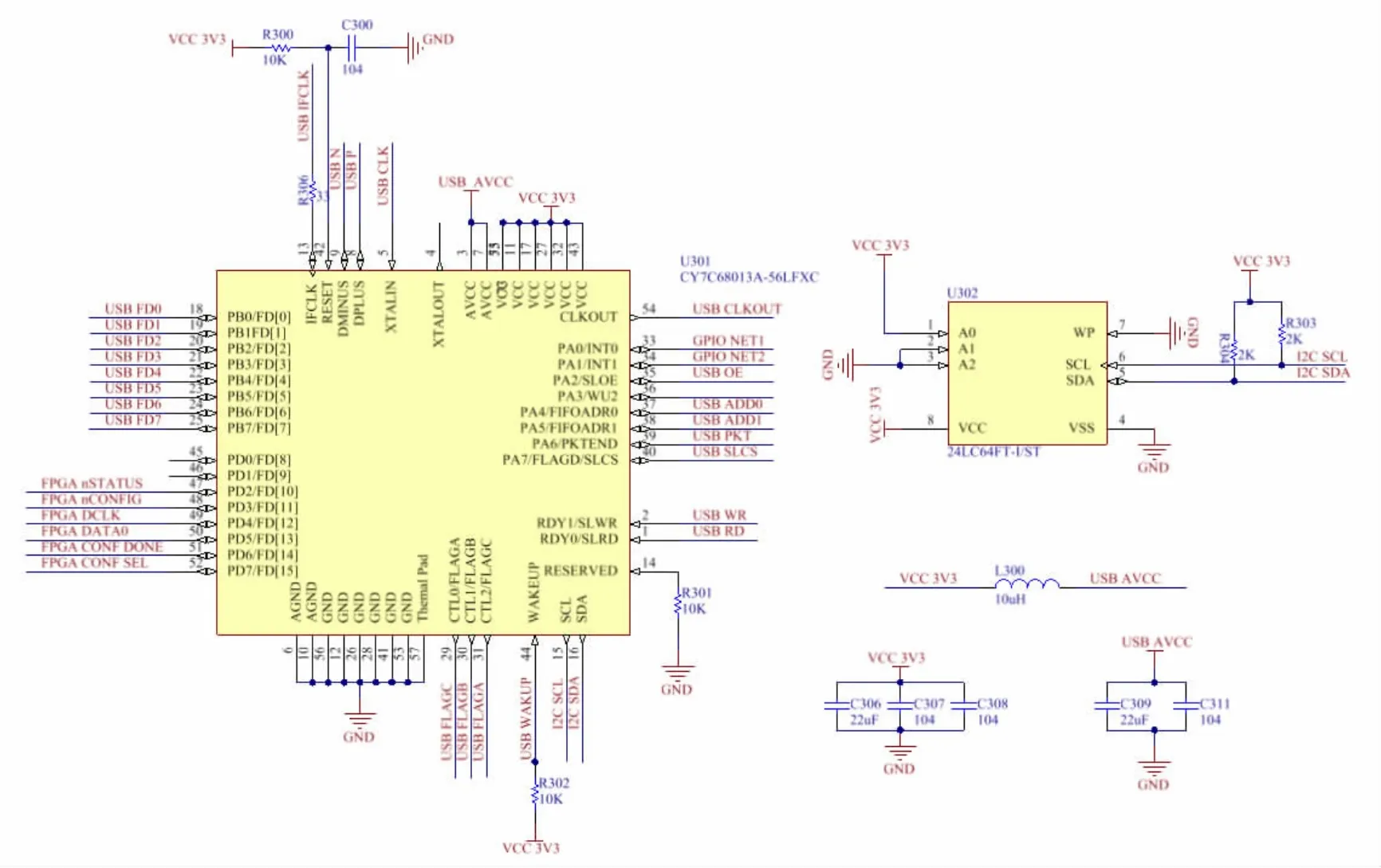

2.4USB模块设计

为了实现FPGA与上位机高速通讯,采用的是CYPRRESS公司的CY7C68013芯片,该芯片将USB2.0收发器、串行接口引擎(SIE)、增强型8051微控制器以及可编程外设接口集成到一个芯片中,具有16位地址总线,8位数据总线,24个I/O口,两个USART,三个计数器,两个数据指针,SCL和SDA引脚具有开漏输出和滞后输入的功能,必须外接2KΩ的上拉电阻上拉至3.3V,即使没有EEPROM也是如此,另外,它的供电电压一般为3.3V,最大不能超过5V,VCC与USB模拟电压之间要加一个电感,目的是抑制高频干扰对模拟电源的影响,同样,在VCC与地、USB模拟电源与地之间要加滤波电容,目的是滤除电源中的高频杂波以免产生自激,稳定电路工作状态。芯片封装采用56引脚QFN封装。USB通讯模块设计如图6所示。

图6 USB通讯模块设计

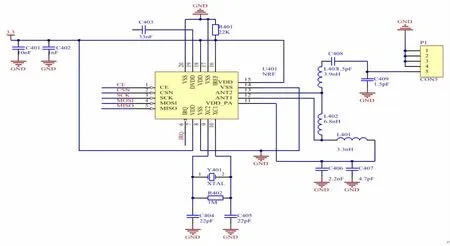

2.5无线模块设计

无线模块采用的是Nordic公司的nRF24l01射频收发芯片,这种无线模块传输方式技术比较成熟,在严苛的环境下通讯很稳定,传输速率也满足设计要求,所以选择nRF24l01射频收发芯片作为本系统的无线传输与模块,芯片内置频率合成器、功率放大器、晶体振荡器和调制器等功能模块。配置外置天线与功放芯片,传输距离会相应变长,但是传输距离变长就会相应的降低传输速率。

芯片电路如图7所示。

图7 无线传输模块设计

在此设计中CE端口为该芯片的片选端,CE端的作用主要用来选择芯片的工作方式,CSN为SPI的使能端,MOSI为SPI的数据输入端,MISO为SPI的数据输出端,SCK为SPI的时钟输入端,IRQ为中断请求端。FPGA一般是通过两个IO口与一个SPI口对nRF24L01芯片进行配置,当CSN为低电平时,在每个SCK的下降沿SPI上MOSI管脚的指令或数据串行移入到nRF24L01的MOSI管脚,在每个SCK的上升沿nRF24L01锁定指令或数据。写入指令时,一般是高位在前,低位在后,向nRF24L01写入指令的同时,其STATUS寄存器的值会从MISO脚移出。nRF24L01上SPI的最高速率可达8Mbps。

3 图像的采集及处理

图8为系统图像采集传输流程图:

图8 图像采集传输流程图

当系统进行图像采集的时候首先要对图像传感器进行初始化,FPGA与图像传感器之间是通过I2C总线相连的,所以对图像传感器得初始化操作也是通过I2C总线控制的,FPGA通过I2C总线对图像传感器一些参数进行设置完成初始化操作。图像采集主要是采集图像的有效像素,利用图像传感器的行有效像素以及列有效像素可以确保有效像素地准确输出;FPGA图像处理部分采用双线性插值算法,双线性插值算法占用硬件资源少,相对比较简单,对于数据实时处理非常方便;最后通过USB2.0传输接口或者通过无线模块把数据传到上位机。使用USB或无线传输方式是FPGA选择驱动不同的传输方式来实现的。

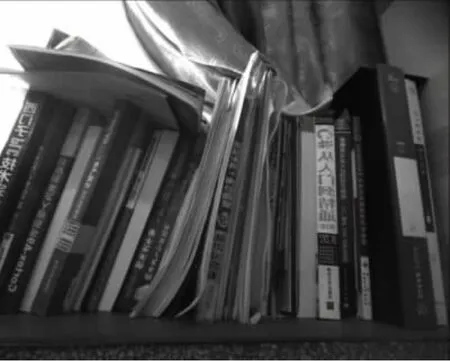

依据原理图制成PCB板进行采图测试,测试效果如下:

图9 测试效果图

4 结语

本系统实现了图像的采集与实时传输,采用CMOS图像传感器较之CCD图像传感器更能在严苛的环境中使用同时也加强了系统工作的稳定性,这使它在安保监控、医疗卫生、交通、工业生产领域作用越来越突出,使用大容量256MB的SDRAM可以更好地实现帧缓存,更好地实现FPGA的实时处理,采用USB2.0传输目的是在有线传输的情况下可以实现更快的传输速度,体现出高速传输的特点,采用无线模块目的是能在严苛的环境有线无法传输的情况下进行图像实时传输,经过测试无线传输完全满足实时传输的要求,采用FPGA使设计结构相对简单,在硬件上大大减少了设计的复杂度,减小了硬件调试难度,同时提高了系统的稳定性,总体来说,本系统设计简单实用,进一步进行工业化设计,有望得到市场应用。

[1]刘虹,黄涛.基于FPGA的高速图像采集系统的研究与实现[J].工业控制计算机,2004,08:18-19.

[2]刘强,潘明,李永伟.基于FPGA的汽车单目测距系统设计[J].液晶与显示,2014,03:422-428.

[3]祝长锋,肖铁军.基于FPGA的视频图像采集系统的设计[J].计算机工程与设计,2008,17:4404-4407.

[4]潘明,陈元枝,李强.基于FPGA的图像采集系统的设计[J].国外电子测量技术,2012,03:58-61.

[5]王荻.基于FPGA的图像处理系统设计[D].西安电子科技大学,2011.

[6]刘龙申,沈明霞,孙玉文,陆明洲,熊迎军.基于FPGA的农田图像采集与3G无线传输系统设计[J].农业机械学报,2011,4212:186-190.

[7]邱委华.无线图像传输系统的研究[D].沈阳航空工业学院,2010.

[8]李子鹤.基于FPGA的水源井无线视频监控系统设计[D].西安科技大学,2013.

FPGA;CMOS;USB;IMAGA;Acquistion;Wireless Transmission

Design and Implement of Image Acquisition Wireless Transmission System Based on FPGA

ZHANG Yu-jiang,LI Yue-qiang,QI Feng

1007-1423(2016)22-0053-06DOI:10.3969/j.issn.1007-1423.2016.22.012

张玉江(1991-),男,山东济南人,硕士研究生,学生,研究方向为光电检测技术

李月强(1968-),男,黑龙江人,硕士研究生,副教授,研究方向为光电检测技术

祁凤(1991-),女,山东济南人,硕士研究生,学生,研究方向为ARM嵌入式

2016-05-10

2016-07-26

设计一种基于FPGA的图像采集传输系统,能够实现图像的实时采集与传输。该系统图像传感器采用Micron公司的CMOS图像传感器MT9M001,核心控制器件为ALTERA公司Cyclone4系列的FPGA芯片EP4CE6E22C8,有线传输方式选择USB2.0接口作为数据传输的接口,实现了把每秒25帧、分辨率1280×1024的图像采集到PC内,同时基于严苛环境无法有线传输的情况下设计基于nFR24l01无线收发芯片的无线传输方式,传输速率能达到8Mbps,采用一片容量为256MB的SDRAM MT48LC64M4A2实现图像的帧缓存,FPGA作为核心器件可以同时控制图像采集,又可以在SDRAM中读取图像进行处理通过USB2.0接口或无线传输到PC实现整个图像采集过程。

FPGA;CMOS;USB;图像采集;无线传输

Designs a kind of image acquisition system based on FPGA and realizes the image acquisition and transmission.This system adopts the CMOS image sensor MT9M001 by Micron company as a system of image sensor,This system adopts the Cyclone4 series EP4CE6E22C8 FPGA chip by ALTERA company as the core of the whole system control devices,and choose USB interface as the data transmission interface,realized the 25 frames per second,1280×1024 resolution of image acquisition in the PC,at the same time,based on the rigorous environment under the condition of cable transmission,designs the wireless transmission mode based on wireless transceiver chip nFR24l01,transmission rate can reach 8 Mbps,with a capacity of 256 MB SDRAM MT48LC64M4A2,realizes the image frame buffer,as the core device FPGA can control the image acquisition meanwhile read and image processing in the SDRAM and via USB to a PC to realize the image acquisition process.