基于FPGA的CES时钟恢复算法实现研究

杨敏华,何 波

(中兴通讯股份有限公司,江苏 南京 210012)

基于FPGA的CES时钟恢复算法实现研究

杨敏华,何波

(中兴通讯股份有限公司,江苏南京210012)

文章介绍了一种适用于硬件数字电路实现的时钟恢复算法,主要描述该算法的原理,并列出关键模块的实现方案。目前该方案已经在Altera的FPGA器件EP4CGX150DF27I7上实现。

CES;现场可编程逻辑器件;时钟恢复;时钟合成

分组网电路仿真服务(Circuit Emulation Services,CES)是指在分组网络上承载传统时分复用(Time Division Multiplexing,TDM)数据的技术。分组网电路仿真技术在PWE3脉宽编码器(Pulse Width Encoder,PWE)框架下,采用电路仿真的方式,为数据流提供端到端的传输。当分组网络承载TDM业务的时候,需要保证业务始终的透明传递,涉及网络上宿端节点的业务时钟恢复问题。

目前的时钟恢复算法主要有两大类,一个是自适应法(Adaptive Methods),另一种是差分法(Differential Methods,DM)。其中自适应法是完全基于分组包到达间隔或缓存区的填充水平来恢复定时,可以保证业务始终的透传。优点是不需要公共参考时钟网,缺点是受到分组网络的影响大,处理相对复杂。差分法将业务时钟和本地参考时钟的偏差进行编码并在分组网络中传送,业务始终在宿端通过使用相同的参考时钟进行恢复,这种方法也可以保证业务始终透传。优点是由于收发两端的设备同步,受到分组网络的影响小,缺点是必须两端有公共参考时钟,成本较高。

本论文利用自适应法来恢复源端时钟,提供一种基于现场可编逻辑门阵列(Field Programmable Gate Array,FPGA)的可实现方案,保证宿端能恢复出源端TDM时钟。

1 设计思路

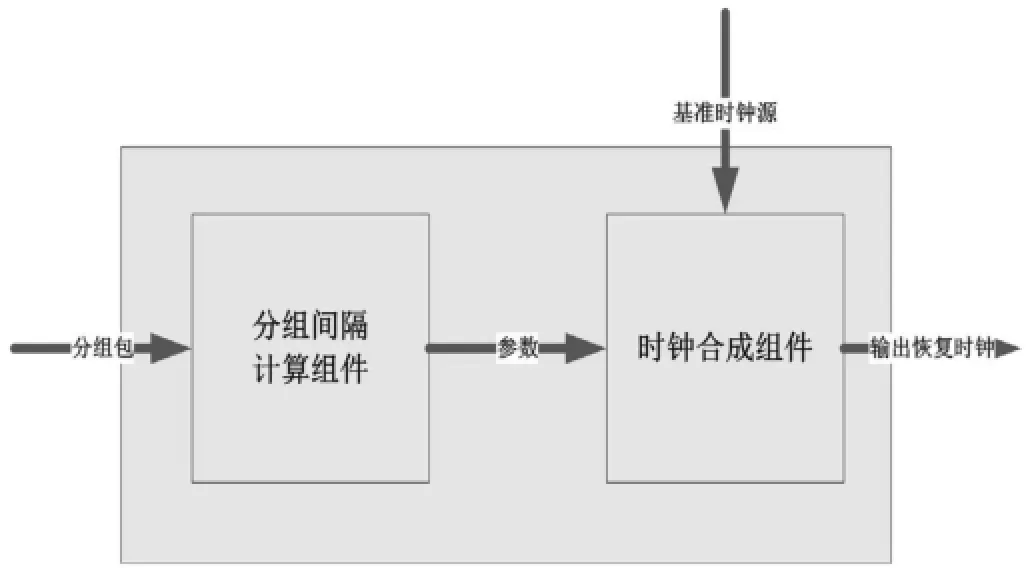

本系统基于分组包到达间隔,通过FPGA来实现基本功能。本系统分为时钟合成组件和分组间隔计算组件。通过分组间隔计算组件得到时钟合成组件需要的参数,最后通过时钟合成组件生成系统所需的恢复时钟。本系统架构如图1所示。

图1 系统架构

2 关键组件实现方案

2.1时钟合成组件

2.1.1算法原理

时钟合成技术是通信系统的重要组成部分,时钟合成技术通过对一个高精度和高稳定性的基准时钟进行运算,产生一个稳定的时钟。

在该组件中,利用删除脉冲模块有规律地删除基准时钟源(该时钟源相对于恢复时钟来说是一个高频时钟源)中的一些脉冲,从而实现平均意义上的小数分频,这种算法很容易用硬件实现,而且不容易产生竞争冒险和毛刺的问题。

2.1.2算法实现

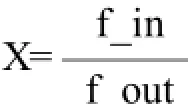

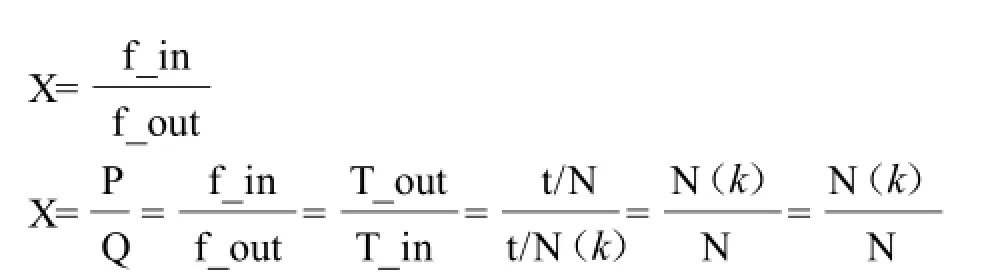

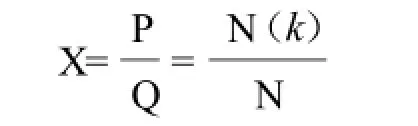

假设X为分频比,源时钟为f_in,输出时钟为f_out,则

将f_in和f_out同时扩大的倍数,总能将分子分母化为整数,将化为整数之后的分子和分母用P和Q表示,则

当时钟源每输入P个脉冲,利用脉冲删除模块从这P个脉冲中按照一定的规律删除(P-Q)个脉冲,输出Q个脉冲,从而实现的平均意义上的X分频。

时钟合成组件主要由删除信号生成模块和脉冲删除模块两部分组成,如图2所示。

图2 时钟合成组件架构

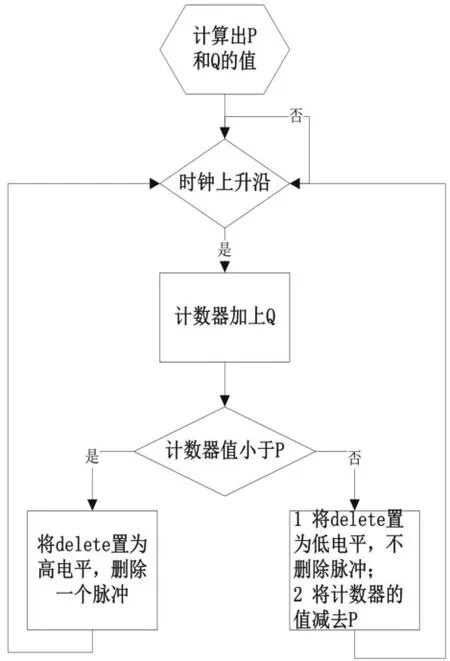

删除信号生成模块工作流程如图3所示,根据P和Q的值,对时钟源输入脉冲数进行计数控制。在时钟源的每个上升沿,计数器加上Q,若计数器的值小于P,则将删除脉冲控制信号delete置为1;若其值大于P,则将计数器的值减去P,并且将delete信号置为0,不发出删除脉冲的信号。

图3 删除信号生成模块工作流程

脉冲删除模块就是一个简单的或门,将delete信号和基准时钟源进行或运算,实现当脉冲删除控制信号delete为1时,从时钟源中删除一个脉冲。脉冲删除控制信号delete必须由时钟源的上升沿触发产生。

基于以上所述,当进行时钟合成时,只要求出分频参数P 和Q,就可以得到相应的分频时钟。

2.2分组间隔计算组件

为了求出最终的分频参数P和Q,先进行演算,假设X为分频比,源时钟(外部基准时钟源)频率为f_in,源时钟周期为T_in(T_in=1/f_in),输出时钟频率为f_out, 输出时钟周期为T_out(T_out=1/f_out)则

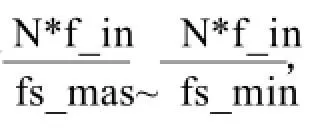

其中:t为两个分组的间隔时间,N(k)为用时钟频率为f_in的时钟采样的两个分组间隔时钟周期数,N为分组长度。

由于分组的传输抖动具有随机性,如果直接采用f_in的时钟采样间隔估算发送定时将导致很大的误差,所以对观测到的间隔值首先要经过预滤波处理,去除噪声间隔的高频分量。采用移动平均窗口算法完成预滤波处理,令表示通过滤波的分组间隔预测值,N_f为每个分组间隔的采样值,M表示平均移动窗口的长度,则

可见,如果M越大,则滤波效果越好,但是存储量和计算量越大。

结合时钟合成组件的算法原理,分组间隔估计组件可以计算出时钟合成所需要的P和Q,则

得到参数P和Q后,利用外部基准时钟源,当时钟源每输入N(k)个脉冲,利用删除脉冲模块从这N(k)个脉冲中删除(N(k)-N)个脉冲,输出N个脉冲,从而实现平均意义上的X分频,恢复了源端TDM时钟。

3 结语

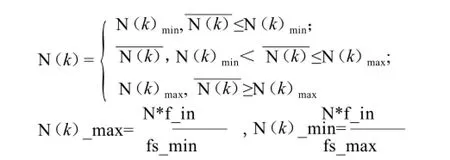

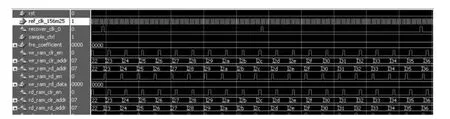

目前该算法用Verilog编码,已经在Altera的FPGA器件EP4CGX150DF27I7上实现。

该系统最终在Modelsim下的仿真波形如图4所示。

图4 仿真波形

[1]周梦然.CLPD/FPGA的开发与应用[M].徐州:中国矿业大学出版社,2007.

[2]王金明. VerilogHDL程序设计教程[M].北京:人民邮电出版社,2004.

[3]毛为勇.基于FPGA的任意小数分频器的设计[J].桂林航天工业高等专科学校学报,2009(1):30-32.

Implementation of CES clock recovery algorithm based on FPGA

Yang Minhua, He Bo

(ZTE Corporation, Nanjing 210012, China)

This paper introduces a clock recovery algorithm which is suitable for the realization ofhardware digital circuits. It mainly describes the principle of the algorithm and lists the implementation schemes of key modules in the program. At present, the scheme has been implemented on device EP4CGX150DF27I7 of Altera FPGA .

CES; FPGA; clock recovery; clock generation

杨敏华(1980— ),女,江苏常州,硕士,工程师;研究方向:数据通信。