地铁值班台硬件电路的设计

翟秀杰,吴 娜,李东格,赵 晋(河北科技大学信息科学与工程学院,石家庄 050000)

地铁值班台硬件电路的设计

翟秀杰,吴娜,李东格,赵晋

(河北科技大学信息科学与工程学院,石家庄 050000)

本文设计的地铁值班台(简称值班台)采用嵌入式Cortex-A8核心ARM处理器、核心板+底板的整体架构,底板集成所需要的功能模块,由音频电路模块和2B+D模块等构成,音频电路模块和2B+D模块是值班台设计的主要内容和创新点。

ARM;WM8731芯片;XHFC-2SU芯片

1 引言

随着计算机技术、微电子技术和网络技术的迅速发展,嵌入式系统日益广泛地应用在移动通信、消费电子、仪器仪表、工业控制等设备中。值班台是地铁调度系统的二级指挥调度设备,部署于每个地铁车站,对车站内的各项工作进行指挥,在地铁通信系统中有重要作用。

原来设计的值班台采用的是Inter处理器,由于此值班台占用空间大、内耗高等缺点逐渐不能满足需要,因此,本文设计的值班台采用嵌入式ARM A8处理器,这样使值班台工作稳定性更高,功耗较小,对环境(如温度、湿度、电磁场、振动等)的适应能力强,体积更小,且集成的功能较多。本论文介绍了值班台硬件电路的整体架构以及底板中音频电路模块和扩展模块硬件电路的设计。

2 值班台硬件电路整体架构

嵌入式系统的硬件核心是嵌入式处理器,嵌入式处理器的选择必须根据设计的需求,在性能、功耗、功能、尺寸和封装形式、SoC程度、成本、商业考虑等诸多因素之中进行折中择优选择。本文选择的是Cortex-A8核心ARM板TI公司AM335X系列中AM3359作为值班台的处理器,该处理器具有以下优点:它是最便宜的Cortex A8处理芯片,降低了整个开发板研发成本;TI史上公开资料最全的一个芯片;产品定位最清晰的一个,惟一一个集成2个MAC的MCU;AM3359开发板支持Linux,Android,WinCE三种操作系统,已在工业控制、智能交通、电力系统、车载设备、通信设备、网络终端等环境恶劣场合广泛应用。选择该处理器的主要原因是因为之前项目中采用的是AM335X系列内核开发板,此开发板完全可以满足本设计的要求,而且公司不用开发新的开发板,既节省了研发时间又大大减少了课题经费。

值班台核心板模块框图如图1所示,核心板是值班台的最小系统,主频率为720MHz,它集成了AM3359处理器芯片、电源芯片、DDRRAM芯片、eMMCFLASH芯片、RTC电路、时钟电路、复位电路等芯片以及功能电路,还含有很多的外设接口,它用来与底板的功能模块进行通信的。

图1 值班台核心板模块框图

值班台硬件电路开发板是由核心板和底板组成,底板则提供值班台所需要的功能模块,如音频电路模块、扩展模块等。

图2 开发板模块框图

3 音频电路模块设计

音频编码解码器的作用是将语音进行模数或者是数模转化。麦克风采集语音后,语音进去到音频编码解码器,经过模数转化,变成数字信号,然后数字信号经音频编解码器接口传输到处理器进行编码,并对语音进行存储来实现录音功能。处理器对语音解码后,数字信号传输给音频编解码器,音频编解码器中的D/A模块将数字信号转化为模拟信号,然后通过耳机或者音响播放出来。

用户要求值班台能实现左右通道独立通话的功能,所以它在音频模块设计中是重点设计内容。

3.1音频编解码器

数字音频处理芯片选用的是wolfson公司的WM8731芯片,该芯片是一款带有集成耳机驱动器的功耗低且语音质量高的24位音频编码解码器。图3是WM8731芯片电路图。

图3 WM8731芯片电路图

本设计中WM8731的引脚LLINEIN和RLINEIN作为语音左声道与右声道信号的输入,LHPOUT和RHPOUT引脚作为信号输出,该芯片有可配置的数字音频接口和2或3线可选的微处理器控制接口。

WM8731芯片中MODE(控制接口选择线)、CSB(片选或地址选择线)、SDIN(数据输入线)和SCLK(时钟输入线)4个引脚作为控制接口,控制器通过控制接口对WM8731进行配置,接口分为2线或3线模式,2线模式是MPU接口,3线模式是兼容SPI接口,本设计选择使用2线模式,MODE引脚置地。

BCLK(数字音频位时钟)、DACDAT(DAC数字音频数据输入)、DACTRC(DAC采样左/右声道信号)、ADCDAT(ADC数字音频信号输出)、ADCLRC(ADC采样左/右声道信号)5个引脚为芯片的数字音频接口,其作用是读写数据音频信号。

核心板通过IIC总线接口对WM8731寄存器进行配置,芯片初始化完成之后,手柄或免提采集到的语音数据通过LHPOUT引脚和RHPOUT引脚输入到WM8731芯片,经过模数转化后,成为串行的数字信号,经由MCASP接口传入到核心板处理器,语音输出时经过WM8731数模转化,由LHPOUT和RHPOUT引脚通过音响或耳机输出语音。

3.2实现左右通道同时通话

本设计中采取免提在左话路手柄在左右话路之间任意切换的方法,来实现两条话路能同时通话且两者之间互相无影响的功能。

手柄在左右话路切换的思想是:由开关控制手柄的切换,当开关置高时,手柄接左话路,置低时手柄接右话路,手柄采集到语音后,经过一级放大器和二级放大器对语音进行放大,然后语音通过左话路或者右话路进入到WM8731芯片中进行模数转换,最后上报到核心板中的CPU,另外核心板的一个GPIO口用来检测手柄的摘挂机。

用户有时喜欢用手柄接听,有时喜欢用免提接听,所以设计了左手柄和左免提之间切换方案:左手柄和左免提的切换方案是通过核心板的GPIO引脚HF-L的高低电平切换的,当引脚为低电平时,左话路切换至左手柄,用手柄接听语音;当引脚HF-L为高电平时,左话路接免提,语音是通过驻极麦克或者电容麦克输入,通过扬声器或者音响输出。

4 2B+D接口模块

2B+D接口模块用于连接程控交换机DUI板或者BRI板。XHFC-2SU是一款ISDN(综合业务数字网)的收发芯片,有2个ISDN接口S/T或Up,这两个接口是与数字程控交换机BRI板或DIU板中的S/T或Up

接口相连接的,实现值班台与数字程控交换机连接的作用。ISDN接口选择可以通过配置芯片引脚来进行选择的,1个PCM128/PCM64/PCM30接口,该接口是数字音频接口,1个集成微处理器总线接口,它可以配置为8位并行处理器接口或者配置为串行处理器接口(SPI)。XHFC-2SU芯片中的FIFO当作内部存储器,FIFO的含义是先入先出阵列,即先进去的数据先出去,后进来的数据后出去,所以只能顺序写入数据和顺序读出数据,FIFO存储器使XHFC-2SU芯片数据采集、数据处理和数据传输都具有高效性。

4.1集成微处理器接口

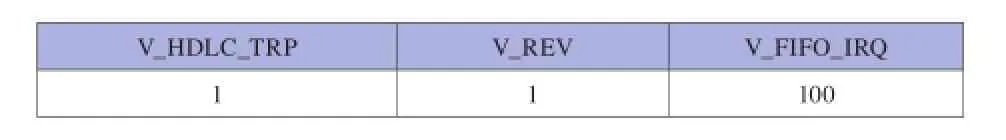

表1 处理器访问方式

处理器访问方式如表1所示。集成微处理器总线接口用于处理器对XHFC-2SU芯片进行操作,即与XHFC-2SU芯片进行数据交换。处理器接口有并行处理器接口和SPI串行接口,通过芯片引脚进行配置,本设计使用的是SPI串行接口作为处理器接口,SPI接口是一个同步串行外设接口,通过SPI接口可以使处理器与外围设备两者之间传输信息。

4.2FIFO和HDLC控制器

HDLC是一种高级数据链路控制器,它位于S/ T或Up接口的FIFO接口侧,纯数据存储在FIFO中,当HDLC控制器进入到自动零插入模式时,数据从HDLC控制器传输到ISDN接口或者是到PCM接口,当HDLC控制器进入到自动删零模式时,数据从ISDN接口或者PCM接口传输到HDLC控制器。

B通道FIFO寄存器可以配置成透明传输方式,bit顺序配置为MSB,中断配置为FIFO半满(64字节,8ms),B通道FIFO配置如表2所示。

表2 B通道FIFO配置

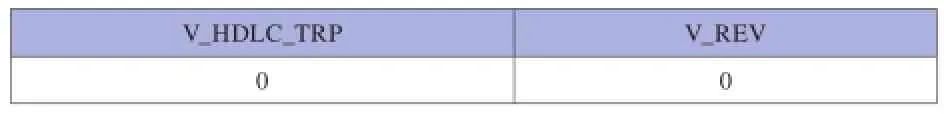

FIFO也可配置为HDLC方式,用于传输D通道数据,bit顺序配置为MSB,中断配置为混合方式(FIFO半满及帧结束都报中断),D通道FIFO配置如表3所示。

表3 D通道FIFO配置

子通道处理功能用来实现降速率的数据传输,D通道收发时必须用到此功能,子通道处理配置如表4所示。

表4 子通道处理配置

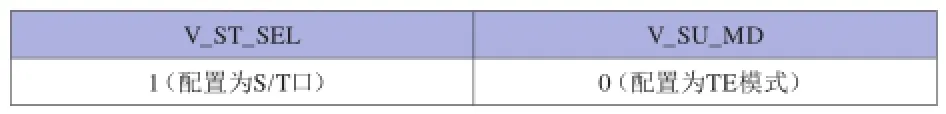

4.3通用ISDN端口

XHFC-2SU芯片具有两个通用的ISDN接口,可选择配置为S/T口或者Up口,在本课题中配置为Up口,工作模式需要配置为TE模式,物理接口使用RJ45接口。通过V_SU_ACT发起激活去激活请求,通过A_SU_RD_STA读取当前接口状态,通过A_ SU_SET_STA设置当前端口状态.ISDN接口的配置如表5所示。

表5 ISDN接口配置

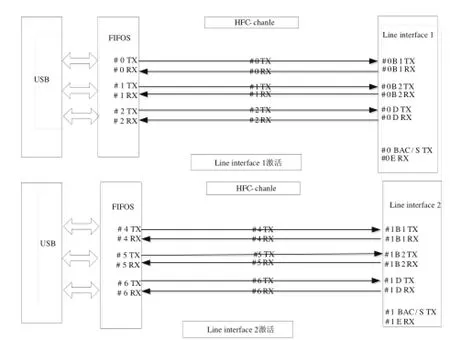

4.4XHFC-2SU数据流

数据流总的来说就是可编程的ISDN接口、PCM接口和FIFO之间的互联,2B+D手柄通话数据流配置如图3所示。

图3 2B+D手柄通话数据流配置

5 结束语

本文设计的值班台手柄可以左右切换,实现两条话路同时通话的功能,而且两条话路之间无影响,增强了值班台的调度功能。值班台程控交换机接口原来是B+D接口,现在改为2B+D接口,这样提高了值班台与程控交换机连接的可靠性。

[1] 周立功.ARM嵌入式系统基础教程[M].北京:北京航天航空大学出版社,2005,(1)

[2] 王永虹.STM32系列ARM Cortex-A3微控制器与实践[M].北京:北京航天航空大学出版社,2008

[3] 王永虹,徐炜,郝立平.STM32系列ARM Cortex-M3微控制器原理与实践[M].北京:北京航空航天大学出版社,2008

[4] 王田苗.嵌入式系统设计与实例开发[M].清华大学出版社,2003

[5] 王宏志.基于Cortex-A8的智能电话的硬件设计与实现[J].哈尔滨工业大学,2013

[6] 刘景华,王辛杰.基于WinCE5.0下WM8731音频驱动器设计,2011, 8(1): 77-80

The Design of Subway Station Console Extension Module

Zhai Xiujie, Wu Na, Li Dongge, Zhao Jin

(Institute of information science and engineering, Hebei University of Science and Technology, Shijiazhuang, 050000)

This design subway duty station (hereinafter referred to as the duty station) adopt embedded ARM Cortex-A8 core processor, overall architecture consisted of core board and base plate, function modules required by Backplane integration is made up of audio circuit module, 2B+D module and so on, audio circuit module and 2B+D module are the main content and innovation in the design of duty station.

ARM; WM8731 chip; XHFC-2SUchip

10.3969/J.ISSN.1672-7274.2016.02.005

TN915.852,TN92文献标示码:A

1672-7274(2016)02-0019-04