基于FPGA的多功能数字频率计的设计与实现

东北大学计算机科学与工程学院 张楠楠 陈 龙 郭恒哲 李大宇

基于FPGA的多功能数字频率计的设计与实现

东北大学计算机科学与工程学院张楠楠陈龙郭恒哲李大宇

针对于普通频率计不能测量小信号的不足,本文介绍了一种基于FPGA与单片机的多功能数字频率计的设计与实现。该频率计采用多周期同步测频法,以FPGA与单片机为核心处理器,通过前端信号调理,实现了对频率为1Hz~100MHz、电压为4mV~1V的周期信号进行周期、频率、占空比、时间间隔等功能的测量。

频率计;FPGA;多周期同步测频;占空比;Tiva C Launchpad

0 引言

数字频率计是计算机、通信设备、电子测量等科研生产领域不可缺少的测量仪器。传统的频率计多采用集成芯片,可测试的最大频率不高,灵敏度不高,而且其单一测频的特点也已无法满足现在的发展要求。本文提出了一种基于FPGA和单片机的频率计设计,可实现低至4mv小信号的1Hz~100MHz频率测量,具有高速、精确、可靠、抗干扰性强、可根据需要进一步提高其测量精度而不需要更改硬件连接的特点。

1 频率计总体设计思想

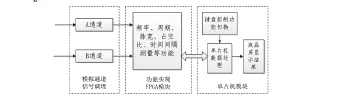

图1 系统框图

整个系统采用模块化的思想,分割为三个模块,(1)前级信号调理模块:对外部输入信号进行波形整形,将输入周期信号整形成逻辑电平;(2)功能实现FPGA模块:对各个功能进行相应的逻辑控制和数据测量,并将测得的数据发送至单片机;(3)单片机模块:能根据不同的外部输入键值发给FPGA相应的控制指令,对从FPGA接收到的数据进行处理,将结果在液晶屏上准确显示。三个模块分别实现后联调,实现了频率、占空比、脉宽、时间间隔等多功能的测量。系统框图如图1所示。

2 理论概述

2.1频率/周期测量原理

频率测量采用多周期同步测频法。其计数的闸门时间不是固定的值,而是被测信号周期的整数倍,即利用D触发器将闸门信号与被测信号同步,因此,避免了对被测信号计数所产生±1个字误差,并且达到了在整个测试频段的等精度测量。示意图如图2所示:

图2 多周期同步测频法波形图

由图2可以看出,实际闸门时间t与预置闸门时间t1并不严格相等,但差值不超过被测信号的一个周期。为了得到实际的闸门时间t,可引入另一个计数器和标准时钟,在测量被测信号频率的同时,对标准时钟进行计数,通过计算即可得到实际闸门时间。若在实际时间t内测得标准时钟计数Nc,待测时钟计数Nx,则:

可计算得到待测信号的频率。

上式中Nc值仍存在±1字误差的影响,但由于标准时钟频率很高,±1字误差的影响很小。取时钟频率fc=200MHz,则由±1字引起的相对误差为5×10-9。该误差是对标准时钟计数时产生的,与被测信号的频率无关,故在全频段的测量精度是均衡的。

2.2占空比/脉宽测量原理

占空比/脉宽的测量方法是,在方波信号高电平时对标准频率fc计数得N1,在其低电平时对标准频率计数得N2,则占空比

2.3时间间隔测量原理

将两路同频周期信号进行逻辑异或操作,也即是将其中一路取反后与另一信号进行逻辑或操作,可实现将时间间隔测量转化为方波信号的高电平持续时间测量,用此高电平信号作为使能信号对标准时钟fc进行计数N,则高电平持续时间为,即这两路同频信号的时间间隔。

图3 时间间隔测量原理

3 调理整形模块设计

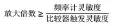

前端信号调理模块主要分为前置放大、偏置电位调节、触发整形等几个功能模块,实现将输入信号调理整形至FPGA输入逻辑电平的功能。

图4 单通道模拟部分功能框图

3.1宽带放大器

前置宽带放大电路设计的难点主要在于高灵敏度和高带宽,合理的运算放大器选型就显得尤为重要。

根据计算公式,在保证系统带宽要求的前提下:

由前后级的相关参数推算,最终选择TI公司的宽带运算放大器opa695,其增益带宽积为1400MHz,较高的压摆率能够适应较快的信号变化,能够满足设计需求。

3.2整形电路

考虑到多种信号的频率测量功能,在前置放大后要级联信号整形模块,将其他类型的周期波形整形成方波。整形电路采用高速施密特触发器,以处理频率高达100MHz的信号,同时利用施密特触发器的滞回特性来增强系统的抗噪能力。最终选择TI公司的SN74LVC1G14芯片,其传输延迟时间<4.6ns,边沿的上升/下降<2.5ns,能够实现设计需求。

信号整形处理模块单元电路示意图如图5所示:

图5 调理整形模块电路示意图

4 FPGA模块功能实现

FPGA根据单片机送来的不同指令分别执行相应的测量操作,并把测得数据在同步时钟的作用下送给单片机进行数据处理及显示。

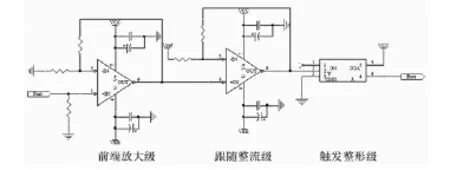

4.1 频率/周期测量功能的实现

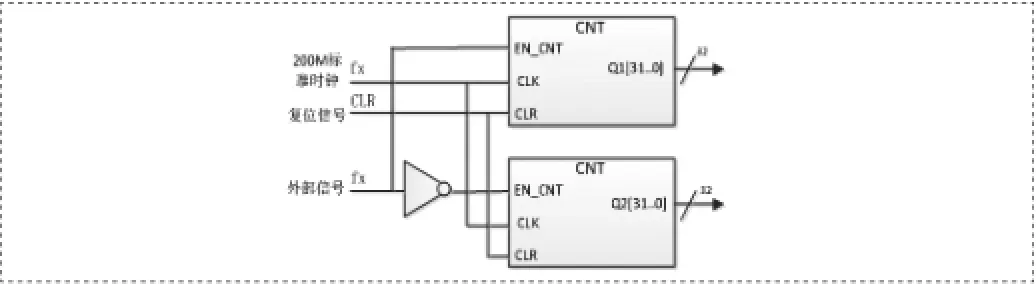

根据前述多周期同步测频法的原理,实现频率测量的结构框图如图6所示:

图6 频率测量框图

图6中的D触发器利用待测信号来同步预置闸门得到实际闸门时间;CNT0模块是对标准时钟进行计数的计数器;CNT1模块是待测时钟信号的计数器;LOCK模块对计数结果进行锁存,以避免在计数完成之前向后传送数据;MUX模块在数据选择信号SEL的作用下将64位数据分8次并行传送给其后的单片机模块,每次传送8位,以“少量多次传输”的方式减少并行传输数据的路数。

4.2占空比/脉宽测量功能的实现

根据前述占空比与脉宽的测量原理,可实现其结构框图如图7所示:

图7 占空比测量框图

外部信号经模拟信道整形后一路直接使能一个计数器,另一路经反相器取反后使能另一个计数器,两个计数器在相应使能信号的作用下分别对标准时钟计数,得到所需的N1,N2,从而得到占空比和脉宽。

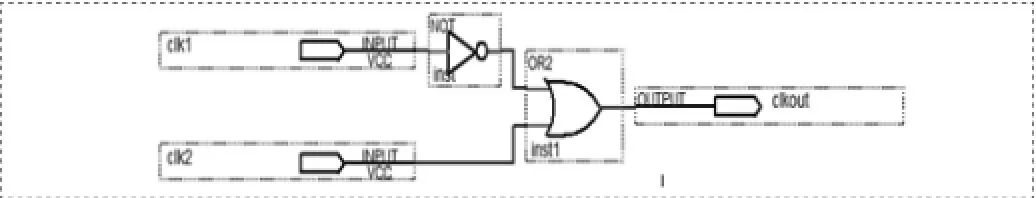

4.3时间间隔测量功能的实现

在FPGA中将接收到的两路同频信号如图8进行处理,然后将结果作为使能信号对标准时钟fc进行计数N,得到时间间隔。

图8 时间间隔测量逻辑处理框图

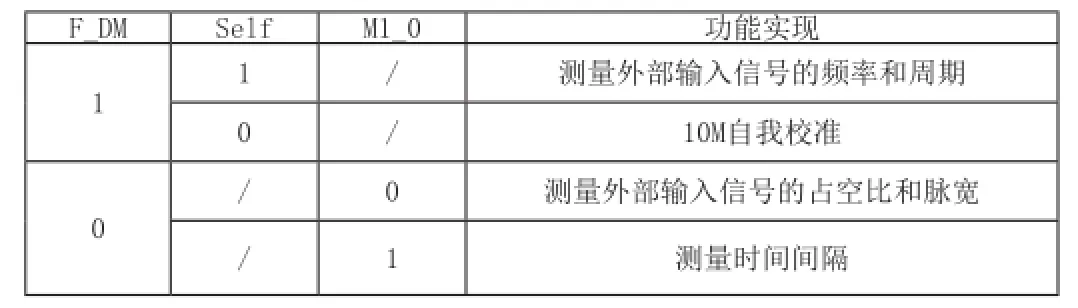

4.4FPGA顶层原理图

FPGA模块共有三根功能控制线与单片机之间通信,它们的逻辑组合与实现的功能如表1所示:

表1 逻辑控制表格

顶层FPGA结构图如图9。其中,锁相环pll0模块用来产生所需的200M标准时钟信号和10M自校准信号等;Delay模块是时间间隔测量时的逻辑处理模块;前一个DQ模块是用来同步的D触发器,后两个DQ模块用来产生计数器的清零信号;COUNTER与LOCK分别为计数器与锁存模块。adjust与CONTROL模块是FPGA对输入的逻辑控制。OUTMCU模块实现FPGA计数结果向单片机传输时由64位宽转换成8位宽的数据选择功能。

图9 FPGA顶层原理图

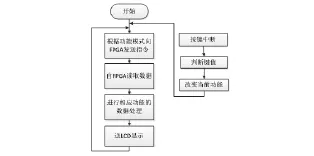

5 单片机计算与显示模块

单片机根据外设键盘的输入给FPGA传送不同的控制命令,然后通过数据选择线sel分别读取FPGA测得的数据N1或N2,通过计算将结果送到液晶屏显示。其中键盘实现功能的切换选择;液晶屏显示频率、周期、占空比、脉宽、时间间隔等测量结果。

程序流程图如图10所示:

图10 单片机程序流程图

6 测试成果展示

本系统选用的FPGA芯片为Altera公司CylconeII系列中的EP2C20Q240C8N,板上50M系统晶振经锁相环倍频到200M作为标准时钟,单片机小系统选用TI公司的Tiva C LaunchPad,联合键盘和液晶屏等外设调试测试后证实性能稳定。频率/周期测量范围为1Hz-100MHz,误差在10-5之内,测试波形可为方波、正弦波、三角波等,幅值最低可到4mv;占空比测量范围为10%-90%,频率范围为1Hz~5MHz,测量误差的绝对值小于10-2;对同频方波时间间隔测量的频率范围为100Hz~1MHz。

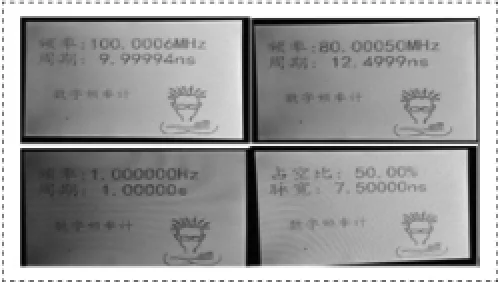

实际测量结果如图11,实物图展示如图12所示:

图11 实际测量结果图

7 结语

本文所设计的多功能频率计作为2015年全国大学生电子设计大赛的参赛作品,获得了国家二等奖以及辽宁省赛区一等奖的成绩。系统采用模块化的思想,将模拟、FPGA、单片机三部分单独设计完成,最后联合调试,在电子设计竞赛期间可使队友之间合理分配利用时间。由于系统采用FPGA和单片机为核心进行设计,保证了系统的灵活性,可以对系统功能进一步进行优化和扩展,比如进一步提高标准时钟频率、在计数显示不溢出的条件下扩大闸门时间以及将固定闸门改为自适应闸门等。

[1]曾永西.基于Quartus II的两种数字频率计的设计与比较[J].福建电脑,2008(6):168-169.

[2]许发翔,颜锦,陈孟臻,刘春群.基于FPGA的数字频率计的设计[J].电子科技,2014(23):10-11.

[3]曾光,冯锐.基于FPGA的数字频率计VHDL软件实现方法[J].软件导刊,2009,8(2):28-29.

[4]梁颖,佟川.基于FPGA的等精度频率计单片系统设计[J].软件,2012,33(1):74-76.

[5]包本刚,何怡刚,谭永宏.基于FPGA的全同步数字频率计的设计与实现[J].测试技术学报,2008,22(2):99-102.

[6]王永良,宋政湘.基于FPGA的同步测周期高精度数字频率计的设计[J].IC设计,2004(12):74-76

[7]林建英,高苗苗,杨素英.基于SOPC的等精度数字频率计设计[J].研究与开发,2012,29(12):51-55.

[8]谢海鸿,李萍,林德彬.基于FPGA芯片的数字频率计设计[J].现代电子技术,2005(18):13-16.

[9]毛智德,吕善伟.基于FPGA的等精度频率计设计[J].电子测量技术,2006,29(4):85-86.

李大宇(1981—),辽宁辽阳人,讲师,研究方向:实时信号处理。