用于电荷域流水线ADC的子级电路版图布局方式

张甘英,陈珍海,魏敬和,于宗光

(中国电子科技集团第五十八研究所,江苏无锡 214035)

工程与应用

用于电荷域流水线ADC的子级电路版图布局方式

张甘英,陈珍海,魏敬和,于宗光

(中国电子科技集团第五十八研究所,江苏无锡214035)

对电荷域流水线ADC子级电路结构和原理进行了分析,并设计了一种基于普通CMOS工艺、适用于高速高精度电荷域流水线ADC的子级电路版图布局方式。基于0.18 μm 1P6M 1.8 V CMOS工艺,采用所设计的子级电路版图布局方式和高精度金属-金属电容匹配技术,完成了典型电荷域子级电路的版图设计,并成功运用于一种14位250MSPS电荷域流水线ADC中。测试结果表明该ADC电路在240MSPS采样条件下对于20.1 MHz的输入信号得到的SNR为70.5 dBFS,功耗为230 mW,面积为2.6×4 mm2,版图设计较好地实现了ADC电路性能。

流水线模数转换器;电荷域;版图设计;子级电路;电容匹配

TM133

A

1673-5692(2016)02-187-05

0 引 言

随着CMOS工艺和设计技术的不断进步,已报道的流水线ADC性能不断提高。通过采用各类新颖的设计技术,基于传统开关电容技术的流水线ADC已经可以达到16位160MSPS以上[1,2],但是其性能严重依赖于所使用的高增益带宽积的运算跨导放大器(OTA),从而导致极大ADC的功耗。为了显著降低高速、高精度ADC的功耗,近年来已经有许多针对性的解决方法被提出并验证。其中最典型的技术是数字校准辅助的开关电容技术[3-7],其思路是降低流水线子级中的运放设计要求从而降低功耗,再采用数字校准电路来纠正低性能运放所引起的误差。然而,数字校准算法增加了电路设计复杂度,并且大规模数字逻辑占用了较大的芯片面积并增大了ADC的动态功耗。

基于BBD(Bucket brigade devices)的电荷域流水线ADC是一种不使用高性能运放的流水线ADC实现技术[8-10]。这种流水线ADC的子级采用基于BBD的增强型电荷传输器件(BCT)来实现电荷域A/D转换,在两相时钟的控制下,各子级依次完成实现电荷接收、电荷比较、余量电荷计算和电荷传输,在整个流水线A/D转换通路中没有高性能的OTA,从而可以极大地降低功耗。由于流水线ADC的性能取决于其所使用的各级流水线子级电路的速度和精度,因此高性能电荷域流水线子级电路结构和版图布局方式成为电荷域流水线ADC电路和版图设计的关键。由于这种ADC的出现时间较短,并且电荷域流水线ADC的原理和关键电路设计和传统的开关电容流水线ADC的实现方式完全不同,现有的版图布局方式不能直接适用,需要设计全新的布局方式以保证ADC电路的性能。

本文首先对电荷域流水线ADC的子级电路结构和基本原理进行了分析,在此基础上设计了一种适用于普通CMOS工艺的电荷域流水线ADC子级电路的版图布局方式,并以典型1.5位子级电路为例对其关键元器件的版图布局方法进行了详细说明。基于所设计的版图布局方式,论文采用1P6M 0.18 μm CMOS工艺完成了一款低功耗14位250MSPS电荷域流水线ADC的设计和流片,测试结果显示了非常好的综合性能。

1 电荷域流水线ADC子级电路结构及原理分析

电荷域流水线ADC子级电路结构和工作原理波形如图1所示,为简化说明图中所示为单端形式。图1(a)所示的ADC子级电路包括一个电荷存储节点Xn,两个连接到Xn的电荷存储电容Cc和Cs,一个用于对输入电荷Qi进行比较量化产生本级量化结果D(n)的Sub-ADC电路,一个用于根据D(n)产生用于对Qi进行电荷加减以产生余量电荷Qout所需模拟电压Vdac的Sub-DAC电路,一个用于将本级所产生余量电荷Qout传输给下一级子级电路的电荷传输电路St和一个在Qout传输完成之后对Xn进行复位的复位开关Sr。

图1 电荷域ADC子级电路结构和工作原理波形

图1(b)所示为该电路工作的电压波形示意图。t0时刻,前级电路的电荷传输电路打开,Qi被传输到本级电荷存储节点Xn,由于电荷以电子的形式传输,随着电荷注入,Xn的电压将会由t0时刻的VXn(0)不断降低;t1时刻,前级电荷传输电路关断,前级电路向本级电路的电荷传输工作结束,由于此时Xn不存在电荷泄露通道(忽略亚阈值漏电),t1时刻的电压VXn(1)将保持不变,此时本级电荷量化电路Sub-ADC电路开始电荷比较量化工作,得到本级量化结果D(n);t2时刻,Sub-ADC电荷比较量化工作结束,所得到的D(n)将会一方面输出给流水线ADC的数字延时同步电路,同时还会交给Sub-DAC电路以产生余量电荷Qout所需模拟电压Vdac,所产生的Vdac会通过电荷加减电容Cs对Qi进行电荷加减得到本级电路的余量电荷Qout,若输入电荷Qi较大,则D(n)较大,Vdac的改变量⊿Vdac越大;t3时刻,本级电路的电荷传输电路St打开,Qout将会传输到下一级子级电路;t4时刻,本级电路电荷传输电路St关断,本级电路向下级电路的电荷传输工作结束;t4~t5时刻,t4时刻的电压VXn(4)将保持不变;t5时刻,本级复位开关Sr打开,复位电压Vs对Xn进行复位,Xn电压逐渐上升;t6时刻,本级电路复位工作结束,此时Xn电压VXn(6)应该等于t0时刻电压,子级电路一个完整的时钟周期工作完毕。

从上述电荷域流水线子级电路的工作机理可以看出,对于电荷域流水线ADC,电荷的传输、加/减、比较量化等功能均围绕各子级的电荷存储节点进行。电荷在不同电荷存储节点之间的传输速度和传输效率直接决定ADC的速度和精度。因此高精度和可靠性电荷存储节点的设计是电荷域流水线ADC子级电路版图设计的核心工作。

2 电荷域流水线子级电路的版图实现

2.1电荷域ADC子级电路版图布局方式

图2所示为本文设计的典型全差分结构电荷域流水线ADC子级电路版图包括基准信号产生电路版图区、比较器阵列版图区、基准信号选择电路版图区、电荷传输电路版图区和电荷存储电容版图区。整个电荷域流水线子级电路的版图布局以比较器阵列中心轴为对称轴,左右两侧完全对称;此外图中版图空白部分由去耦电容填充,以进一步减小各类噪声对电路核心版图模块部分的干扰。图中电荷传输电路版图区与电荷存储电容版图区共同构成了本级电荷域ADC子级电路的电荷存储节点,因此对该两大版图区域的版图设计应特别小心。本文在该两大版图区域的版图区域外围设置了由P型衬底隔离带版图区与N阱隔离带版图区所组成的双环保护隔离带,以使数字电路引起的衬底噪声对该部分版图区域的干扰最小化。

图2 电荷域流水线子级电路版图布局

2.2电荷存储电容的匹配设计

在普通CMOS工艺中,可以实现的片上电容包括:结电容、栅电容、金属-多晶、金属-金属电容等等,其中前两种容易实现高电容密度,后两种容易实现高匹配精度和线性度。要实现高性能电荷域流水线ADC,子级电路内部的电荷存储电容对于电容的匹配精度和线性度均要求均非常严格,因此论文采用高匹配精度的金属-金属电容来实现电荷存储电容。对于金属-金属电容的实现,可以采用不同金属层之间的平板电容结构也可以采用同层金属线之间的叉指结构,前者相对容易实现绝对精度,但是大电容实现需要比较大的面积开销;后者相对更容易实现容值更大的电容,同时也容易实现高精度匹配。综合考虑,论文选择用叉指结构的金属-金属电容来实现电荷存储电容,具体结构如图3(a)所示。

图3 电荷存储电容结构及版图实现

图3(a)中电荷存储电容的结构是采用3层金属并联的叉指结构,目的是增大单位面积电容的容值。论文中ADC设计采用的是1P6M0.18μmCMOS工艺,电容实现采用的是第三、四、五层铝线。图3(b)所示为电荷存储电容的具体版图实现,中间部分正、负端交叉布局的为有效电荷存储电容,左右两侧为起匹配保护作用的dummy电容,所有电容的外围设置了保护隔离环带来隔离外界噪声的耦合。

2.3电荷域1.5b/级子级电路版图实现

图4所示为采用上述子级电路布局方式,基于1P6M0.18μmCMOS工艺设计得到的典型电荷域1.5b/级流水线子级电路版图具体实现。该子级电路为14位250MSPSADC的第三级子级电路,版图面积为0.1×0.22mm2。

图4 1.5b/级流水线子级电路版图实现

3 试验结果

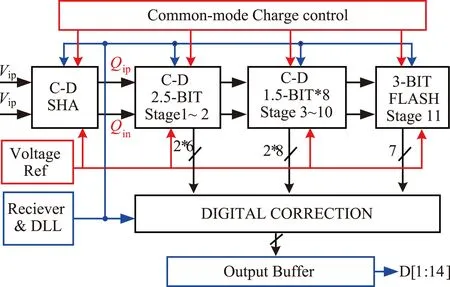

本文所设计的电荷域流水线ADC子级电路版图布局方式已成功应用于一款14位250MSPS电荷域流水线ADC电路中,并流片验证。图5所示为该14位ADC的系统结构图。输入模拟信号处理通道包括一个高速采样保持电路,两级电荷域2.5-bit子级电路,8级电荷域1.5-bit子级电路和最后一级电荷域3-bitflashADC电路。由于电荷域流水线ADC各子级电路对于共模电荷误差非常敏感,因此必须使用共模电荷控制电路[8]。

图5 14位250MSPS ADC系统框图

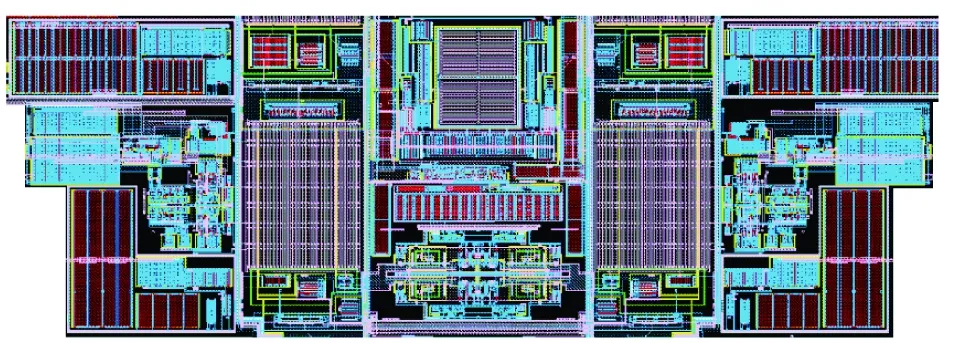

图6所示为应用本文所设计的电荷域流水线ADC子级电路版图布局方式的14位250MSPS流水线ADC电路的芯片概貌图和测试结果。ADC样片的概貌图如图6(a)所示,图中芯片上部基准电压产生和共模电荷控制电路,中间部分为采样保持电路和锥形电荷域流水线ADC各级子级电路,下部为时钟接收、DLL及其驱动电路,最右侧为数字校准逻辑部分。所设计14位ADC采用0.18um1P6MCMOS工艺流片,整个ADC芯片电路包括PAD和ESD保护电路在内的面积为2.6×4mm2,其中采样保持和11级子级电路面积为0.8×1.8mm2,共模电荷控制电路占用了0.4×1.3mm2的电路面积。图6(b)所示为ADC测试得到的FFT频谱图,在240MHz采样条件下对于20.1MHz正弦输入信号转换得到的无杂散动态范围(SFDR)为78.1dBc,信噪比(SNR)为70.5dBFS,信噪失真比(SNDR)为69.6dBFS,整个芯片的功耗仅230mW。

图6 ADC芯片概貌图和测试结果

4 结 语

本文在对电荷域流水线ADC子级电路结构和原理进行分析的基础上,设计了一种基于普通CMOS工艺、适用于高速高精度电荷域流水线ADC的子级电路版图布局方式。基于所设计的子级电路版图布局方式,论文采用1P6M0.18μmCMOS工艺完成了一种14位250MSPS电荷域流水线ADC的设计和流片,测试结果表明该ADC电路在240MSPS采样条件下对于20.1MHz的输入信号得到的SNR为70.5dBFS,显示出非常好的综合性能,证明了所设计的电荷域流水线ADC子级电路版图布局方式的有效性。本文所设计的子级电路版图布局方式非常适合于应用在高速高精度电荷域流水线ADC的版图布局设计工作中。

[1]AhmedM.A.Ali,AndyMorganandChrisDillon,et.al,.A16-bit250-MS/sIFSamplingPipelinedADCwithBackgroundCalibration[J].IEEEJournalofSolid-StateCircuits, 2010, 45(12): 2612-2613.

[2]Payne,R.Corsi,M.Smith,D. ,et.al.A16-Bit100to160MS/sSiGeBiCMOSPipelinedADCWith100dBFSSFDR[J].IEEEJournalofSolid-StateCircuits, 2010, 45(12): 2613-2622.

[3]Bing-NanFang,Jieh-TsorngWu.A10-Bit300-MS/sPipelinedADCWithDigitalCalibrationandDigitalBiasGeneration[J].IEEEJournalofSolid-StateCircuits, 2013, 48(3):670-683.

[4]ChangyiYang,FuleLi,WeitaoLi,etal.An85mW14-bit150MS/spipelinedADCwith71.3dBpeakSNDRin130nmCMOS[C] //ProcofAsiaSolid-StateCircuitsConference,Singapore:IEEE, 2013:85-88.

[5]Setterberg,B. ,Poulton,K. ,Ray,S.,etal.A14b2.5GS/s8-way-interleavedpipelinedADCwithbackgroundcalibrationanddigitaldynamiclinearitycorrection[C] //ProcofInternationalSolid-StateCircuitsConference.SanFrancisco:IEEE, 2013: 466-467.

[6]Ali,A.M.A. ,Dinc,H. ,Bhoraskar,P.etal.A14Bit1GS/sRFSamplingPipelinedADCWithBackgroundCalibration[J].IEEEJ.Solid-StateCircuits, 2014, 49(12),pp. 2857-2867.

[7]Miyahara,Y. ,Sano,M. ;Koyama,K.etal.A14b60MS/sPipelinedADCAdaptivelyCancellingOpampGainandNonlinearity[J].IEEEJournalofSolid-StateCircuits, 2014, 49(2): 416-425.

[8]MichaelAnthony,EdwardKohler,JeffreyKurtze,et.al.AProcess-ScalableLow-PowerCharge-Domain13-bitPipelineADC[C] //ProcofSymposiumonVLSICircuits.Honolulu:IEEE, 2008. 222-223.

[9]ChenZhenhai,HuangSongren,ZhangHong,et.al.A27-mW10-bit125-MSPSCharge-DomainPipelinedADCwithPVTInsensitiveBoostedChargeTransfer[J].JournalofSemiconductors, 2013, 34(3):035009

[10]ChenZhenhai,QianHongwen,HuangSongren,et.al.Lowpowertime-interleaved10-bit250MSPSchargedomainpipelinedADCforIFsampling[J].JournalofSemiconductors, 2013, 34(6): 065005.

张甘英(1977—),女,福建武平人,高级工程师,2000年毕业于南京理工大学电子信息工程专业,长期从事数模混合集成电路版图设计工作,主要研究方向为数模混合集成电路版图设计,在国内外期刊和国际会议发表论文多篇,授权专利2项;E-mail:diaoyuds@126.com

陈珍海(1982—),男,安徽黄山人,在读博士后,高级工程师,2014年毕业于西安电子科技大学微电子学与固体电子学专业获博士学位,现在中国电子科技集团第58研究所博士后工作站工作,主要研究方向为高速低功耗数模混合集成电路设计,在国内外期刊和国际会议发表论文30余篇,授权专利24项。

Floor-planning Method of Sub-stage Circuit for Charge Domain Pipelined ADCs

ZHANG Gan-ying, CHEN Zhen-hai, WEI Jing-he ,YU Zong-guang

(No.58thResearch Institute, China Electronic Technology Group Corporation, Wuxi, Jiangsu 214035, China)

The circuit structure and the scheme of the sub-stage for charge domain pipelined ADC is analyzed. And a new floor-planning method of the sub-stage circuit suitable for high speed high precision charge domain pipelined ADC based on CMOS process is designed. Based on the newly designed floor-planning method of the sub-stage circuit and a high precision metal-on-metal capacitor matching technique, the layout design of typical charge domain sub-stage circuit has been finished and successfully used in a 14-bit 250MSPS charge domain pipelined ADC in 0.18 μm CMOS 1P6M 1.8 V process. Test results show the 14-bit 250MSPS ADC achieves the SNR of 70.5dBFS with 20.1 MHz input at 240MSPS, while consumes the power consumption of 230 mW and occupies an area of 2.6×4mm2. The layout design process has successfully realized the performance of ADC circuits.

Pipelined Analog-to-Digital Converter; Charge Domain; Layout Design; Sub-stage Circuit; Capacitor Matching

10.3969/j.issn.1673-5692.2016.02.013

2016-01-29

2016-03-06

国家自然科学基金(61474092)