基于FPGA的模拟信号采样和隔离传输系统设计

张德华, 傅晓程, 靳晓光

(浙江大学 电气工程学院, 浙江 杭州 310027)

基于FPGA的模拟信号采样和隔离传输系统设计

张德华, 傅晓程, 靳晓光

(浙江大学 电气工程学院, 浙江 杭州310027)

针对电子系统中模拟信号采样以及隔离传输的要求设计了该系统。发送端由多通道A/D转换器实现模拟信号的数字化,FPGA作为核心部件实现转换控制和数据处理,产生能够通过单光纤进行传输的数字码流,接收端提取有效数字信号并存储,供控制系统使用,同时通过D/A转换器进行信号还原以便观察。进行仿真和实验测试表明,该方法抗干扰能力强、误码率低、传输速度高。该传输系统的设计和实现可由本科生在实验室完成,作为电子系统课程设计的可选择方案。

模拟信号; 隔离传输; FPGA; 编码

现代电子系统一般采用数字控制方式[1-2]。传统的传感器只能采样一路信息,并传输到控制端后进行一次模数转换,传输和转换效率低,且易受干扰,不能满足需要多路信号采样和反馈的电子系统实时控制和高隔离性能的要求。为此设计了多路模拟信号的数字化隔离传输系统。该方法是:在发送端先由多通道A/D转换器实现模拟信号的采样和数字化,由现场可编门阵列(FPGA)进行转换控制和数据处理,产生的数字码流通过光纤传输,在接收端将有效数字信号提取出来,供控制系统使用,同时通过D/A转换器进行信号还原,以便对有效数据进行观察和验证[3]。

该系统不仅是对现代电子系统数控技术的一项改进,而且由于包含电子技术课程中多个知识点,例如模拟信号的采样放大、A/D和D/A转换、数字信号的编码、同步等处理手段,可作为综合性的电子系统设计课题,由大二、大三年级本科生在实验室完成,既巩固电子技术课程理论知识,又能够培养和激发学生对电子系统设计的兴趣爱好。

1 硬件结构

1.1总体方案设计

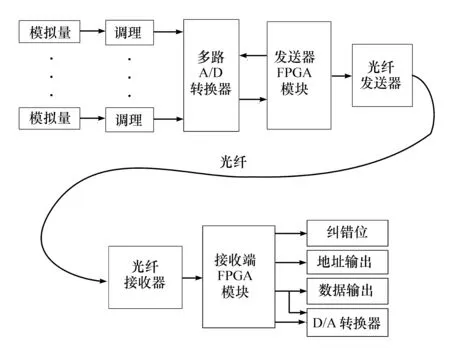

硬件总体框图如图1所示,其工作原理:电子系统的采样电量通过调理模块实现模拟信号的增益和电平偏移等调节,调理后的输出电压需与A/D转换器的电平匹配;然后经A/D转换后送入FPGA进行处理,FPGA负责A/D转换器的控制、传输协议的生成和对协议进行编码处理;光纤发送器将FPGA输出的电信号转换为光信号,并通过光纤传输到接收端,在接收端再用光纤接收器将光信号还原为电信号;接收端的FPGA负责数据分离和解码等处理,将有效信号提取出来,供控制电路取用;在接收端,为了方便观察信号是否正确,加一级D/A转换,将提取出的有效数字信号还原成模拟信号,和初始输入模拟信号进行对比观察。此外,协议中包含校验位,数据被接收端提取后若未通过校验,则代表传输出错,此帧数据将被丢弃。

图1 硬件总体框图

1.2隔离传输系统发送端设计

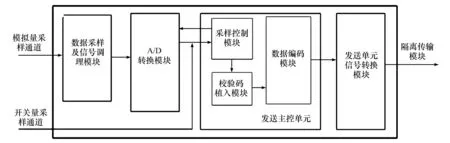

图2是发送单元的结构示意图。

图2 发送单元结构示意图

数据采样及信号调理模块采集模拟量信号并发送到A/D转换模块。A/D转换器选用TI公司生产的4通道12位串行ADS7950[4]。

信号输入A/D转换器之前,需要进行信号调理。以正弦波信号为例,ADS7950的模拟输入电压范围为2.7~5.25 V,因此需要对输入的正弦波进行电平偏移和幅度调整,运算放大器LM358可实现调理功能。

A/D转换模块将模拟量信号转换成数字量信号并发送给采样控制模块。发送单元还支持由采样控制模块直接采集开关量信号。

采样控制模块将数字信号进行扩展以使扩展后的信号包含开始标识位、地址位、数据位和结束标识位。扩展后的信号发送到校验码植入模块。校验码植入模块给所接收到的扩展后的信号植入校验位形成新的数据帧并发送到数据编码模块,数据编码模块则将新的数据帧进行编码并将编码后的高低电平信号发送到发送单元信号转换模块。

发送单元信号转换模块由HFBR-1527光纤发送器构成,HFBR-1527实现电—光信号的转换,将光信号通过光纤发送到接收单元信号转换模块中[5]。

1.3隔离传输系统接收端设计

图3是接收单元的结构示意图。

接收单元信号转换模块由型号为HFBR-2526的光纤接收器构成,完成光—电信号的转换。接收单元信号调理模块在将所接收到的电信号进行电压幅值匹配后转换为TTL信号,分别发送到时钟提取及同步模块和起始指令判断模块。

时钟提取及同步模块从所接收到的TTL信号中提取出同步时钟信号,和TTL信号同时发送给解码校验模块和起始指令判断模块。起始指令判断模块负责提取起始指令,解码校验模块对TTL信号进行校验并将校验结果也发送给数据解码模块。数据解码模块根据起始指令、同步时钟信号和校验结果对TTL信号进行解码得到地址位和数据位信息,并发送给存储输出模块的寄存器中。

2 软件设计

FPGA选用Altera公司生产的Cyclone系列芯片EP1C6T144C8和低成本串行配置器件EPCS4。用VHDL编写收发单元控制模块,在Quartus II 平台上完成仿真和器件配置[6-7]。

图3 接收单元结构示意图

2.1发送端软件设计

发送端FPGA实现的功能有:

(1) 控制A/D转换器。ADS7950内置多路模拟开关,使用时需进行芯片工作模式、采样通道等设置。本例采用自动模式1进行工作模式配置。

(2) 定义传输协议。采用异步串行通信方式,符合单光纤传输情况下数据传输的要求。本设计定义了一个传输协议,如图4所示。该协议实现两个功能:一是多路信号的总线传输;二是使接收端正确判断出有效数据的起止时刻。协议数据帧的第一位是起始位,以逻辑“0”为有效状态,表示有效数据传送开始;紧接着是4位地址,然后是12位数据,两者均从低位开始传输;有效数据结束后发送一位奇偶校验位,用于有限差错检测;最后以一位逻辑“1”作为停止位,标志着一帧数据传送结束。

图4 传输协议的数据格式

(3) 编码模块。数字信号需要经过编码,变换成适合在光纤中传输的光纤线路码[8]。因此需对传输协议进行编码处理。本设计选用CMI编码方式。

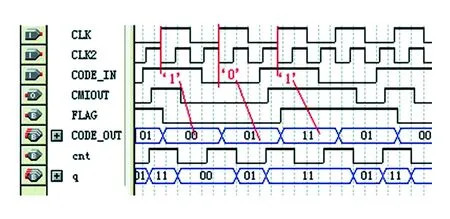

CMI码是一种两电平非归零码(nrz),其编码规则为:“1”码交替用“11”和“00”两位码表示;“0”码固定用“01”表示。 “00”和“11”的交替出现使“0”、“1”在码流中平衡[9]。“10”作为禁用字。CMI码最大连“0”和连“1”数都是3个。因而该码的直流起伏和低频分量都很小,定时含量很丰富,很容易进行误码监测。对该CMI编码模块进行功能仿真,仿真结果见图5。

图5中,CLK为原始时钟,用于读取待编码数据CODE_IN,CLK2为2倍频之后的时钟,可通过直接调用EP1C6中的Cyclone PLL(锁相环)[10-11]实现。CODE_OUT为编码之后的并行数据,经过并串转换后形成CMI码输出CMIOUT,可由CODE_OUT观察编码是否正确。

图5 CMI编码模块时序仿真结果

2.2接收端软件设计

接收端FPGA需完成协议接收及有效数据的提取。各模块功能如下:

(1) 时钟提取。从接收的数据中恢复数据同步时钟,再用恢复的同步时钟读取数据[10],从而保证读取数据的正确性[12]。时钟提取包括边沿检测、时钟倍频和计数器。边沿检测采用D触发器和非门实现,边沿检测电路的输出作为计数器的复位信号,计数器的最高位即为异步数据的同步时钟。用这种方法提取的时钟和CMI码流频率一致,为40 MHz。

(2) CMI解码。提取出的同步时钟可直接为解码所用。解码是将CMI码流还原成普通的二进制代码。CMI编码中“10”是禁用码组,在数据传输正确的情况下,CMI码流中下降沿时刻必定是新码组的开始时刻。将“00”、“11”还原为“1”,“01”还原为“0”即可完成解码。图6为解码过程的仿真结果。datain是CMI码,经时钟提取产生同步时钟clockout,解码的结果可通过nrz信号观察到,该结果是未经过数据分离的二进制协议结果。

图6 CMI解码模块时序仿真结果

(3) 接收协议。接收协议就是把协议中的4位地址、12位数据和奇偶校验位分离出来。

(4) 数据存储模块。从协议中分离出的数据先存储到RAM中。将各个采样点的数据分开存储,便于后续电路的取用。直接调用EP1C6中的LPM_RAM_DP模块可以实现该功能。

(5) 控制D/A转换器[13]。D/A转换器AD5342是为了方便观察提取出的有效数据是否正确而设置的,其控制指令来自FPGA。

3 隔离传输系统性能测试

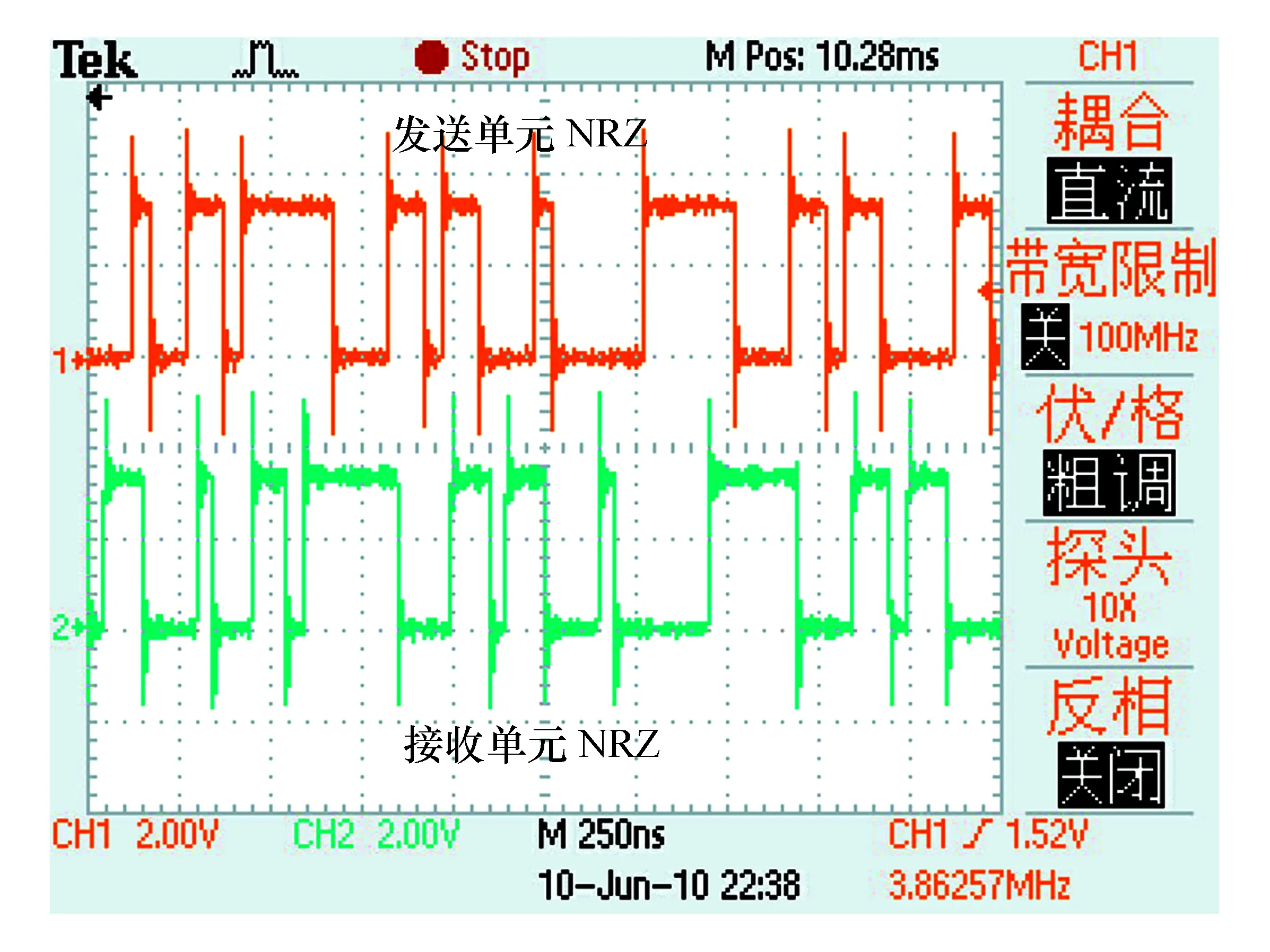

图7是发送单元的原始数据帧和接收单元编码还原后的原始数据帧比较。竖线括出的为一个完整的数据帧。对比发现二者的延时约为170 ns。图8为光纤(包括光纤模块的信号调理电路)两端CMI码流,二者数据保持一致,延时约为30 ns。

图7 收发双方原始数据比较

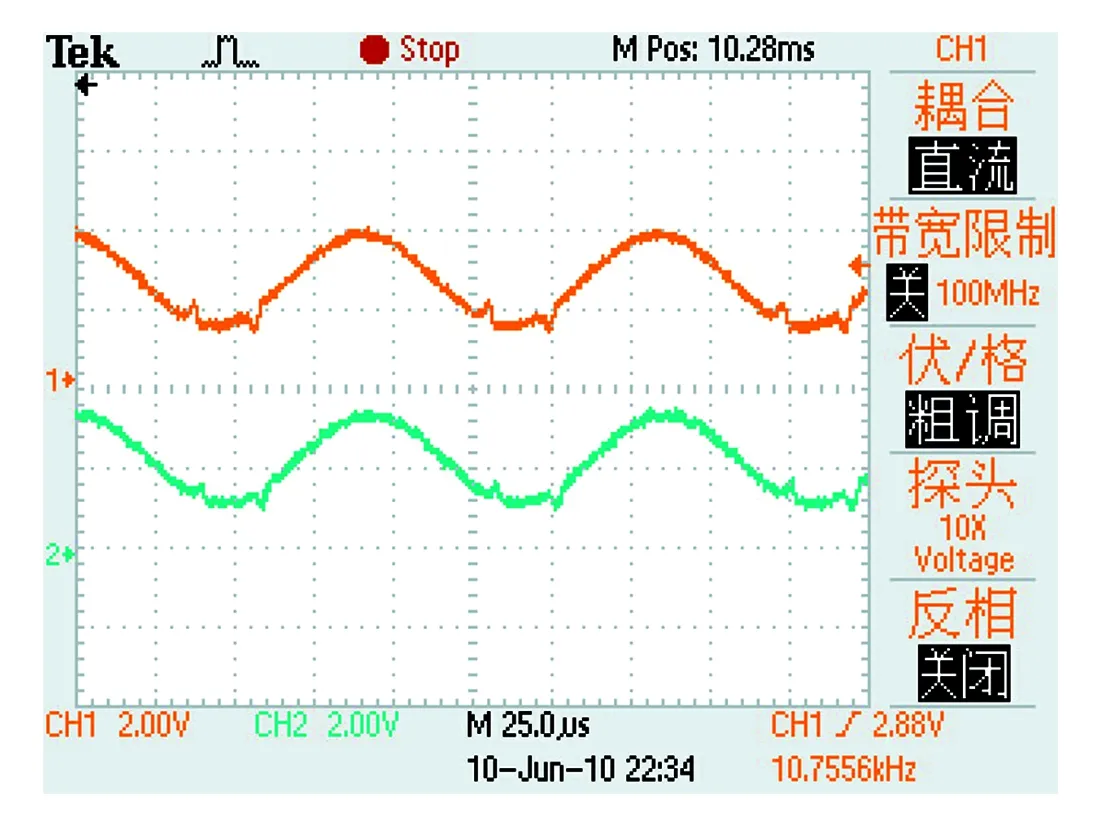

图9为发送单元采样信号和接收单元还原信号的对比波形。信号是频率为10 kHz的正弦波形。对比发现,信号经采样、编码、传输、解码、D/A转换后并没有发生畸变。

图10为发送和接收单元实物图。

图8 光纤两端信号

图9 正弦波采样与还原波形

图10 发送和接收单元实物图

4 结语

本文设计制作的多路模拟信号的隔离传输系统的收发模块系统稳定,误码率小,抗干扰能力强,实时性强,能很好地解决全数字控制装置中电压、电流、转速、温度等信号的数字化传输问题。该系统可作为电类专业大二、大三年级的本科学生进行课程设计的选择。其特点和可行性表现在:

(1) 与工程应用相结合,能激发学生对电子系统设计的兴趣;

(2) 模拟数字电路相结合,软件编程和硬件调试相结合,具有综合性,全面提高学生的动手能力;

(3) 系统结构简单,可行性好,在现有的电子技术基础知识层面就可以实现;

(4) 学生的集成电路应用能力得到有效的锻炼,并且对FPGA的应用从入门达到熟练,为进入专业训练打下良好的基础。

References)

[1] 陈小桥,陈慧,张令.基于MSP430F6638的单相正弦波逆变系统设计[J].实验技术与管理,2015,32(7):75-79.

[2] 卢慧芬,林斌,孙丹,等.DSP电机控制综合实验平台研制[J].实验技术与管理,2014,31(10):97-102.

[3] 饶文贵,田建生.DSP 串行数据光纤传输系统设计[J]. 计算机测量与控制,2007,15(1):127-128.

[4] Texas Instruments Inc. ADS7950 Data Sheet[EB/OL].[2015-12-21].http://www.ti.com/product/ADS7950/datasheet?keyMatch=ads7950&tisearch=Search-EN-Everything.

[5] 光纤收发器白皮书[EB/OL]. (2006-06-06)[2015-12-21].http://www. cnii. com.cn/20060529/ca355632.htm.

[6] 张小平,赵不贿.Altera新型FPGA器件的配置方式[J].微处理机,2006(4):93-95.

[7] Altera Corporation. Cyclone FPGA Family Data Sheet[EB/OL].[2015-12-21]. http://www.altera.com.cn/content/dam/altera-www/global/zh_CN/pdfs/literature/ds/ds_cyc.pdf?GSA_pos=2&WT.oss_r=1&WT.oss=Cyclone+FPGA+Family+datasheet.

[8] 王廷尧. 光通信设备基础[M]. 天津: 天津科技出版社,1992.

[9] 罗杰. Verilog HDL与数字ASIC设计基础[M]. 武汉:华中科技大学出版社,2008.

[10] 远坂俊昭. 锁相环(PLL)电路设计与应用[M].何希才,译.北京: 科学出版社,2006.

[11] Using PLLs in Cyclone Devices:Cyclone Handbook [EB/OL].[2015-12-21].http:///www.altera.com.cn/content/dam/altera-www/global/zh_CN/pdfs/literature/hb/cyc/cyc_c51006.pdf?GSA_pos=2&WT.oss_r=1&WT.oss=Using+PLLs+in+Cyclone+Devices.

[12] 苏红,张俊辉. 利用FPGA内部DLL实现数字时钟恢复[J]. 科学技术与工程,2007,7(18):4720-4722.

[13] DAC的分类与指标[EB/OL]. (2009-03-08)[2015-12-21].http://www.21ic. com/app/analog/200903/33250.htm.

Design of analog signal sampling and isolated transmission system based on FPGA

Zhang Dehua, Fu Xiaocheng, Jin Xiaoguang

(College of Electrical and Engineering, Zhejiang University, Hangzhou 310027, China)

This system is designed for the requirement of multi-channel analog signal sample and isolated transmission. The sending unit takes an multi-channel A/D converter to digitize the analog signals. The field programmable gate array (FPGA) is taken as the core component to realize conversion control and data process,generate a digital bit stream which can be transmitted in a single optical fiber. The receiving unit extracts effective digital signals and stores it into memory for control use. A D/A converter is used for observing the reduction signal. Sending and receiving unit modules are built for the simulation and experiment. The results prove that the method has strong anti noise ability,low error rate and high transmission speed. The undergraduate students have the ability to design the transmission system. Therefore the implementation can be completed in the laboratory. The proposed design scheme can be taken as an option in the curriculum design of electronic system.

analog signal; isolated transmission; FPGA; coding

DOI:10.16791/j.cnki.sjg.2016.06.019

2015-12-30

浙江省教育厅科研项目(Y201326823)资助

张德华(1972—),女,浙江杭州,博士,副教授,主要从事电子技术基础理论和实验教学和科研工作.

E-mail:eedhzh@zju.edu.cn

TN710

A

1002-4956(2016)6-0070-04