闪电定位仪的通信接口设计

田新兴,严 飞,刘银萍

(南京信息工程大学 信息与控制学院,江苏 南京 210022)

闪电定位仪的通信接口设计

田新兴,严 飞,刘银萍

(南京信息工程大学 信息与控制学院,江苏 南京 210022)

文章主要开展闪电定位仪通信接口设计的工作。首先,研究以Altera FPGA为核心的控制器,主要用于数据采集系统及数据流的处理过程;其次,针对闪电定位仪通信接口设计要求,细化通信协议;最后,通过在FPGA上编程实现将采集到的闪电数据传输到上位机,配合LabView上位机波形分析软件对单次闪击信号进行特征分析。

闪电定位;通信接口;FPGA

闪电定位仪是一种监测雷电发生的气象探测仪器。目前,国家闪电定位网采用的ADTD型闪电定位仪,其探测过程是在天线上感应出回击的南北向和东西向磁场信号以及电场信号,并直接送到信号处理板,两路磁场信号信道完全对称。信号处理板对三路信号分别进行前置放大,低通滤波,积分放大,滤波,差分变换等技术处理,输出干净的磁场波形和电场波形[1]。

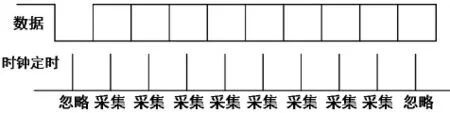

闪电定位仪采集到的波形信号最终要输出到上位机,与上位机通信。本文以FPGA为控制核心,设计闪电定位仪与上位机的通信接口,可以充分利用FPGA资源将数据按照协议传输。异步通信,可实现全双工收发。数据格式如图2所示,一个数据帧包括起始位,数据位,奇偶校验位和停止位。

串口传输数据一般是一帧数据11位(见表1),也可以无校验位。

表1 数据位功能

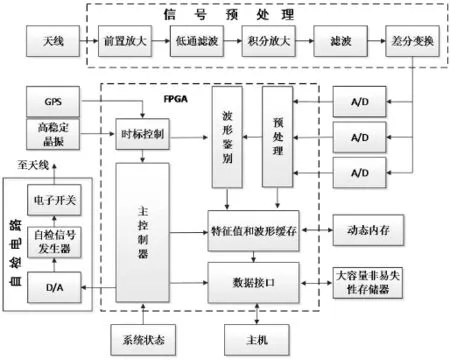

1 系统结构

闪电定位仪系统构架如图1所示,基本结构组成有:信号预处理,FPGA,自检电路,天线,GPS等。利用GPS全球定位系统的同步授时和可编程逻辑器件提供高精度的同步时间标记,多台定位仪可以得到雷电脉冲到达个站之间的时间差,进而确定闪电的位置[2]。天线接收到闪电信号后经信号预处理电路去除噪音和毛刺等部分,经过A/D转换为数字信号,然后在FPGA内处理并鉴别接收到的信号是否是闪电波形。如果满足闪电波形的特征,则将采集到的数据缓存到内存中。本系统的关键部分是FPGA处理并鉴别数字信号,提取特征值,本文主要工作是将处理后的最终结果传输至上位机的通信接口。

2 数据接口

2.1UART的工作原理

图1 闪电定位仪系统构架

UART是一种串行数据总线,用于

图2 数据帧格式

在串口的总线上“高电平”为默认状态,当一帧数据开始传输时必须先拉低电平,这就是第0位的作用。第0位过后就是有意义的8个数据位,最后的两位是校验位和停止位。

另外,串口传输的另一个重要参数就是“波特率”。在微观上“波特率”就是串口传输中“一个位的周期”。

闪电信号经A/D转换后,my_uart_rx以设定好的波特率采集信号,如图3所示。根据奈奎斯特采样定理,在A/D信号转换过程中,采样频率fs.max大于信号中最高频率fmax的2倍时,采样后的数字信号会完整地保留原始信号中的信息。一般实际应用中保证采样频率为信号最高频率的5~10倍,常用的波特率有9600 bps和115200 bps[3]。

图3 数据采集时序

因为现实环境中存在各种电磁干扰,导致数据的起始部分不稳定,所以,一般在数据中间部分采样。如图4所示,在输入一帧数据时,当my_uart_rx检测到rs232_rx由高电平跳变到低电平,向speed_select发送bps_start信号,然后speed_select模块在每一个时钟上升沿计数。假设时钟为50MHz,波特率为9600bps,每位为1/9600秒,需要计5208个周期(计数5208),要在中间采样所以计数满2604并且bps_start为1,方可产生clk_ bps信号。

对于第0位数据,采取忽略态度,只需采集接下来的8位数据,最后校验位(可以无校验位)和停止位,也采取了忽略的操作。串口传输数据的起始是“从最低位开始,到最高位结束”[4]。整体系统的硬件逻辑框结构如图4所示。

图4 硬件逻辑框

2.2接收模块设计

当电平检测检测到接收引脚(pin_rx_in)电平由高变低时,接收控制部分向波特率选择模块发送开始计时信号(bps_start),波特率模块在时钟周期的上升沿计数,当计数满时向接收模块发送脉冲(clk_bps)。接收到clk_bps后,将pin_rx_in的数据缓存到寄存器reg[0]-reg[7],然后通过rx_date[7∶0]发送到RAM中。图5为接收部分的示意图。

图5 接收模块

2.3RAM模块设计

接收模块接收完整数据后向RAM控制模块发送rx_int信号,使控制模块控制RAM的wren(写使能)信号置位,并输出写地址信号,rx_date[7∶0]存储到wraddress的地址。之后,每收到rx_int信号时要使wraddress=wraddress+1,在新的地址写入接收到的新数据,如图6所示。

图6 控制模块和RAM模块

2.4控制模块

将接收模块发送的rx_int信号作为RAM写入使能信号,并控制wraddress写地址自增,将发送模块的tx_done信号和send_en信号分别作为读地址变换信号和发送模块发送数据的使能信号。当发送模块发送出去一帧数据后,读地址rdaddress自增,然后send_en置1,发送使能。

2.5发送模块设计

RAM接收数据后,控制模块向发送模块发送一个发送使能(send_en)信号,读取读地址rdaddress内的数据到寄存器Q[7∶0],传送给发送模块,发送模块在波特率模块的控制下发送数据到PC,发送完一帧数据后向控制模块发送一个发送完成信号,tx_done和send_en信号均为高电平时,方可发送下一帧数据,如图7所示。

图7 数据发送模块

2.6波特率选择模块

当芯片晶振为50MHz时,波特率为9600bps,发送一位的时间是1/9600s。即计数1/9600×50M=5208,根据数据采集的原则,当计数不满2604或超出2604但不到5208时继续计数,达到2604且bps_start=1时输出信号,计数满5208时清零,如图8所示。

图8 波特率选择模块

3 系统验证

真实的大气放电现象的复杂多变的,主要包括对地放电,云层内部放电,云对云放电[4]。图9为捕获到的闪电波形

图9 接收到的闪电波形

图,包括闪电触发后的南北向磁场信号,东西向磁场信号和电场信号。从波形可以明显看出闪电波形的不规律性,可以由接收到的信号的场强和脉冲电磁波传播规律推算出雷击电流大小,以便用于后续研究。

4 结语

闪电定位仪对天线接收到的信号进行前置放大,低通滤波,积分放大等处理,经过模数变换后,FPGA对其进行鉴别、分析,提取出相应的特征点。本文开展的闪电定位仪通信接口设计的工作,可以有效地将之前处理后的波形特征信息传输至上位机,实现基于FPGA的雷电数据采集、数据处理和数据上传的功能。本设计还可以借助GPRS的数传模块,实现远程通信,将多站点雷电数据传输至服务器,以实现基于时差算法的闪电定位。

如今,4G数传模块的发展趋于成熟,下一步的工作将秉承现有的传输协议,使系统不仅能传输处理后的特征点信息,还将实现数据的低延时全波形传输,其对有效分析闪电的发展过程有重要意义。

[1]黄志兴.ADTD型闪电定位仪的日常使用和维护[J].气象水文海洋仪器,2015(2):112-113.

[2]肖坤峰,孙秀斌,杨崧令,等.基于FPGA的雷电定位系统高精度时标设计[J].电子技术应用,2013(11):50-52.

[3]聂涛,许世宏.基于FPGA的UART设计[J].现代电子技术,2006(2):127-129.

[4]田乐,张勇.基于FPGA实现异步串行通信[J].现代电子技术,2013(13):71-73.

[5]谭涌波.《雷电学原理》课程建设与发展[J].教育教学论坛,2015(33):202-203.

[6]RAKOV V A,MALLICK S,NAG A,et al.Lightning Observatory in Gainesville(LOG),Florida:A review of recent results[J]. Electric Power Systems Research,2014(113):95-103.

[7]MURTHA J B, SKINNER II W H.Lightning detection apparatus and methodology[M].US:US5977762 1999.

[8]RAKOV V A,UMAN M A,RAIZER Y P.Lightning:Physics and Effects[J].Physics Today,2006(57):63-64.

Lightning of Communication Interface Design

Tian Xinxing, Yan Fei, Liu Yinping (Nanjing University of Information Science & Technology Information and Control College, Nanjing 210022, China)

This paper carried out the lightning locator communication interface design work.Firstly,in order to Altera FPGA as the core controller,primarily for data acquisition and processing system data flow; Secondly,lightning locator communication interface design requirements,refine the communication protocol; and finally,by the FPGA programming will be collected the lightning data to a PC,the PC with LabView waveform analysis software for a single strike signal characteristic analysis.

Lightning location; communication interface; FPGA

项目名称:江苏省高校自然科学研究面上项目;项目编号:15KJB170010。项目名称:江苏省自然科学;项目编号:BK20150903。项目名称:南京信息工程大学人才启动基金项目;项目编号:S8113106001。

田新兴(1994-),男,河南新乡,本科。