基于FPGA的误码分析仪设计

丁鑫 耿涛 郭娟 方佳朕 张晓鹏

摘 要:为了设计出基于FPGA的误码分析仪,选用以STC10F08XE单片机为主控制器、以EP1C3T144C8N芯片为误码检测、USART GPU串口屏为显示和控制以及EPCS和MAX232为下载程序,完成了整个硬件系统的设计。并在整个硬件系统实现的基础上,进行了M序列的产生、数据同步实现、误码监测统计以及液晶显示控制等相关实验。结合硬件电路以及实现的功能设计了各个功能模块的软件流程图,并结合流程图编写了各个模块的实现程序,然后结合硬件完成了联合调试,最终实现了系统的预期功能。

关键词:误码分析仪;FPGA;M序列;STC10F08XE

中图分类号:TN911 文献标识码:A 文章编号:2095-1302(2016)07-00-04

0 引 言

在通信系统中,由于信号在传输过程中衰变引起信号电压的变化,导致信号在传输过程中遭到破坏,产生误码。误码分析仪便是测试误码率的测试仪器,本文旨在通过误码分析仪模块的设计来深入了解其原理及使用方法[1]。

1 总体方案设计

1.1 系统需求分析

系统使用FPGA和单片机共同控制的方式,使系统具有很高的集成度,并且方便扩展和升级。经过调研和讨论分析,整个设计的基本功能包括如下几部分[2]:

(1)八种测试速率可调:1 K/10 K/100 K/500 K/1 M/2 M/5 M/10 M速率;

(2)三种测试码型可选:9位、15位、23位伪随机序列码;

(3)误码率的统计和计算;

(4)误码的发送、接收、同步以及手动插入误码的设计;

(5)TFT-LCD彩屏显示和触摸按键的控制;

(6)单片机与TFT-LCD的通信设计;

(7)误码测试仪的菜单显示设计;

(8)外部指示系统的设计;

(9)时钟锁相环设计。

1.2 系统设计方案

误码分析仪系统分为硬件设计和软件设计两部分。选用FPGA芯片实现误码的测试,采用Verilog硬件描述语言通过EDA软件设计外围电路和必要的功能。采用单片机作为主控芯片,控制误码测试的启动、加误码、变速率、换码型、TFT-LCD液晶显示、触摸按键等。

2 硬件电路设计

2.1 系统硬件结构框架

整个系统设计中通过CPU访问FPGA芯片与TFT-LCD通信,通过FPGA芯片实现码型的产生与发送、码型接收的同步、码型的比较、速率的切换等逻辑功能;通过TFT-LCD实现误码率实时显示以及通过其触摸功能反馈控制整个系统的功能。系统结构框图如图1所示。

2.2 电源电路设计

系统采用5 V供电,模块内部FPGA普通的IO口电源电压需要3.3 V供电,而其PLL锁相环所在的内核LPM模块需要1.5 V供电。因此需要设计电压转换电路。具体设计电路如图2所示。

除此之外,设计中需要使用FPGA内部的PLL,为了避免数字器件产生的噪声影响倍频效果,该模块必须有单独电源和滤波设计[3]。具体设计电路如图3所示。

设计中,5 V电源经AS1117-1.5芯片降压至1.5 V,产生的1.5 V电源经过一个由磁珠和钽电容组成的退耦电路过滤后接入PLL电源[4]。

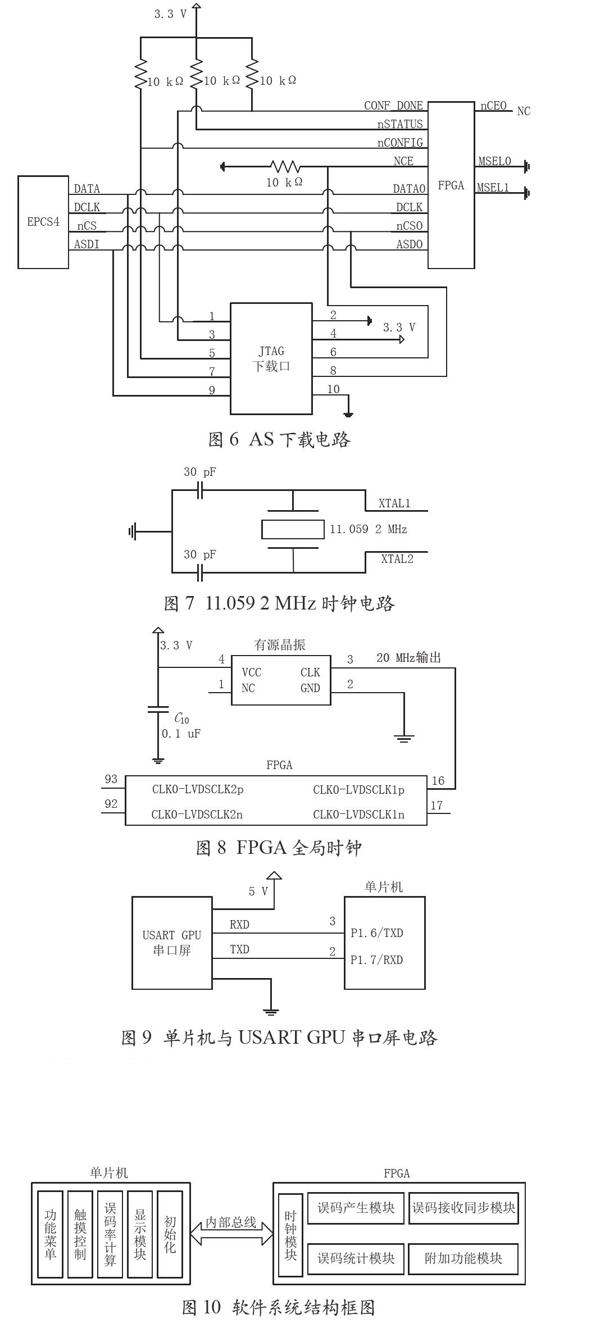

2.3 下载电路设计

RS-232电平与TTL电平转换设计采用MAX232以进行通信电平转换。具体设计电路如图4所示。

根据FPGA数据手册,设计的JTAG下载口电路如图5所示。

标准的JTAG接口是4线TMS、TCK、TDI、TDO,分别为测试模式选择、测试时钟、测试数据输入和测试数据输出[5]。

AS模式下载电路设计,参照数据手册设计的相应电路如图6所示。

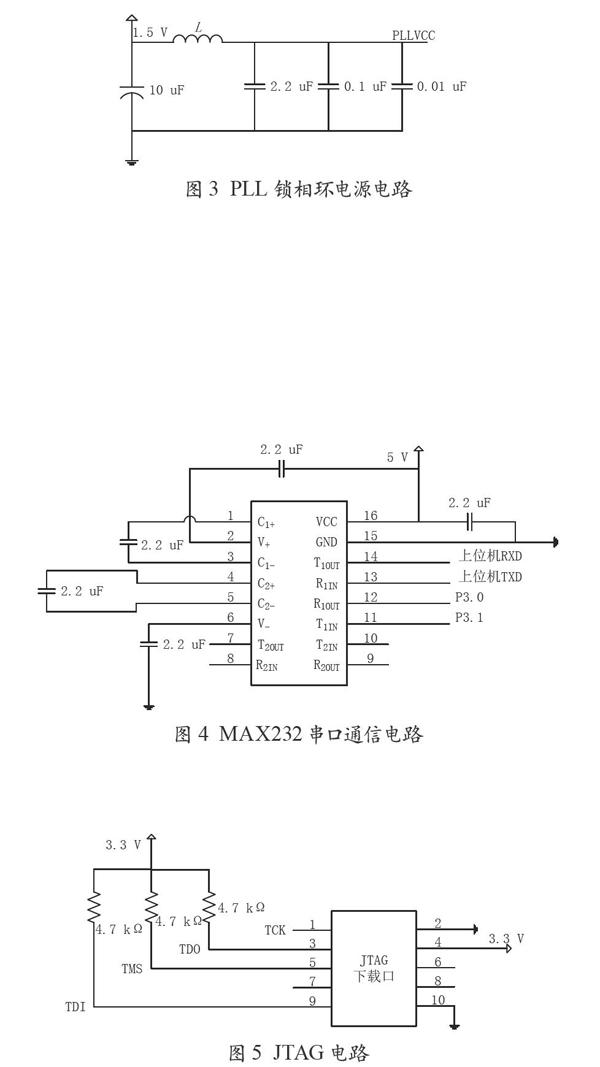

2.4 时钟电路设计

单片机时钟电路设计如图7所示。FPGA时钟电路整体设计如图8所示。设计中选用的FPGA芯片有4路专用时钟输入端口,可作为4个LVDS时钟信号输入或4个LVTTL时钟信号输入[6]。

2.5 USART GPU 串口屏的电路设计

误码分析仪系统与用户进行交互时,需要控制和显示模块,系统设计中采用单片机通过串口通信与USART GPU 串口屏进行数据交流、通信,由于其内部集成模块,所以外部电路简单。具体设计电路如图9所示。

3 软件设计总体结构

整个软件系统主要由FPGA芯片内部逻辑和单片机程序组成。具体结构框图如图10所示。

3.1 软件开发环境的建立

软件开发环境主要由QuartusⅡ11.0、Keil C51、ModelSim构成。

3.2 时钟模块的设计

本系统的时钟模块由PLL锁相环和时钟分频模块组成,该模块的输入输出如图11所示。

图11中inclk0是外部时钟输入,c0是PLL锁相环时钟输出,CLK是PLL时钟20 MHz信号输入,DIV[2..0]是分频值输入,而M_CLK、CLK1是两路时钟信号输出,其中M_CLK是码型发生速率,而CLK1是同步码型发生模块的码型发生速率,与M_CLK变化趋势相反。变化模式如图12所示。

本设计使用时钟分频的设计思想实现速率可调功能。具体设计方法如下:分频值由DIV[2..0]输入,按分频公式计算分频数等于(DIV+1)*2,将PLL倍频至20 MHz(由于本次设计仅仅需要10 MHz测试速率,所以无需倍频也可以实现,但为了后续功能增加,故保留PLL模块)时钟分频至10 MHz、5 MHz、2 MHz、1 MHz、500 kHz、100 kHz、10kHz、1 kHz,由M_CLK和CLK1输入系统。

3.3 PLL锁相环模块

PLL锁相环将低速率稳定的晶体振荡器倍频到更高频的稳定时钟。基本框图如图13所示。

3.4 M序列码的产生

本误码测试系统提供9位、15位、23位三种伪随机序列作为测试码型,以9位伪随机序列发生器为例介绍M序列的产生方法。

9位伪随机序列的特征方程为:F(X)=1+X5+X9,因此电路反馈线需要从第5级和第9级引出,通过模二加电路送到第1级输入端。具体设计如图14所示。

3.5 手动误码插入设计

手动插入误码即人为在发送的伪随机序列中插入已知个数的误码信号,然后在接收端接收信号,检测这些误码,最后将检测结果和插入误码进行比较,以此可以更加可靠地判断系统的误码性能[7]。具体设计思路流程如图15所示。

3.6 数据接收模块设计

数据接收模块的主要功能是将经过信道传输的伪随机序列码进行采样提取。数据接收模块设计图如图16所示。

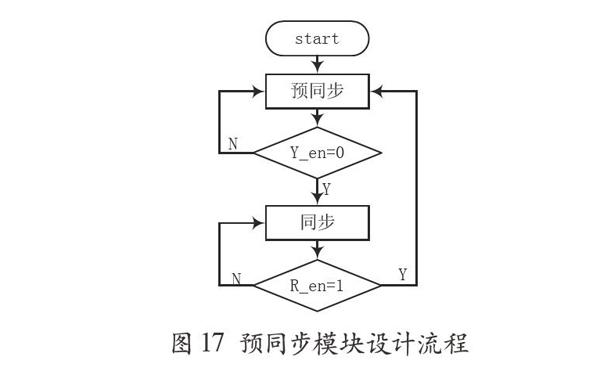

3.7 数据同步模块设计

本设计中的同步设计思路通过灌码同步实现,将接收数据随机抽取R位送至接收码组发生器的各个寄存器,此时接收端可以自身产生码组与输入码组进行比较,设定同步规则[8];除此之外,同步成功后需要设定失同步规则,本设计中采用的规则是:300个周期内若出现10个以上误码则收发两端失同步,若30 000个周期内出现1 000个以上误码则收发两端失同步,因此系统给出失同步信号[9],此时的测试数据不能体现系统性能,等待系统再次同步成功后进行测试。同步模块设计流程图如图17所示。

3.8 误码统计模块设计

整个误码统计模块的工作流程是:模块在同步状态中开始工作,通过R_en检测是否失同,若R_en=1则失同步,误码数清零,若R_en=0时表示误码率在可接受范围之内,继续测试,有误码则误码数加1,当测试超过30 000个测试周期时[10],整体误码数清零,一次测试结束。误码统计模块流程图如图18所示。

3.9 USART GPU 串口屏

USART GPU 串口屏模块包括UI界面设计模块、触摸按键设计模块两部分,主要实现测试数据的显示和测试系统参数的控制。

3.10 单片机总控制模块设计

单片机软件模块是整个软件设计的中枢,它主要包括控制部分、显示部分和处理部分三大模块。具体设计流程图如图19所示。

4 系统调试与结果分析

4.1 硬件调试

硬件测试主要包括单片机能否正常运行、FPGA能否正常运行、单片机和串口屏能否通信、下载器能否实现切换、EPCS能否下载程序并且是否能时刻为FPGA下载程序。

4.2 软件调试

软件调试主要包括FPGA和单片机两部分。FPGA调试首先是M序列的产生,接着是数据接收模块,最后同步。单片机程序调试时分别调试各个功能,最后将各个功能集于一体进行综合调试,实现整体功能。

最后将FPGA和单片机联调,实现误码分析仪的整体系统功能。

4.3 模块实体图

该模块的实体图如图20所示。

5 结 语

整个系统采用了软硬结合的设计思想,实现了误码率的实时测量、误码报警、无信号报警、全一报警、手动加误码等功能。

本误码测试系统是基于FPGA的在多个EDA软件共同工作下完成的设计。在通信技术日益发展的今天,FPGA在通信研发行业中的应用非常广泛,在ASIC中的前端仿真、基带通信的编码解码设计、数字图像处理等都有应用,本次设计实现了FPGA在通信中的一个应用设计,体现了FPGA设计方式的优越性。

参考文献

[1]官剑.基于FPGA的3G误码仪的设计与研究[D].武汉:华中科技大学,2011.

[2] Y Fan,Z Zeljko,MW Chiang .A Versatile High Speed Bit Error Rate Testing Scheme[J]. IEEEXplore, 2004: 385-400.

[3]张义芳.高频电子线路[M].哈尔滨:哈尔滨工业大学出版社,2009:223-243.

[4]童诗白,华成英.模拟电子技术基础[M].北京:高等教育出版社,2006:358-397.

[5] Lattice_Maehxo Mini Development Kit Users Guide(Rev EB41_00.5)[Z]. Lattice Corp, 2009: 23-37.

[6]郭天祥.51单片机C语言教程:入门、提高、开发、拓展全攻略[M].北京:电子工业出版社,2009:56-200.

[7] Gerd Vandersteen.Efficient Bit-Error-Rate Estimation of Multicarrier Transceivers[Z]. IEEE, 2011: 5-9.

[8] Barry, J.R,Chen-Chu Yeh.Adaptive minimum bit-error rate equalization for binary signaling[J].IEEE, 2010,48(7): 1226-1235.

[9]李新春.电信测试仪器原理及应用[M].沈阳:东北大学出版社,2008:158-166.

[10] An Overview of LVDS Technology[Z].National Semiconductor Corporation, 1998: 11-15.