异构双核SoC软件调试环境的研究与设计

王 品,袁春如,贺红卫

(1.中国兵器科学研究院,北京 100089;2.中国航天科工集团 第二研究院 706所,北京 100039)

异构双核SoC软件调试环境的研究与设计

王品1,袁春如2,贺红卫1

(1.中国兵器科学研究院,北京100089;2.中国航天科工集团 第二研究院 706所,北京100039)

摘要:分析了嵌入式系统远程调试原理,提出面向某异构双核SoC的调试环境设计方案,讨论了仿真器软硬件设计和调试代理软件设计等关键技术。该调试环境能够对目标平台进行在线编程和调试,解决了自主双核SoC处理器缺乏配套软件调试手段的实际问题,为目标平台的应用和推广提供了有力支撑,对其他面向多核处理器的调试环境设计具有参考价值。

关键词:异构双核SoC;仿真器;远程调试;USB;JTAG

0 引言

多核技术是提升CPU计算能力的重要途径。武器装备嵌入式系统对高精度、高性能和安全可控的计算需求不断提高,促使我国在核心电子器件领域的技术水平有了长足进步。目前,许多处理器已经能够自主研制,对相应的软件开发调试环境提出了迫切的需求。如果能够提供包括仿真器在内的、与处理器相配套的调试环境,将会给自主芯片的应用、推广与发展提供更加广阔的空间。

1 嵌入式系统远程调试原理

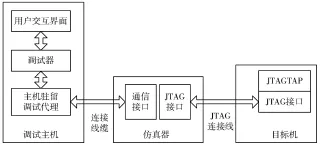

嵌入式系统一般使用远程调试的方式进行调试,一个典型的远程调试系统主要包括三个部分:调试主机、仿真器(调试协议转换器)和调试目标板。通常来说,调试主机通过某个接口(如并口、网口、USB接口)与仿真器相连,仿真器通过JTAG接口连接调试目标板,以此达到调试主机与调试目标进行交互的目的。调试主机运行调试器(如GDB)和调试代理,并为开发调试人员和目标系统的交互提供友好的用户界面。远程调试系统结构如图1所示。

图1 远程调试系统结构

相对于本地调试,远程调试具有以下特点:

(1)调试器和被调试程序运行在不同的计算机上,通过一定的通信方式将调试主机和目标板相连,绕开了目标板上软硬件资源有限的限制,为用户提供强大的调试环境。

(2)目标板上无需操作系统支持。目标板上即使运行操作系统,也主要是用于嵌入式应用的支撑,而不是用于目标板的开发环境平台。

(3)本地调试只能调试相同指令集的程序,而远程调试可以调试与主机不同指令集的程序,这一特点被称为交叉调试。

(4)由于调试器和被调试程序的分离,不可避免地引入了通信开销,对调试效率有一定影响。

2 JTAG调试标准

JTAG是JOINT TEST ACTION GROUP的简称。IEEE 1149.1标准就是由JTAG组织最初提出,并由IEEE批准和标准化的。所以IEEE 1149.1标准也称为JTAG调试标准。边界扫描(Boundary⁃Scan)是JTAG调试中的关键技术,其基本思想是在靠近芯片的输入/输出管脚上增加一个移位寄存器单元,因为这些移位寄存器单元都分布在芯片的边界上,所以被称为边界扫描寄存器(Boundary⁃Scan Register Cell)。当芯片处于调试状态时,这些边界扫描寄存器可以将芯片和外围的输入/输出隔离开来。通过边界扫描寄存器单元,可以实现对芯片输入/输出信号的观察和控制。对于芯片的输入管脚,可以通过与之相连的边界扫描寄存器单元把信号(数据)加载到该管脚中去;对于芯片的输出管脚,也可以通过与之相连的边界扫描寄存器“捕获”(CAPTURE)该管脚上的输出信号。在正常的运行状态下,这些边界扫描寄存器对芯片来说是透明的,所以正常的运行不会受到任何影响。这样,边界扫描寄存器提供了一个便捷的方式用以观测和控制所需要调试的芯片。另外,芯片输入/输出管脚上的边界扫描(移位)寄存器单元可以相互连接起来,在芯片的周围形成一个边界扫描链(Boundary⁃Scan Chain)。一般的芯片都会提供几条独立的边界扫描链,用来实现完整的测试功能。边界扫描链可以串行的输入和输出,通过相应的时钟信号和控制信号,就可以方便地观察和控制处在调试状态下的芯片。在IEEE 1149.1标准中,寄存器被分为两大类:数据寄存器(Data Register,DR)和指令寄存器(Instruction Register,IR)。边界扫描链是一种重要的数据寄存器,用来实现对芯片的输入/输出的观察和控制。而指令寄存器用来实现对数据寄存器的控制,例如:在芯片提供的所有边界扫描链中,通过指令寄存器选择一条指定的边界扫描链作为当前的目标扫描链即访问对象。

3 异构双核SoC调试环境设计方案

本文设计的调试环境的目标平台为某自主异构双核SoC,该SoC由一个ARM核与一个DSP核组成。为了节约片上资源,将SoC的ARM核和DSP核中符合IEEE 1149.1标准的JTAG控制器用菊花链的方式连接起来,通过一个JTAG接口进行控制。

为了对这一设计进行支持,ARM核与DSP核的JTAG控制器都支持Bypass指令,通过Bypass指令,可以将Bypass寄存器连接到数据移入接口TDI和数据移出接口TDO之间。在某个处理器内核不需要进行任何测试的时候,将Bypass寄存器连接在TDI和TDO之间,在TDI和TDO之间提供一条长度最短的串行路径。这样允许测试数据快速地通过该处理器内核送到处理器其他内核上去。

目标平台设计了自主的调试协议,无法使用现有的任何一种软件开发环境进行软件的开发和调试;因此,迫切需要针对目标平台的特点和调试协议,设计并实现与目标平台配套的软件调试环境。

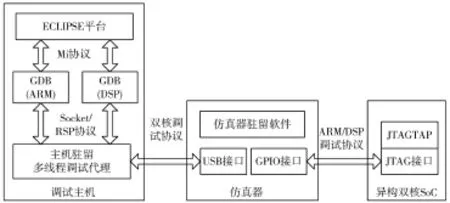

本文针对异构双核处理器结构,结合JTAG标准及菊花链连接方式、调试环境设计技术以及多线程技术,提出了一种调试环境设计方案。调试环境交互界面基于ECLIPSE平台,主要功能是提供友好的开发调试界面,接收用户调试命令输入,并显示调试结果,如目标机寄存器内容、内存内容、堆栈内容及断点信息等;采用GNU开源组织发布的支持多种目标平台的程序调试工具GDB作为调试器,ECLIPSE平台同时集成针对ARM 的GDB与针对DSP的GDB,ECLIPSE平台与GDB通过标准的Mi协议通信;调试主机驻留惟一的调试代理软件,调试代理通过两个线程采用两个端口分别与两个调试器建立连接,利用信号量解决通过单一JTAG接口访问双核SoC的互斥问题;调试代理利用调试主机的USB接口和仿真器进行通信。仿真器驻留异构双核SoC调试协议解析程序,该程序作为宿主机调试代理和被调试程序之间的媒介存在。

用户通过ECLIPSE平台输入调试命令,ECLIPSE平台根据当前处于活动状态的工程,区分输入命令的目标平台,将命令转换为若干Mi协议指令,发送给相应GDB,GDB将Mi协议指令转换为若干远程串行协议(RSP)指令,通过Socket连接发送给调试代理,调试代理根据接收到指令的线程区分指令的目标内核,将指令添加目标内核信息,封装成为异构双核调试协议指令,通过USB接口发送给仿真器软件;仿真器软件接收异构双核调试指令,根据指令中的目标内核信息,区分指令对应的内核,将指令解析为ARM或DSP单个内核的调试指令DSP或ARM内核的Bypass指令,按照JTAG状态机的时序要求,通过GPIO口将解析后的指令数据扫描到目标平台中,同时以移位方式获取返回结果;最后仿真器将调试结果通过USB接口发送给调试主机,经ECLIPSE解析后以图形方式呈现给用户。整个远程调试系统结构如图2所示。

图2 面向异构双核SoC的远程调试系统结构图

目前,GDB已经提供了对ARM和DSP指令集的支持,只需下载GDB源码,使用相应编译选项分别进行编译,即可生成针对目标平台的调试器。因此,本方案的关键技术是调试代理软件的设计和仿真器软硬件的设计。

4 调试代理软件设计

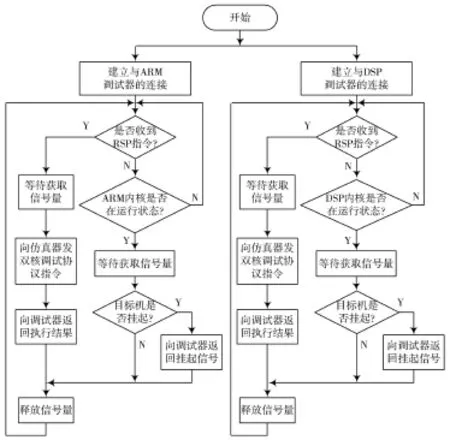

根据异构双核SoC调试环境设计方案,调试代理启动两个线程,使用两个端口分别建立与面向ARM和DSP的GDB的Socket连接。其中一个连接接收到完整的RSP调试指令后,需获取全局信号量,以避免与另一个内核的调试相冲突;获取到全局信号量后,通过USB接口向仿真器发送双核调试协议指令,等待仿真器软件返回执行结果;接收到执行结果后,将结果封装为RSP数据包,通过Socket连接返回给相应的GDB;最后释放全局信号量,一条RSP指令执行完毕,等待接收下一条GDB发送来的RSP指令。

调试代理软件通过内部变量记录两个内核的状态(挂起和运行)。如果一个连接没有接收到RSP指令,还应判断相应内核是否处于运行状态,如果相应内核处于运行状态,则需获取全局信号量,通过USB接口向仿真器发送内核状态查询指令,如果该内核已挂起,调试代理主动向GDB发送内核已挂起信号,最后释放全局信号量。其执行流程如图3所示。

5 仿真器设计

5.1硬件设计

硬件电路采用AT91SAM7X512作为仿真器控制芯片,外接USB接口。控制芯片引出5个GPIO引脚,分别对应IEEE 1149.1标准中的TDI,TDO,TMS,TCK,RST五个接口信号,通过缓冲处理芯片HC244SJ与目标平台的标准JTAG接口连接。为了能够实时观察调试过程中仿真器与目标平台之间的通信过程,控制芯片外接3个LED指示灯,分别与TDI,TDO及RST接口对应的GPIO引脚串联,只要JTAG接口有信号传输,对应的LED灯就会闪烁,起到指示作用。

图3 调试代理的执行流程图

调试主机上的调试代理与仿真器之间的通信是由连接于主控制芯片的USB接口来完成的,仿真器软件经烧写后存储在FLASH芯片中。为了提高仿真器的调试速度,仿真器上电后主控制芯片通过已经烧写在FLASH中的BootLoader将仿真器软件搬移到SRAM中运行。

图4 仿真器的硬件设计

5.2软件设计

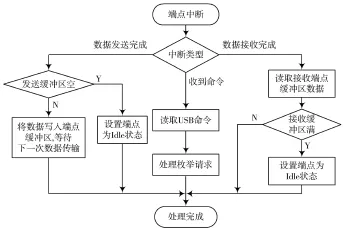

仿真器内部的嵌入式软件的执行流程如图5所示。当调试主机通过仿真器与目标平台连接后,仿真器开始通过端点中断进行设备的枚举过程,图6为端点中断处理流程。枚举完成后,仿真器作为从设备通过USB接口与调试代理进行通信,接收并执行双核调试协议指令。调试代理先发送2个字节的指令长度,然后发送指令的内容。仿真器通过端点中断接收到指令长度后开始等待接收此长度的指令内容。接收完毕后对指令进行解析,识别指令的目标处理器内核,从而选择进入针对ARM或DSP的处理函数,将双核调试协议指令转化为ARM或DSP内核调试指令,与另一内核的Bypass指令进行组合,通过TDI引脚按照TAP状态机的时序要求移入内核执行。内核调试指令执行完成后,仿真器将从TDO引脚移出的处理结果返回给调试代理。调试代理接收到执行结果后开始发送下一条调试指令。

图5 仿真器软件流程图

图6 仿真器端点中断处理流程

6 实验验证

将仿真器与调试主机及目标平台连接,同时对ARM和DSP内核进行调试,实验结果显示,调试环境能够实现设置断点、单步、观察变量等调试功能,下载程序到目标平台的速度为50 KB/s,具有较高的调试性能。

7 结 语

本文提出了一种面向某自主异构双核SoC调试环境的设计方案,解决了目标平台缺乏配套软件调试手段的实际问题。方案全部采用自主研发的软硬件或开源软件,具有功能完备、性能良好、安全可控等优点。本方案能够集成GNU的GCC编译器,结合Eclipse平台自身的功能,即可构成一个图形化的集成软件开发环境,实现一体化的工程管理、编译链接和远程调试功能,对其他自主多核处理器软件开发环境的设计具有一定的参考价值。

参考文献

[1]盛建忠,王胜,张庆文,等.GDB RSP协议与USB通信在嵌入式调试系统中的应用[J].电子与封装,2013(3):43⁃48.

[2]高扬.USB接口无线仿真器:硬件模块设计[J].电子测试,2015 (2):6⁃9.

[3]Joint Test Action Group.IEEE Std 1149.1⁃2001 IEEE standard test access port and boundary⁃scan architecture[S].USA:Insti⁃tute of Electrical and Electronics Engineers,2001.

[4]周乐,黄光红,陆俊峰,等.一种基于网口的DSP嵌入式仿真器的设计[J].中国集成电路,2012(4):19⁃22.

[5]王爽,康慕宁.基于Eclipse平台的嵌入式远程调试软件实现[J].微处理机,2014(3):56⁃59.

[6]田丹,李运喜,胡宁,等.基于Eclipse的嵌入式软件交叉调试[J].现代电子技术,2015,38(6):86⁃89.

[7]殷绍剑,雷航,詹瑾瑜,等.嵌入式远程调试原理研究与实现[J].计算机应用与软件,2014,31(6):240⁃243.

[8]鲍华,余锋林,黄光红,等.基于多DSP系统的交叉调试系统的设计和实现[J].中国集成电路,2013,22(4):79⁃83.

[9]黄光红,刘冠男.可配置多核处理器的调试器模块化分层设计[J].单片机与嵌入式系统应用,2014(7):13⁃15.

[10]范涛,刘高辉,叶笑春,等.SPARC平台模拟器源码级调试系统的研究与实现[J].计算机工程与应用,2013,49(4):65⁃70.

袁春如(1983—),女,硕士,工程师。主要研究方向为嵌入式系统、软件工程。

贺红卫(1970—),男,硕士,研究员。主要研究方向为软件工程、嵌入式系统。

中图分类号:TN911⁃34;TP311.5

文献标识码:A

文章编号:1004⁃373X(2016)03⁃0001⁃04

doi:10.16652/j.issn.1004⁃373x.2016.03.001

收稿日期:2015⁃07⁃22

基金项目:国家科技重大专项(2013ZX01020⁃004)

作者简介:王品(1984—),男,吉林松原人,硕士,工程师。主要研究方向为嵌入式系统。

Research and design of software debugging environment for heterogeneous dual⁃core SoC

WANG Pin1,YUAN Chunru2,HE Hongwei1

(1.Academy of Chinese Weapon Science,Beijing 100089,China;2.Institute of the 706,Second Academy of China Aerospace Science and Industry Corporation,Beijing 100039,China)

Abstract:Based on analysis of the remote debugging principle of the embedded system,the debugging environment design scheme for a heterogeneous dual⁃core SoC is proposed,and the key technologies of software&hardware design for the emulator and the debugging agent software design are discussed.The debugging environment can conduct online programming and debug⁃ging for the target platform,which can solve the practical problem that the independent dual⁃core SoC processor lacks of the de⁃bugging means for bundled software,and provide a strong support for target platform application and promotion.It has a refe⁃rence value for debugging environment design of other multi⁃core processors.

Keywords:heterogeneous dual⁃core SoC;emulator;remote debugging;USB;JTAG