基于ARM与FPGA的高速数据采集技术研究

高寰宇

摘 要:现场可编程门阵列(FPGA)与ARM(高级RISC微处理器)的结合能降低系统体积并实现强大的功能,在数据采集系统中得到越来越广泛的使用,FPGA与ARM之间的高速数据传输是系统实施的最具挑战性的问题之一。在本文中,我们使用FPGA来从前端获取海量数据,将其发送到ARM,同时ARM通过TCP/IP协议传输数据到远程计算机。本文主要介绍了FPGA和ARM之间高速传输方法的接口设计。该理论研究表明,这种方法最大传输速度可以达到50MB/s。

【关键词】现场可编程门阵列(FPGA) ARM 数据采集

在这个系统中,FPGA被应用于控制前端电子电路,并通过模数转换器将数据转换发送给ARM,同时,ARM可以发送数据到其他计算机来进行即时时间存储和处理。考虑到这个系统的最大数据采集率是8 MB/秒,因此从FPGA到ARM的数据发送的速度一定要超过8 MB/秒。

1 介绍

许多数据采集系统仍然基于CAMAC(计算机自动测量和控制)总线,其最大传输速率为3MB /秒,不能够满足高速数据传输的需要。

此外,也有大量的基于VME,FASTBUS,PCI或PXI的数据采集系统,虽然这些总线的速度可以满足要求,但是它们的协议非常复杂,并且ARM的I/O端口不能与那些协议兼容。此外,一些便携设备都基于如SPI,12C等的串行总线上,由于它的速度的限制,也不适合高速数据系统。因此,我们选择了高速并行通信方法,这不仅是因为它的简单的协议,还有低成本和高速的优势。

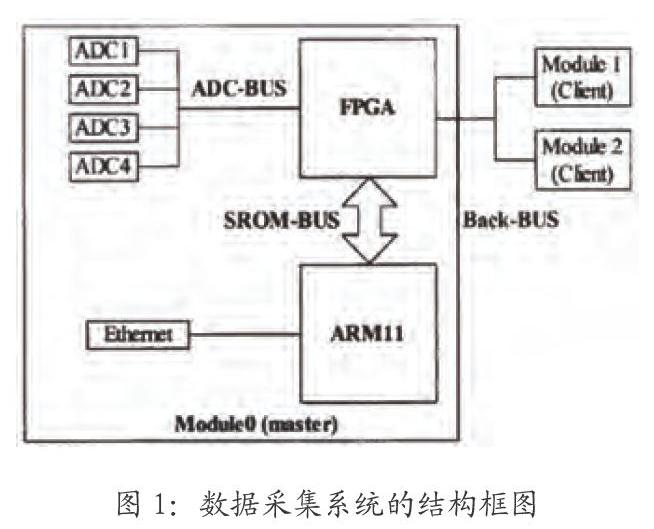

这种通信方法有两个设计要点:首先, FPGA设计为一个存储器与ARM的IO总线相连接;其次,FPGA是受控于SROM(静态只读存储器)控制器(SROMC)并集成在ARM中。理论上,该数据通信机制可以使FPGA和ARM之间传输速率高达50 MB / s,因此能够满足我们的数据采集系统的设计要求。FPGA可以独立或与相同的模块一起工作非常方便。该数据采集系统可以工作在主模式或客户端模式。该FPGA通过数模转换总线控制4个本地数模转换器,然后通过返回总线与其他数据采集模块通信。只有在主控模式下,数据采集模块需要通过SROM总线将数据传输到ARM。所有的数据通过以太网被发送到计算机进行处理。

2 FPGA与ARM之间的连接方式

FPGA和ARM之间的通信方法包括串行通信,定制的并行通信和高速并行通信。ARM和FPGA之间的连接包括一个16位的数据总线,一个16位的地址总线,读取控制信号线(OEN),写控制信号线(WEN)和中断信号线(IRO)。由于FIFO和SROMC的控制逻辑是不同的,因此,SROMC中的控制信号首先应在FPGA中处理后才能保证FIFO中的R&W数据是正确的。当FIFO由读时钟和写时钟控制时,SROMC是由读和写控制信号控制的,因此,我们需要将SROMC的读写控制信号转换为FIFO中的读写时钟。

另外,还要特别注意“rdclk”信号和“wrclk”信号的同步,以避免时序电路中系统时钟的矛盾问题。由于FPGA的系统时钟频率为50MHz,为了同步,“rdclk”信号和“wrclk”信号的周期应该高于40ns。然而,由于ARM的数据总线和地址总线是由FIFO和其他设备共享的,因此,在进行任何读操作和写操作之前,我们都必须检查CSN信号,否则,读或写逻辑将提供一个错误的结构,导致整个系统崩溃。

3 ARM中的驱动设计

事件信号的产生往往是随机的,为了解决系统不知道何时读取数据的问题,在其中实施了中断机制,以达到有效的结果。其工作机理如下:当事件的累积数(多事件模式)达到预设值时,FPGA被设置为通知ARM读取数据,该方法可以减少对ARM的负担,驱动器会处理该中断信号,并通知给程序来解决。中断处理器模块用于响应

硬件中断。如果数据达到数预设值时, FPGA将发送一个中断消息至ARM来读取数据,并将其写入到缓冲区中。此外,为了减少事件损失率和死亡时间(未检测到第二脉冲的时间),我们在驱动中应用了乒乓缓冲技术。当应用程序(APP)从两个缓冲器中的一个读取数据时,中断服务程序可以响应硬件中断,与此同时将数据写入另一个缓冲器。除此之外, ARM中的应用程序是基于多线程的,所以信号和数据可以在不同的线程中处理。信号处理线程能够响应驱动器中的数据读出要求,并将数据写入到APP缓冲器。同时该数据的处理线程可以分析信号处理线程获得的数据。同样,乒乓缓冲技术也应用在APP中,这样一来,它可以减少死区时间,并提高数据的吞吐量。

4 实验结果

该数据采集和传输系统的性能由下述两个实验结果验证:

实验一,采用P1010MIN模块来产生脉冲信号和门信号,脉冲信号直接被发送至数据采集系统,栅极信号先由MIN模块GG800处理,然后发送至系统。实验结果表明,最大数据传输速率约为2百万字节/秒,而事件生成的频率为250kHz;

实验二,将该数据采集系统应用于微波信号的采样处理。经检测器后,微波信号被转化为脉冲信号和门信号,最后得到的结果与通过PHILLIPS7164得到的结果是相同的。该系统的结构如图1所示。

5 总结

FPGA和RAM结合的高速传输方法成功地解决了数据采集系统中大量数据很难以高速发送的问题。第一个实验结果显示最大数据传输速率能够达到2百万字节/秒,以及事件生成的频率为250kHz。第二个微波信号采样显示这种方法能够满足数据收集系统的要求。然而,由于还存在一些微小的缺陷,整个系统的运行速度还达不到8 MB/秒。一旦系统的所有部分全部完成,系统就能够全速运行。

参考文献

[1]王亚庭.基于ARM与FPGA的高速数据采集技术研究[D].北京交通大学,2008.

[2]朱建光,余红英.基于ARM和FPGA的高速数据采集系统[J].伺服控制,2010,03:75-77.

[3]吴伟,郝建新,卢力.基于ARM和FPGA的高速高空数据采集系统的实现[J].现代电子技术,2009,01:126-128.

[4]张素萍,高照阳,张建芬.基于FPGA和ARM的高速多通道数据采集系统设计[J]. 自动化与仪器仪表,2015,08:110-113.

作者单位

中船重工第七二三研究所第四研究部 江苏省扬州市 225000