低功耗SARADC芯片设计与研究

刘 洋(天津维晟微科技有限公司,300457)

低功耗SARADC芯片设计与研究

刘 洋

(天津维晟微科技有限公司,300457)

摘要:本文设计和研究了一种低功耗8Bit SARADC结构,其采用了GF0.18um工艺设计,1.8V单电源电压,动态范围为1V,INL为0.5LSB,DNL为2LSB通过详细的电路原理分析和软件Cadence的仿真,并流片测试,性能达到设计初衷。

关键词:逐次逼近;比较器;预放大

近两年来,手持式设备的广泛应用,以及无线传感器在测控,仪表,工业控制等领域内作用的日渐突出,对数字模拟混合信号的芯片需求量越来越大,同时,对芯片的低功耗性能也提出了更高的要求,在绝大部分的数模混合芯片中,模数转换器(Analogto-Digital Converter,ADC)作为将真实世界中的模拟信号转换成系统可识别的数字信号的主要部件,也成为了整个芯片中降低功耗的热点。

目前,主要有pipelinde(流水线型),flash(闪存型),sigma-delta,sar(逐次逼近型)四种电路结构的ADC,其中SARADC具备中等速度,低功耗,高分辨率,高精度,尺寸小,等优点而被广泛应用于传感器信号处理,无线通讯,工业控制等领域。

1 SARADC系统原理

SARADC 主要由S/H(采样/保持电路),DAC(数模转换器),COMP(比较器模块),SAR(逐次逼近寄存器)模块以及其他模拟电路组成,其中,最核心的电路模块为DAC,COMP(比较器)以及SAR模块。

SARADC采用二进制搜索法原理,通过对信号的处理,使DAC的输出逐步逼近模拟信号Vin,工作过程为:模拟信号Vin通过S/H模块采样并保持,保持的信号进入COMP(比较器)的正端,此时,数字控制模块SAR通过对DAC的数字端的控制,将DAC的输出设定为1/2Vref, S/H电路的前端保持信号与DAC输出在比较器中进行比较,如果Vin>1/2Vref,则COMP输出1,则SARADC的最高位输出为1,如果Vin<1/2Vref,则COMP输出0,则SARADC最高位输出为0,最高位确定后,再确定SARADC输出的第二高位,根据最高位的比较输出结果,如果之前最高位输出为1,那数字控制模块将DAC的输出设定为3/4 Vref,输入信号Vin开始与3/4Vref进行比较,如果之前最高位输出为0,那数字控制模块将DAC的输出设定为1/4 Vref,输入信号Vin开始与1/4Vref进行比较,既可确认第二高位的值,以此类推,直至最低位确定为止。总结下来,就是对Vin与以二分法细分的Vref进行比较,从而得出量化值,每一次比较和确定SARADC输出数字码都需要一个时钟周期的时间,本文设计目标为8bitADC,即对每一个将要量化Vin值需要8个时钟周期的时间,再加上比较器清零和数字控制的时间,每个Vin值的量化总共需要9个时钟周期。

由原理可见,对SARADC的转换速度,转换精度,功耗等关键指标的影响,主要集中在DAC和COMP的建立时间和转换精度等性能上。

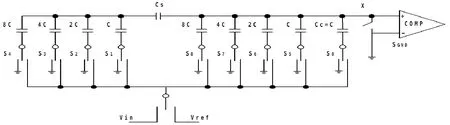

图1

2 DAC(数模转换器)设计

在SARADC中,通过COMP的比较结果,sar输出控制码对DAC进行控制,从而输出下次需要比较的电压,

DAC常用电阻阵列,电容阵列和电容电阻混合阵列结构来实现,但在CMOS工艺中,相同面积的电阻与电容相比较,电容由于远小于电阻的失调匹配而被经常运用在DAC中,而且,电容的充放电特性使其并不消耗电流,从而起到了降低功耗的作用,本文在综合各个阵列结构的优缺点后,本文选定电容阵列结构(电荷定标结构),具体电路采用了分段电容结构,其优势是采用了更少的电容,速度更快,功耗更小,版图面积也更小,在速度,功耗,面积与性能之间得到了很好的折中,最重要的是,通过电荷定标的结构,SARADC可以通过电容阵列直接对输入信号Vin进行采样保持,不需要另外的电路。电荷定标具体结构如下图1

工作过程如下:DAC的电容阵列先对Vin进行采样,开关~连接到地,~,连接Vin,闭合,Vin对电容阵列充电,整个电容阵列的电荷为=-16C·Vin;根据电容充放电,电荷保持不变的特性,采样后将~接地,断开,此时,=-256/271Vin;然后再分配阶段,接到Vref,闭合,增加128/271Vref,闭合,增加1/271Vref。所以的最终电压为

是分段电容的第i位,由上式可见,函数中的系数为,稍微小于1,所以,在比较器的设计中,对其精度的相关指标,要留有余量。

电容阵列中单位电容的匹配精度对SARADC的线性度有很大的影响,而影响匹配精度的主要由蚀刻误差和电容两个极板之间氧化层的梯度效应引起的,在本文中,采用了单位电容并联的形式来减轻蚀刻误差,通过电容阵列中心对称的版图布局来减小氧化层梯度效应,并增加dummy(冗余)单位电容,使电路电容蚀刻环境相同,dummy电容的两极极板同时接地或电源,在电路中没有实际的作用,只是在生产过程中,形成对有用单位电容的包围,使有用电容在蚀刻时保持一致的比例

3 COMP(比较器模块)设计

COMP是saradc中另一个关键电路模块,通过对DAC输出信号与Vcm的比较,得到数字信号1或0,sar模块根据比较结果,再控制DAC的数字控制字,所以,比较器的速度,精度等性能指标都会对saradc整体产生很大的影响。目前,常用的比较器分为两种,一种为运放型比较器,一种为LATCH比较器,其中运放型比较器精度高,但速度较慢,LATCH比较器速度很快,但精度不高,根据推导的结果,本文采用两种方式相结合的方式,先将被比较信号预放大,在进行比较。

比较精度由saradc的性能指标LSB决定,本文要求输入范围为1V,8Bit,按经验推算,比较器精度为0.5LSB,再考虑DAC输出推导式中Vx的系数,得出如下公式

由上式可知,比较器精度为1.8mV,而一般LATCH比较器失调电压在60mV左右,这要求在预放大电路的增益要在32dB以上,考虑其他因素,将预放大电路的增益定为40dB即100倍,同时,为了满足saradc的转换率达到20k,需要比较器的工作频率需达到5MHz,即在200ns所以,为了留出余度,比较器需在100ns内完成信号比较工作。

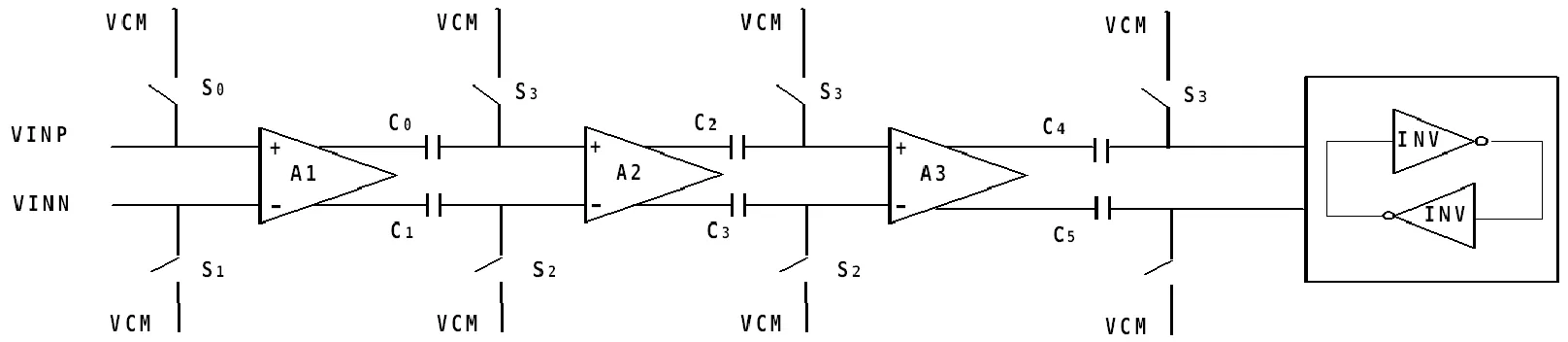

图2

3.1 比较器模块的失调校准

在生产加工过程中,由于电路元件的不匹配,会造成预防大电路的随机不可预测的直流电压失调,输入信号在小于offset的范围内,会导致比较器出现错误的比较结果,降低了比较器的精度,进而降低了整个saradc的精度,为了减少这种不可预测的影响,在级联预防大运放信号通路上采用了失调校准技术,通过电容可以充放电的特性,将失调电压存储在信号通路的电容上,再通过与输入叠加来减小消除失调,由于本文对级联预防大运放采用了输出失调存储技术。

讨论:椎体成形术治疗椎体骨质疏松性骨折或是肿瘤导致的脊柱疼痛中都获得显著镇痛效果,骨质疏松症导致患者疼痛脊柱不能活动又加重了骨质疏松二者形成恶性循环,所以解除疼痛和恢复脊柱的活动功能是治疗成败的关键1,认为此介入技术治疗椎体骨折是安全、有效,并且止痛可靠。骨水泥渗漏是PVP术的重要并发症,不过出现骨水泥渗漏的患者,都无明显的临床中症状2。本组105例患者术后未见严重并发症,101例患者疼痛显著缓解,显著缓解率达96.19%。

工作原理如下,在预防大电路对信号放大之前,闭合,使运放输入端短接到共模电平Vcm,此时,电容,上存储了经由运放Ai的失调电压,随后,预防大电路开始对信号放大,断开,电容,上存储的电荷反回去补偿抵消掉了运放的失调电压,本文的预防大电路为三个单极点运放级联,而每个运放的增益都不大,所以,每一级运放都采用这种失调电压补偿的方法。

3.2 比较器模块仿真(见下图2)

比较器输出为net020,其在时钟latch1的由低变高的瞬间输出比较结果,INP输入为由0.9V到1.1V的渐变电压信号,INN为1V共模电平,据观测,比较器在INP输入1.0002V时翻转,结论是比较器的失调电压在0.0002V以内,远小于SARADC系统要求0.5LSB,满足设计要求

4 回片测试结果

测试所需仪器

对信号发生器的需求:因为测试对象为8bit ADC ,所以信号源提供的信号精度必须要高于8bit,基于此要求的考虑,在本次回片测试中,本文选择了信号发生器:Agilent 81150,其可提供信噪比SNR为90dB,14bit精度的信号。

测试方法,由电压源提供1.8V电源电压,由信号发生器提供幅值为1V,频率为200k的正弦输入信号,通过逻辑分析仪对SARADC的输出点65536(2的16次方)个点进行采样记录,再将数据导入MATLAB进行fft的计算,得出以下结论

SINAD=41.3800

SNR=42.4852

SNR_ENOB=6.7645

THD=-47.6258

SFDR=49.4282

5 结论

本文采用了GF0.18 CMOS工艺,设计了一款8bit,5M采样率的低功耗SARADC,,电路中采用了分段电容DAC结构和带有预防大功能结构的比较器,功耗为96uW,经流片回片测试,实际有效位为6.7bit,完全符合设计初衷

参考文献

[1]李北建.10位50MHz流水线ADC的研究与设计.

[2]吴松昌.10比特50MSs流水线结构模数转换器设计.

Low power consumption SARADC chip design and research

Liu Yang

(Tianjin weishengwei Science and technology co. LTD,300457)

Abstract:This paper study and design a low-power 8 bit SARADC structure,the adopted GF0.18 um process design,single power supply voltage of 1.8 V,the dynamic range of 1 V,INL 0.5 LSB,DNL is 2 LSB Cadence through detailed analysis of the circuit principle and software of the simulation,test,and flow performance meet the design intent.

Keywords:the successive approximation comparator pre amplifier

作者简介

刘洋(1978.3-)汉,辽宁省凌海市,天津维晟微科技有限公司;中级工程师,硕士;研究方向;自动化。