一种基于共模负反馈的高性能运算放大器的设计*

范凯鑫,徐光辉,徐 勇,张开礼

(解放军理工大学 通信工程学院,江苏 南京 210007)

一种基于共模负反馈的高性能运算放大器的设计*

范凯鑫,徐光辉,徐勇,张开礼

(解放军理工大学 通信工程学院,江苏 南京 210007)

摘要:设计了一种基于CSMC 0.25 μm CMOS工艺的高性能全差分输入的折叠式共源共栅运算放大器电路。该电路由折叠式共源共栅运放模块、差分输出模块与共模负反馈模块组成,具有单位增益带宽高、稳定性好、开环增益大等优点。通过Cadance对此电路进行进一步的设计优化与仿真,表明该电路在5 V电源电压下,直流开环增益为115 dB、单位增益带宽为30 MHz、共模抑制比为185 dB、相位裕度为66°,达到了预期的设计目标。

关键词:折叠式共源共栅;共模负反馈;运算放大器;CMOS工艺

0引言

运算放大器是模拟集成电路的常用模块,大量具有不同复杂程度的运放被用来实现各种功能,从直流偏置的产生到高速放大或者滤波,运算放大器都扮演着重要的角色。随着CMOS工艺的不断发展,电源电压和晶体管的沟道长度减小,为运放的设计提出了更高的要求。运放的性能好坏将直接决定着整个电路系统的优劣。因此,高性能运放的设计是当前模拟集成电路与数模混合集成电路研究的热点。

增益与带宽是衡量运放性能的两个重要性能指标。一般来说低偏置电流、长沟道、多级放大运放电路可以实现高增益,然而高单位增益带宽电路又要求电路由高偏置电流、短沟道、单级运放电路来实现。由于共源共栅电路所具有的良好频率特性、高输出阻抗、主极点由负载电容决定等优点,可以在不降低增益带宽积的条件下提高直流增益,是两者的一个良好的折中。

1电路设计

1.1输入级的设计

本文运放输入级采用的是共源共栅运放,根据结构不同共源共栅运放可以分为折叠式共源共栅与套筒式共源共栅运放两种。套筒式共源共栅运放具有功耗低、频率特性好、速度高和带宽大等优点,然而套筒式共源共栅运放的输出摆幅较小,很难使输入与输出短路,不利于闭环使用。相比较折叠式共源共栅运放同样具有功耗低、频率特性好、速度高和带宽大等优点而且它的输出摆幅远大于套筒结构,可以闭环使用,具有更大的使用范围[1]。因此本文采用折叠共源共栅结构作为运放的输入级。

图1 折叠式共源共栅运放

运放的单位增益带宽是由负载电容决定,单位增益带宽为

其中Ccom为共模反馈电容。在共源共栅管N1、N2的源极存在较大的寄生电容,将引入一个次极点频率。由于N1、N2管的栅源电容一般大于源极其它的寄生电容,对于放大器次极点的频率决定起着主要的作用。因此可以减小共源共栅管的沟道长度或者增大静态工作电流,都可以增大次极点频率,有效地提高放大器的单位增益带宽。

1.2输出级的设计

为了能够实现高增益,本文采用了两级放大器结构,输出级采用共源级放大器(见图2),为了能够满足输出电压摆幅,采用了共源级放大电路[2]。其中,N1作为共源级输入管,P1作为电流源负载相比于电阻负载可以有效地提高输出摆幅和降低功耗,Vb提供偏置电压。运放的增益为:Av=gm1(ro1‖ro2),其中gm1为NMOS管N1的输入跨导,ro1与ro2分别为P1与N1的输出电阻。

图2 共源级放大器

1.3共模负反馈电路的设计

本文所设计的运放采用的是全差分运放,相比较于普通的单端运放,全差分运放有着较大的输出摆幅而且避免了镜像极点,达到了很高的闭环程度。然而,在高增益全差分放大器中,输出共模电平对于器件特性与适配相当敏感,而且难以通过差动反馈来达到稳定。若输出共模电平无法确定,便会使输出电平随之变化进而导致N1、N2、P4、P5进入线性区,使电路无法正常工作[3-4]。因此,我们需要增加共模反馈检测网络来检测两个输出端的共模电平,并有根据地调节放大器的偏差电流。关于共模负反馈的检测主要分为以下三个步骤:检测电路的输出共模电平;与参考电压进行比较;将误差送回放大器偏置网络。基于此本文所涉及的放大器共模检测反馈电路如图3所示。

图3 共模负反馈电路

如图3所示:该共模反馈电路的原理是将电路的两个输出端Vout1与Vout2的共模电平与参考电平Vref进行比较,然后通过N1、N2管的栅极将通过比较所产生的反馈电压传输到共源共栅全差分电路。从而调节直流偏置,进而稳定输出端的共模电平。

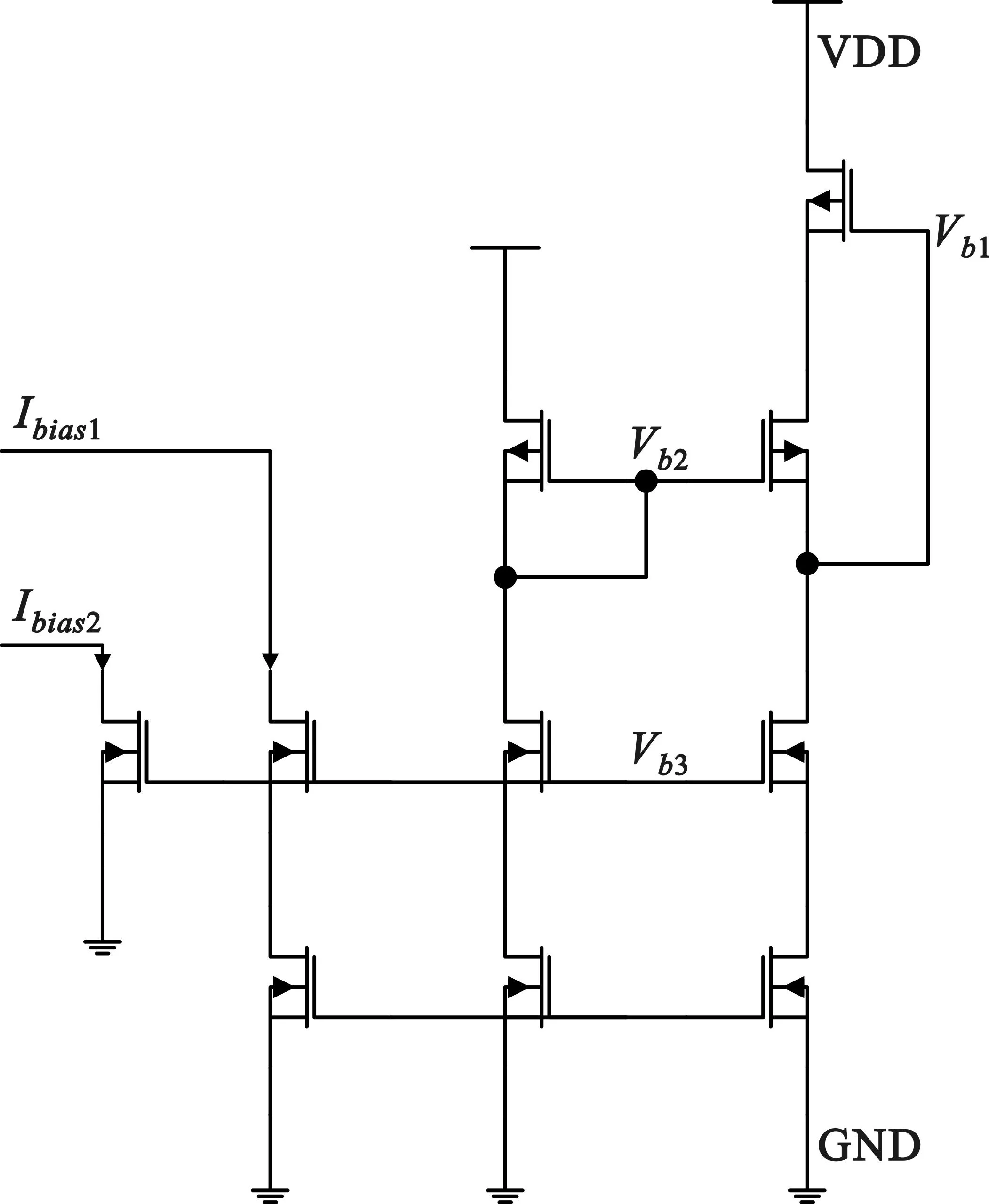

1.4运放偏置与整体电路设计

偏置电路设计如图4所示,其中Ibias1与Ibias2为5uA的基准电流源用来驱动偏置电路产生Vb1、Vb2、Vb3等偏置电压[5]。为了能够最大限度地降低误差,偏置电路晶体管的宽长比与折叠式共源共栅运放电路的宽长比一致。

图4 运放偏置电路

运放的整体电路如图5所示,其中运放的输入级为折叠式共源共栅运放,输出级采用了有源负载的共源放大器电路,最后输出端通过共模负反馈电路将电压差值反馈回放大器偏置从而稳定共模输出电压。其中,在共源输出级,我们采用了密勒补偿电容C1、C2使主极点向高频方向移动,非主极点向低频方向移动,实现了极点分离,确保了电路具有的相位裕度;电阻R1、R2用于将右半面零点向高频方向移动以降低零点对于环路的不良影响,从而实现电路的稳定。

图5 运放整体电路

2仿真结果与分析

本电路采用CSMC 0.25 μm工艺模型,通过Cadance Spectre软件对其进行原理图绘制与仿真。如图6所示为运放的增益和相位曲线图,仿真结果表明,该运放开环增益为115 dB,具有30 MHz带宽,相位裕度为66°,达到了设计要求。

图7所示为本文所设计运算放大器的共模增益仿真结果,其低频共模增益为110 dB。图8所示为运算放大器的共模抑制比仿真结果,其低频共模抑制比为185 dB。表1为运放性能对比。

图7 运放共模增益

图8 共模抑制比

参数文献[2]文献[4]本文直流增益100.1dB121.5dB115dB单位增益带宽10.1MHz12MHz30MHz共模抑制比84.1dB130.1dB185dB

3结语

本文设计了一种基于共模负反馈的高性能折叠式共源共栅全差分放大器。其中,折叠式共源共栅结构满足了高增益、宽带宽的要求;基于共源结构的输出级满足了高增益的要求;共模负反馈网络及RC补偿电路使电路具有稳定的共模电平。通过Cadance Spectre仿真软件对该放大器分别进行直流仿真、交流仿真及瞬态仿真,仿真结果表明该电路低频开环增益为115 dB、相位裕度为66°、共模抑制比为185 dB及电源电压抑制比,达到了设计要求。

参考文献:

[1]罗鹏,庞宇.一种低噪声高共模抑制比运算放大器的分析与设计[J].数字通信,2014,47(02):77-80.

LUO Peng,PANG Yu.Analysis and Design of A Low Noise High CMRR Operational Amplifer[J].Digital Communication,2014,47(02):77-80.

[2]王好德,王永顺,史琳等.高性能CMOS运算放大器的设计[J].微电子学,2011,41(01):19-22.

WANG Hao-de,WANG Yong-shun,SHI Lin,et al.Design of High Performance CMOS Operational Amplifier[J].Microelectronics,2011,41(01):19-22.

[3]尤志刚,邓立科,杨小军等.基于反馈技术的宽带低噪声放大器的设计[J].通信技术,2011,44(02):149-153.YOU Zhi-gang,DENG Li-ke,YANG Xiao-jun,et al.Design of Broadband LNA based on Feedback Technique[J].Communications Technology,2011,44(02):149-153.

[4]朱治鼎,彭晓宏,吕本强等.高性能折叠式共源共栅运算放大器的设计[J].微电子学,2012,42(02):146-149.

ZHU Zhi-ding,PENG Xiao-hong,LV Ben-qiang,et al.Design of High Performance Folded-Cascode Operational Amplifier[J].Microelectronics,2012,42(02): 146-149.

[5]刘敏侠,田泽,邵刚.高增益轨对轨运算放大器的设计实现[J].计算机技术与发展,2013,23(08):152-156.

LIU Min-xia,TIAN Ze,SHAO Gang.Design and Implementation of High Gain Rail-to-Rail Operational Amplifier[J].Computer Technology and Development,2013,23(80): 152-156.

A High-Performance Operational Amplifier based on CMFB Circuit

FAN Kai-xin,XU Guang-hui,XU Yong,ZHANG Kai-li

(College of Communications Engineering,PLA University of Science and Technology,Nanjing Jiangsu 210007,China)

Abstract:Based on CSMC 0.25 μm CMOS technology,a high-performance and full differential input operational amplifier with folded-cascode structure is designed.The amplifier circuit is composed of the folded-cascode operational mode,the differential output module and the CMFB module,and is of wide unity gain bandwidth,good stability and big open-loop gain.Further optimization and simulation of this circuit by Cadance indicate that this circuit,at 5V supply voltage,has a DC open-loop gain of 115 dB,a unity gain bandwidth of 30 MHz,a CMRR of 185 dB and a phase margin of 66°,thus satisfying the expected design target.

Key words:folded-cascode; CMFB; operational amplifier; CMOS process

doi:10.3969/j.issn.1002-0802.2016.02.023

* 收稿日期:2015-09-08;修回日期:2015-12-19Received date:2015-09-08;Revised date:2015-12-19

中图分类号:TN91

文献标志码:A

文章编号:1002-0802(2016)02-0243-04

作者简介:

范凯鑫(1990—),男,硕士研究生,主要研究方向为模数混合集成电路设计;

徐光辉(1973—),男,副教授,主要研究方向为SOC技术与嵌入式系统设计;

徐勇(1974—),男,副教授,主要研究方向为模数混合与射频集成电路设计;

张开礼(1989—),男,硕士研究生,主要研究方向为模数混合集成电路设计。