基于DDR2和FPGA的实时成像转置存储器设计

徐艺 黄静

摘 要:随着雷达实时成像处理器的发展,使得系统中的运算愈加复杂且数据量大,这就要求系统在进行快速运算的同时能对大量数据进行快速传输和存储。转置存储器是合成孔径雷达实时处理器和逆合成孔径雷达实时处理器的一个重要组成部分,它的效率直接决定了整个系统的性能。文中创新性地提出了一种将FPGA作为控制逻辑,DDR2作为外部缓存的转置存储器方案,该方案针对DDR2连续对同一bank的同一行进行读写操作时效率最高这一特点,设计了一种可以在雷达成像系统中通用的转置存储器,使用该存储器对4 096×512×32 b的数据在125 M时钟下做转置,只需80 ms,完全满足系统实时性的要求。

关键词:实时成像处理器;FPGA;转置存储器;DDR2

中图分类号:TP211 文献标识码:A 文章编号:2095-1302(2016)06-00-02

0 引 言

转置存储器(Corner Turning Memory,CTM)是合成孔径雷达实时处理器和逆合成孔径雷达实时处理器的一个重要组成部分,它的效率直接决定了整个系统的性能。在实时性要求不高的系统中,通常使用DSP作为成像处理的核心,配合DSP内建的SDRAM控制器,使用软件的方法,利用SDRAM对数据进行转置运算。但是采用DSP作为处理核心,DSP在功耗体积和抗辐射方面都不能满足当前对于SAR成像信号处理的实时性和微型化要求。也有同样基于DDR2的CMT在FPGA中的实现方法,此方法基于三页式思想来设计,其设计图如图1所示。将存储器按照实际需求分为A、B、C三页,在每页将距离压缩后每个距离向的数据按行的方式存储,而列的长度为方位向采样的一半,按行写入而按列读出。这样, 在写入A页的同时,可以读B、C页;写入B页的同时, 可以读A、C页;写入C页的同时,可以读A、B页。虽然用页的轮转工作实现了处理上的流水作业,在功能上可满足需求,但其并没有对DDR2的使用效率加以考虑,因为每次连续对DDR2进行跨行的读写操作会产生很长的延时,对DDR2的利用率降低,很难提高外部输入输出数据的时钟频率。

本设计充分考虑了DDR2的工作效率,即当对DDR2进行读写操作,连续对同一bank的同一行进行寻址时,DDR2对于连续的读或写命令间需要保持的延时最小,即对DDR2来说,进行此种操作的工作效率最高。同时也考虑到雷达实时成像系统所处理的数据大小是变化的,且方位向点数和距离向点数都是2的n次幂,所以可以利用数据大小的特点把转置存储器设计为通用的,将处理的方位向点数和距离向点数设计为输入,并对分块矩阵进行转置来实现矩阵转置功能。

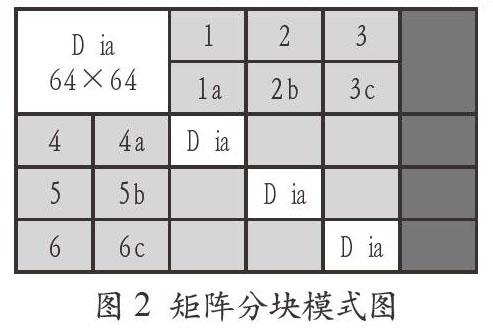

1 基于矩阵分块思想的设计方案

为了在读写数据时都是对同一bank的同一行进行操作,设计将输入矩阵数据按行写入DDR2,然后把该矩阵划分为大小相等的矩阵块,再按照其位置和不同的寻址规律把矩阵块划分为三类,对分类的矩阵块按规律一行一行从DDR2中读出并写入FPGA中的RAM资源内,对RAM内的数据进行地址跳变的读出,相当于对小的矩阵块做了转置处理,最后把转置后的数据存入同一片DDR2内的正确地址处。矩阵分块方法如图2所示。

(1)白色矩阵块表示对角模式的分块,对此种模式的矩阵块进行处理,首先要按行将数据读入RAM,然后再对RAM进行跳读,即对矩阵块进行转置处理,并把转置后的数据按行存入DDR2,存入位置为之前读出该矩阵块的位置。完成对一个矩阵块的处理后再进行下一矩阵块的转置处理。其间,除了对地址的连续操作外,还需要转到下一行,回到转置矩阵的最初位置,转入下一个矩阵模块等地址跳变操作。

(2)灰色矩阵块表示非对角模式的分块,对此种模式的矩阵块进行处理,首先要把上三角的矩阵块横向分成两个相等的部分,如图2所示的矩阵块1和矩阵块1a,再把下三角的矩阵块纵向分成两个相等的部分,如图2所示的矩阵块4和矩阵块4a。这是因为如果按照对角模式的处理方法,对数据进行转置处理后存入DDR2相应的转置位置会与仍停留在位置内的数据产生冲突。所以在该模式下读和写数据的顺序和位置为先按行连续读出模块1的数据,再按行连续读出模块4的数据,然后对RAM中的模块4数据进行跳读,转置处理后按行存入模块1所在的位置,最后对RAM中的模块1数据进行跳读,转置处理后按行存入模块4所在的位置。接下来其转入下一模块的顺序为先对(2,5)、(3,6)模块分别进行上述操作,再对(1a,4a)、(2b,5b)、(3c,6c)进行操作。其中矩阵块(3,6)表示MAX位置(标志对非对角分块每行或每列的最后一个矩阵块进行读写操作),矩阵块(3c,6c)表示LAST位置(标志对非对角分块偶数行或偶数列的最后一个矩阵块进行读写操作)。其间,除对地址的连续操作外,还需要转到下一行,操作到MAX位置后的地址跳变,操作到LAST位置后的地址跳变等对地址跳变不同规律的控制逻辑。

(3)斜纹的矩阵块表示非对称模式的分块,对此种模式的矩阵块进行处理,首先要按行将数据读入RAM,然后再对RAM进行跳读,即对矩阵块进行转置处理,并把转置后的数据按行存入DDR2,存入转置后该矩阵该块所对应的位置。完成对一个矩阵块的处理后再进行下一矩阵块的转置处理。在此种模式下,操作到每行的最后一个矩阵块为MAX位置。其间,除了对地址的连续操作外,还需要转到下一行,正确寻址转置后的存入地址,读写完一个矩阵块后如何转到下一个矩阵块,操作到MAX位置后的地址跳变操作。

按照这样的操作顺序是为了对DDR2的地址操作有规律可循,同时简化控制着不同规律的地址跳转的逻辑设计。转置完成后各模式分块的新位置如图3所示。

2 本设计的特点

在本设计中,每个矩阵块的大小是固定的,这样更有利于控制逻辑的编写。RAM的大小由FPGA中RAM缓冲资源的大小来确定,这样间接通过RAM来进行转置能保证对DDR2读写时的大部分操作都是对连续地址进行的,只有极少的操作需要连续对同一bank的不同行操作,所以相对于三页式而言极大地提高了对DDR2的利用率。设计的用于转置的RAM大小为64×64×32 b。

3 结 语

文中设计的通用矩阵转置模块建立在altera DDR2核可以稳定的对DDR2进行连续读写操作的基础之上,充分利用DDR2连续对同一行进行读写能够达到最大的带宽利用率这一特点,对需要做转置的数据先按照矩阵的形状一行一行连续存入DDR2,再对矩阵按照不同的跳址规律划分为三种矩阵块,对每一种矩阵块都完成转置变化后再存入DDR2内的对应位置,当用户需要时就可按行将转置完后的数据读出。测试中将4 096×512的数据在外部时钟100 M的条件下,需要80 ms,由于系统设计时采用了两组DDR2进行乒乓操作,所以当第三幅SAR图像数据到来时可以被继续处理,不会产生冲突。本方案能够满足雷达实时成像处理器的性能要求,达到对雷达信号进行实时成像处理的效果。

参考文献

[1]白海龙,全英汇,王虹现,等.基于DDR2SDRAM的SAR成像转置存储器的FPGA实现[J].现代电子技术,2008,31(1):48-50.

[2]保铮,邓文彪,杨军.ISAR成像处理中的一种运动补偿方法[J].电子学报,1992, 20(6): 1-6.

[3]卢光跃.逆合成孔径雷达成像技术的改进[D].西安:西安电子科技大学,1999.

[4]刘畅,牛晓丽,王岩飞.基于微处理器的SAR成像处理转置存储[J].现代雷达,2005,27(4):32-34.

[5] Hiroki Fujisawa,Masayuki Nakamura.1.8V 800Mb/s/pin DDR2 and 2.5V400Mb/s/pin DDRI Compatibly Designed 1-Gb SDRAM With Dual-ClockInpnt-Latch Scheme and Hybrid Multi-Oxide Output Buffer[Z]. IEEE,2005.

[6] Blagomir Donchev,Georgi Kuzmanov.External Memory Controller for Virtex IIpro[Z]. 2006.

[7] DDR_PHY_Interface_Specification_v2_1[EB/OL]. http://wenku.baidu.com/view/cc2ba76527d3240c8447ef5a.html