基于SystemC的可重构阵列处理器模型

蒋 林, 王杏军, 刘镇弢, 宋 辉

(西安邮电大学 电子工程学院, 陕西 西安 710121)

基于SystemC的可重构阵列处理器模型

蒋林, 王杏军, 刘镇弢, 宋辉

(西安邮电大学 电子工程学院, 陕西 西安 710121)

摘要:基于可重构技术以及SystemC的体系结构建模特点,构建一种基于SystemC的可重构阵列处理器模型。采用模块化的SystemC系统模型分别对指令传输模块、处理元模块以及邻接互连模块建模,构成32×32的可重构阵列处理器。通过指令传输模块实现局部和非局部两种单指令多数据模式的快速切换,使用邻接互连模块完成处理元间的通信。对建立的模型进行仿真验证,同时将高效视频编解码标准中视频算法映射到该模型上。仿真结果表明,该模型搭建正确,能够实现视频编解码标准中视频算法的并行化映射。

关键词:阵列处理器;可重构技术;SystemC;体系结构建模

视频处理技术[1]以数据并行和密集型运算为特征,已广泛应用于高清信号传输、视频聊天、视频会议等方面[2],其要求具有运算能力较高的处理器来应对复杂多变的网络应用环境[3-4]。可重构阵列处理器[5]具有强大的处理能力和优越的可扩展性等特点,已成为视频处理技术研究热点之一。

系统级建模工具SystemC[6-7],综合了硬件特有的并行性和软件设计的便捷性,可通过仿真来分析和优化可重构处理器结构。文献[8]提出了动态可重构系统的概念,并采用SystemC对其进行系统级建模,通过指定上下文切换时间和被选功能的激活时间来评估总线周期精确的性能,但是该系统采用上下文切换,只能改变不同功能的重构,不能实现部分可重构机制。一种动态可重构协处理器(DynamicllyReconfigurableCo-processors,DRC)结构[9],解决了文献[8]中缺陷,可以支持部分可重构,可对不同可重构方案进行快速设计空间探索。基于SystemC的周期精确级数字信号处理器(DigitalSignalProcessing,DSP)的建模方法[10],改善了高级语言在模型精度方面的不足。但是上述方法都缺乏对数据并行和密集型等视频算法的适应性。

本文拟采用SystemC对可重构阵列处理器进行体系结构建模,该模型由1 024个同构、规则处理元组成,相邻处理元之间以邻接互连形式组成32×32的处理器阵列,通过全局控制器实现对1 024个处理元的控制和管理。

1可重构阵列处理器系统结构

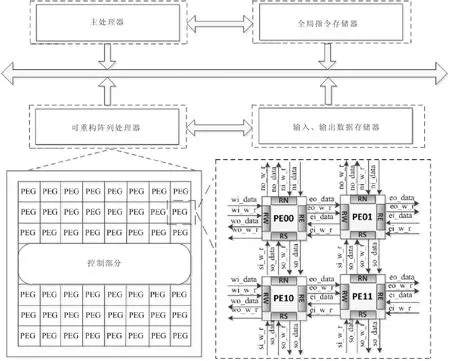

可重构阵列处理器系统由主处理器、接口控制器、全局指令存储器、输入/输出存储器和可重构阵列处理器组成,结构如图1所示。

图1 可重构阵列处理器系统结构

主处理器通过接口控制器负责控制调度可重构阵列处理器;全局指令存储器用于存储可重构阵列处理器工作的操作指令和调用指令;输入/输出存储器用于存放阵列处理器需要的输入和处理数据;可重构阵列处理器用于完成主处理器分配的任务,由指令传输网络、处理元(ProcessingElement,PE)和邻接互连网络组成。

1.1指令传输网络

指令传输网络是可重构阵列处理器的管理核心,当全局控制器的控制信号有效时,指令传输网络依照H型网络[11]将指令传输到相应的PE中,如图2所示,正方形为传输节点,到达的第1个节点命名为1,第2个节点有两个,分别命名为2-1和2-2,其他节点的命名方式与此类似,每个传输节点的终点为PE。

指令传输网络包括掩码检测单元和寻址单元,其中掩码检测单元接收到全局控制器发送的42bit寻址信息后,其格式如图3所示。掩码检测单元根据[31:30]两位信息检测出该指令是局部单指令多数据(SingleInstructionMultipleData,SIMD)模式和非局部SIMD模式的操作指令、调用指令。如果[31∶30]两位是10,表示该指令是局部SIMD模式的操作指令,将高10位掩码信息保存,并在下个周期和指令的寻址信息一起下发到选中的PE。否则高10位直接作为寻址信息。寻址单元负责对1 024个PE进行寻址,图4给出了节点1的寻址逻辑流程,通过对到达节点1的42bit信息的最高位进行检测,如果是1将低41bit信息发送到2-1;如果是0则将41bit信息发送到2-2。其他节点的处理过程与此类似,最终完成对1 024个PE的寻址。

图2 指令传输网络

图3 传输指令的格式

图4 节点的寻址逻辑流程

1.2处理元

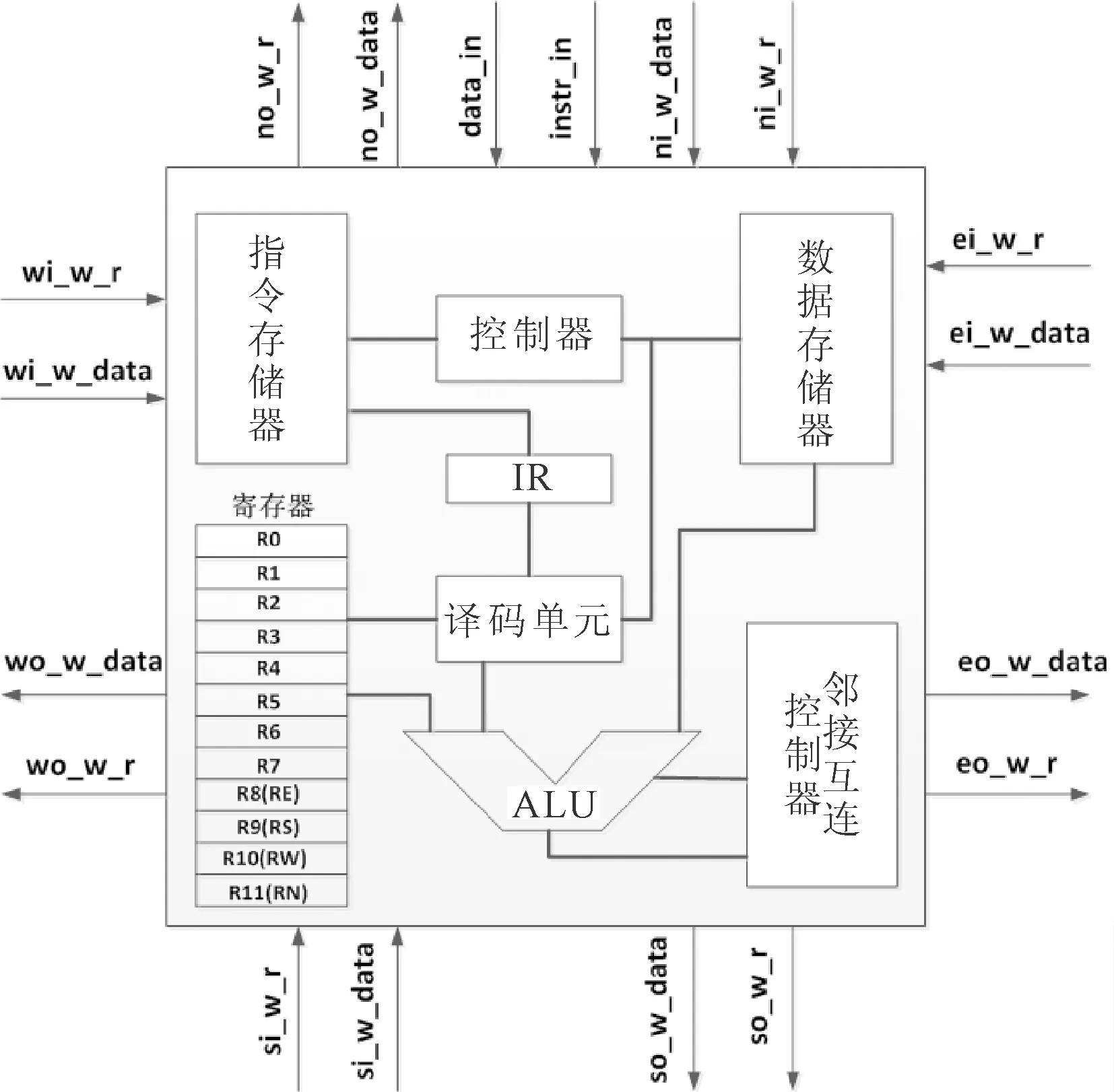

可重构阵列处理器可以支持1 024个PE。每个PE由算术逻辑单元(ArithmeticLogicUnit,ALU)、指令存储器、数据存储器、指令寄存器(InstructionRegister,IR)、译码单元、控制器、邻接互连控制器和寄存器文件组成,整体结构如图5所示。每个时钟周期,控制器根据当前的地址值和偏移地址,产生下一个周期的程序计数器(ProgramCounter,PC),根据该地址将指令存储中选定的指令送入IR。PE中有12个IR,其中R0、R1、R2、R3、R4、R5、R6、R7等8个寄存器为PE私有的,RE、RW、RS、RN等4个寄存器为东、西、南、北方向相邻PE的共享寄存器。

图5 处理元结构

1.3邻接互连网络

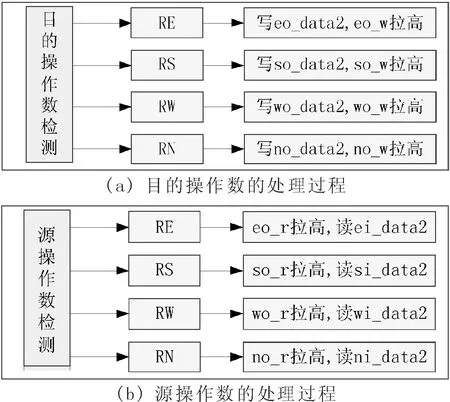

通过互连单元实现互连网络,其主要对指令地址码中码字是RE、RS、RW、RN的寄存器进行管理。邻接互连控制器的具体实现如图6所示。

图6 邻接互连控制模块功能

如图6(a)所示,地址码是目的操作数,表示本地PE要将运算结果写到相邻PE的寄存器中。以ADDRE,R2,R1这条指令为例来说明,当PE的译码单元检测到目的操作数为RE,邻接互连控制器把R1和R2相加的结果写到端口eo_data2,同时将写信号eo_w拉高。

如图6(b)所示,地址码是源操作数,表示本地PE要将相邻PE寄存器中的数据作为源操作数进行操作。以ADDR2,RE,R1这条指令为例来说明,当PE的译码单元检测到源操作数为RE,将读信号eo_r拉高。东边PE的邻接互连控制器检测到该信号有效时,把与本地PE共享寄存器中的数据传输给ei_data2。

2可重构阵列处理器建模

2.1建模系统设计

可重构阵列处理器模型系统如图7所示。用户界面通过汇编器将汇编程序解释成机器能够识别的二进制指令码,并将这些二进制指令码送往视频阵列处理器,同时用户界面通过进程间通信启用ModelSim10.1d仿真软件对可重构阵列处理器进行仿真,可重构阵列处理器的仿真结果反馈给用户界面以方便对该系统进行性能分析。

图7 可重构阵列处理器模型系统

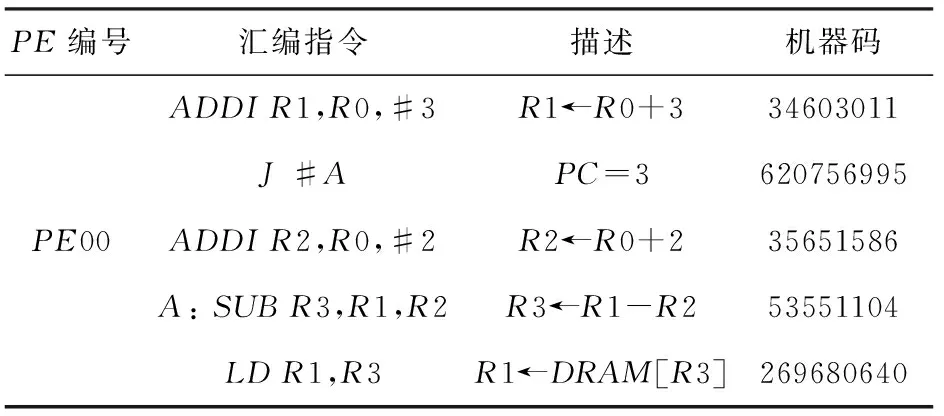

用户通过在Windows菜单中单击代表特定窗口的一项,就可以激活该窗口,点击图标B将汇编程序翻译成二进制的形式,点击图标M将调用Modelsim10.1d对设计的算法进行仿真,点击图标C选择需要调试的PE,点击图标D将二进制数转换成十进制形式,实际操作用户界面如图8所示。

图8 用户界面

2.2模型的建立

可重构阵列处理器模型分为指令传输、处理元和邻接互连等3个模块,通过实例化处理元模块和邻接互连模块连接构成1 024个阵列处理器,与指令传输模块连接构成可重构阵列处理器。

(1) 指令传输模块

指令传输模块包含控制信息分析、指令处理和指令更新等3个并行执行的进程和1个信息类。

控制信息分析进程根据寻址信息的最高位和掩码信息实现对1 024个PE的寻址过程以及采用何种下发指令的方式;指令处理进程是任务处理进程,向处理元模块下发该模式下的指令和指示指令有效的功能;指令更新进程等当前任务下发结束后,将设定新的工作模式,等待下一个任务的调用;信息类是存储可重构阵列的编码信息,并为实现任务放置、删除任务等任务提供接口。

(2) 处理元模块

处理元模块为实现基本计算单元,该模块包含1个信息类、1个数据结构体和1个ALU进程。

信息类存储运行时间,并检测PE是否在执行任务中;数据结构体记录所有的通用寄存器的值和PC指针等变量;ALU进程用来实现每条指令的操作。当全局控制信号无效时,PE内部的指令地址强制加1,否则,执行下发到指令存储中的配置指令。

(3) 邻接互连模块

邻接互连模块是实现相邻PE之间的互连,该模块包含目的处理和源处理两个并行执行的进程。目的处理进程将本地PE运算结果写入相邻PE的共享寄存器中,源处理进程实现从相邻PE共享寄存器中数据作为本地PE的源操作数。

3仿真结果及分析

可重构阵列处理器的模型搭建完成后,通过Modelsim10.1d得到仿真波形,设定时钟周期为20ns。

(1) 处理元基本功能的仿真测试结果

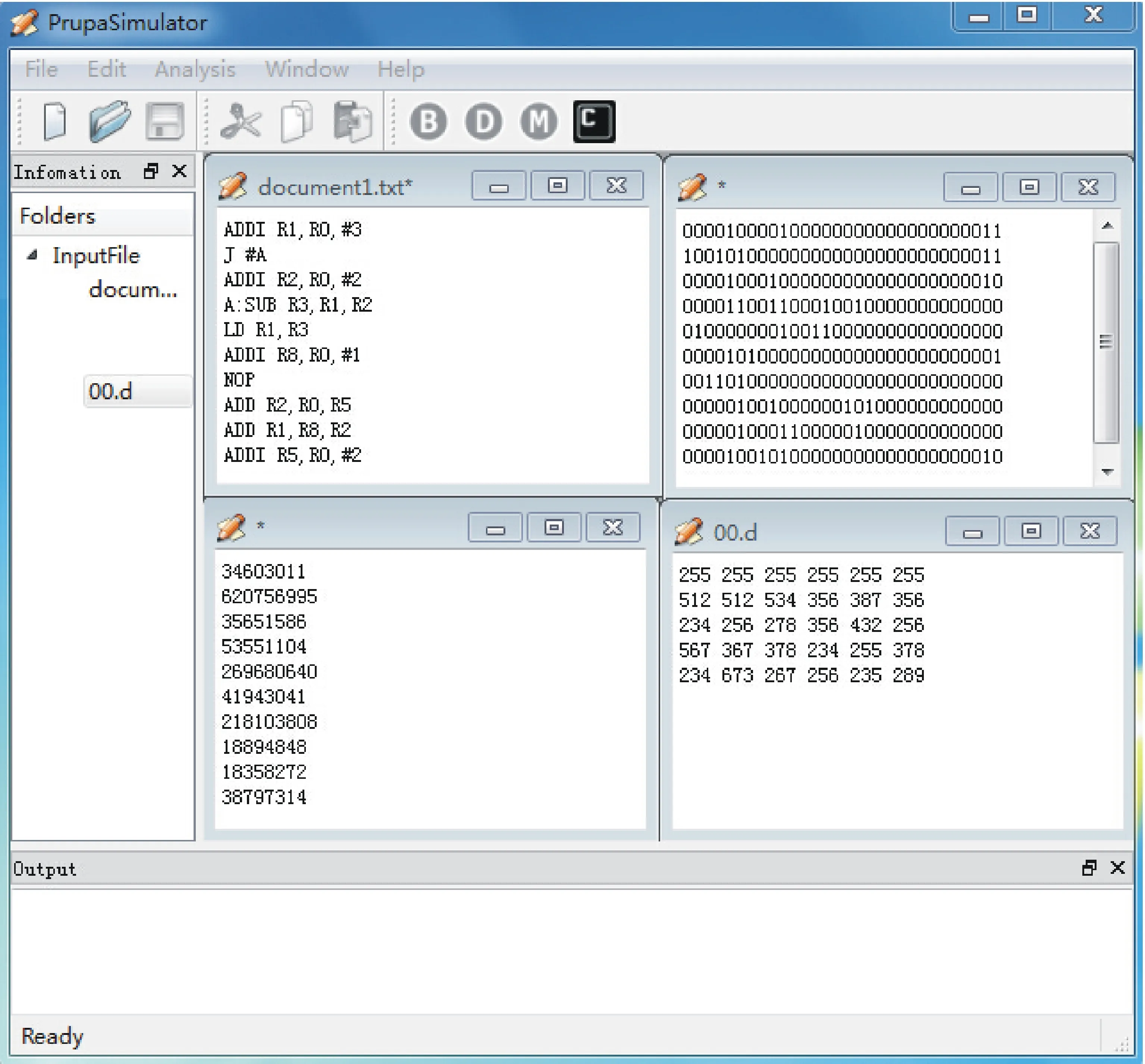

配置处理元PE00的指令如表1所示,测试处理元在执行基本指令、功能和时序的正确性。

表1 处理元的配置指令

由表1可知,4条指令共执行了7个时钟周期,第[0]条ADDI指令为1号寄存器,赋值为3;第[1]条指令J#A,通过助记符A代替立即数,该条指令的执行结果为PC=3,向指令寄存器中加载PC为3的指令,将第[2]条指令跳过,下个时钟周期直接执行第[3]条指令,在80ns时PC被更新为3,说明所构建的模型可以正确执行跳转指令;第[3]指令为SUBR3,R1,R2,即3=3-0;第[4]条指令为LDR1,R3,此条指令将地址寄存器R3中的值作为数据存储器地址,地址3所存储的值为5,将取出的值放到R1中,即R1中的值为5,说明存储指令得到正确执行。

(2) 邻接互连功能的仿真测试结果

按表2所示的指令配置相应的处理元,测试模型中邻接互连的正确性。

表2 处理元的配置指令

PE00输入指令ADDIRE,R0,#1,此条指令是将寄存器R0的值与立即数1相加的结果写入到PE01的R5中。PE01的第[0]条指令是NOP,执行空操作,因为向相邻PE寄存器中读写数据都需要两个时钟周期,所以PE01插入NOP指令等待1拍,第[1]条指令ADDR2,R0,R5中R5的值就是PE00写入的值1,表明该互连写指令得到正确执行;第[2]条指令ADDR1,RE,R2是将寄存器R2中的值与PE02中寄存器R5中的值相加写入寄存器R1中,即R1中写入的是数值3,表明该互连读指令得到正确执行。

(3) 实现视频算法映射的仿真测试结果

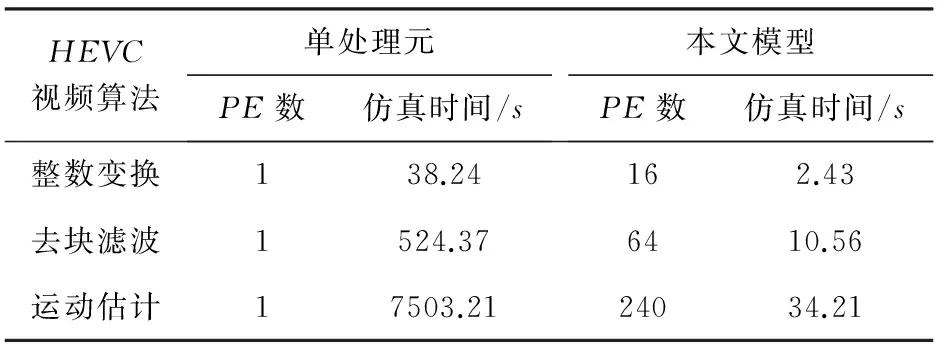

验证建立模型可以正确执行各种指令后,针对新一代高效视频编解码(HighEfficiencyVideoCoding,HEVC)标准的整数变换[12]、去块滤波[13]和运动估计[14]等算法,分别在单处理元和可重构阵列处理器模型上使用汇编程序实现其映射,并对仿真时间进行测试。

在Inteli3-2350 2.30GHz、2GRAM上处理1帧图像,表3是比较在单处理元和可重构阵列处理器模型上运行整数变换、帧间预测和去块滤波算法所使用的PE数和仿真时间。

表3 不同视频算法的仿真时间

由表3可以看出,基于SystemC的32×32规模的可重构阵列处理器模型能够实现HEVC视频算法的并行化映射,仿真时间得到提高。

4结语

构建了一种基于SystemC的32×32规模的可重构阵列处理器模型,该模型采用指令传输模块实现局部SIMD和非局部SIMD模式之间的切换;加入邻接互连模块完成PE间的通信,增加了PE的寄存器资源。对建立的模型进行仿真验证,同时将HEVC标准中整数变化、帧内预测和运动估计等视频算法分别映射到单处理元和该模型,结果表明,该模型搭建正确,能够实现HEVC视频算法的并行化映射,仿真时间得到提高。

参考文献

[1]陶文卿. 面向媒体处理的可重构阵列的结构设计与研究[D]. 上海: 上海交通大学, 2010:2-17.

[2]刘禹成. 面向密集数据并行计算的可重构线性阵列处理器架构的设计[D]. 上海:上海交通大学, 2011:2-5.

[3]霍俊彦,常义林,李明,等. 多视点视频编码的研究现状及其展望[J]. 通信学报, 2010, 31(5):113-121.DOI:10.3969/j.issn.1000-436X.2010.05.016.

[4]雷海军,杨辉,何业军. 高效率的多视点视频编码预测结构[J]. 电视技术, 2012, 36(18): 32-35.DOI:10.3969/j.issn.1002-8692.2012.18.016.

[5]李涛,刘应天,乔虹. 多态并行阵列机中处理单元的设计与实现[J]. 西安邮电大学学报, 2015, 20(3):21-28.DOI:10.13682/j.issn.2095-6533. 2015.03.003.

[6]FUMMIF,LOGHIM,PERBELLINIG,etal.SystemCco-simulationforcore-basedembeddedsystems[J].DesignAutomationforEmbeddedSystems, 2007, 11(2-3):141-166.DOI:10.1007/s10617-007-9006-7.

[7]SynopsysInc.SystemC2.3.1CoreSystemCLanguageandExamples[EB/OL].[2015-12-11].http://www.systemC.org.

[8]PELKONENA,MASSELOSK,CUPAKM.System-levelmodelingofdynamicallyreconfigurablehardwarewithSystemC[J].Parallel&DistributedProcessingSymposium.proceedings.international, 2003:174b.DOI:10.1109/IPDPS.2003.1213321.

[9]YANGQ,TIENSYRJAK,MASSELOSK.System-LevelModelingofDynamicallyReconfigurableCo-processors[C/OL]//FieldProgrammableLogicandApplication: 14thInternationalConference,Fpl2004,Leuven,Belgium,August30 -september1, 2004.Proceedings.Berlin:Springer, 2004:881-885[2015-10-20].http://dx.doi.org/10.1007/978-3-540-30117-2_93.

[10] 何卫强,杨靓,卢强. 基于SystemC的周期精确级DSP处理器建模[J].微电子学与计算机,2013,30(4): 107-110.

[11] 彭良睿, 李学明. 一种基于树型结构的P2P系统高维数据检索方法[J]. 计算机应用研究, 2015, 32(3): 842-845.DOI:10.3969/j.issn. 1001-3695.2015.03.046.

[12] 田小平, 田永召. 面向交互应用的HEVC编码性能分析[J]. 西安邮电大学学报, 2014, 19(3): 6-10.DOI:10.13682/j.issn.2095-6533. 2014.03.002.

[13]LEEYL,PARKHW.Loopfilteringandpost-filteringforlow-bit-ratesmovingpicturecoding[J].SignalProcessing:ImageCommunication, 2001, 16(9): 871-890.DOI:10.1016/S0923-5965(00)00048-5.

[14]YANC,ZHANGY,DAIF,etal.HighlyParallelFrameworkforHEVCMotionEstimationonMany-CorePlatform[C/OL]//2013DataCompressionConference.Snowbird,UT:IEEE, 2013:63-72[2015-10-20].http://dx.doi.org/10.1109/DCC.2013.14.

[责任编辑:祝剑]

ReconfigurableArrayProcessorModelingBasedonSystemC

JIANGLin,WANGXingjun,LIUZhentao,SONGHui

(SchoolofElectronicEngineering,Xi’anUniversityofPostsandTelecommunications,Xi’an710121,China)

Abstract:Based on the reconfigurable technology and the feature of SystemC architecture modeller, a reconfigurable array processor modelling based on SystemC is proposed. A model of reconfigurable array processor with 32×32 is built by building instruction transmission module, processing element module and adjacent interconnect module by using the modular SystemC system model design method. The model uses the instruction transmission module to achieve the fast switching of the local single instruction multiple data and the non-local single instruction multiple data mode, and then the adjacent interconnection module is used to complete the communication between the processing elements. Once the modeller is set up, simulation and verification are carried out, and the new generation video coding standard is mapped to the modeller. Simulation results show that the system modeller is correct and can achieve the parallel mapping of the new generation of efficient video codec standard video algorithm.

Keywords:array processor, reconfigurable technology, SystemC, architecture modeler

doi:10.13682/j.issn.2095-6533.2016.03.012

收稿日期:2015-12-11

基金项目:国家自然科学基金资助项目(61272120);陕西省自然科学基金资助项目(2015JM6326);陕西省科技统筹创新工程基金资助项目(2016KTZDGY02-04-02)

作者简介:蒋林(1970-),男,博士,教授,从事集成电路设计方向的研究。E-mail: jl@xupt.edu.cn 王杏军(1989-),女,硕士研究生,研究方向为微电子学与固体电子学。E-mail: 654221611@qq.com

中图分类号:TP391

文献标识码:A

文章编号:2095-6533(2016)03-0073-06