FPGA的验证平台及有效的SoC验证方法

张跃玲,张磊,汪健,王镇

(1.北方通用电子集团有限公司 微电子部,苏州 215163;2.63963部队)

张跃玲1,张磊2,汪健1,王镇1

(1.北方通用电子集团有限公司 微电子部,苏州 215163;2.63963部队)

摘要:设计了一种基于FPGA的验证平台及有效的SoC验证方法,介绍了此FPGA验证软硬件平台及软硬件协同验证架构,讨论和分析了利用FPGA软硬件协同系统验证SoC系统的过程和方法。利用此软硬件协同验证技术方法,验证了SoC系统、DSP指令、硬件IP等。实验证明,此FPGA验证平台能够验证SoC设计,提高了设计效率。

关键词:DSP;SoC系统;FPGA平台;验证技术

引言

随着集成电路技术的发展以及EDA 设计水平的迅速提高, 基于IP(Intellectual Property) 进行SoC(System on Chip)芯片设计的能力和技术得到了大大的提高。在一些应用中,需要处理的数据量不断增大,并且处理时间也要缩短,数据运算更加复杂,内嵌DSP核处理器的SoC技术能够缩短处理时间并能进行大数据量的处理,提高可靠性,缩小体积,降低功耗。因此本文研究一种基于DSP的SoC芯片的FPGA验证方法,并将整个系统包括DSP处理器、片上总线、ASIC、内存模块、I/O 外围设备及其他IP模块集成到一个芯片中。而在复杂的内嵌DSP核的SoC 芯片的系统设计中, 为了保证SoC芯片设计的正确性, 验证工作变得越来越重要, 也更加复杂。FPGA验证是复杂芯片和SoC芯片设计验证的一种有效手段,可以弥补软件模拟仿真的不足,减少验证时间,检验SoC的设计是否实现了设计规范确定的功能,从而提高SoC芯片流片成功率。

1基于DSP核控制的SoC系统

本文设计的SoC系统采用国内自主研发DSP核,主要包括: DSP处理器核、片上AXI总线、PWM、事件捕获器、看门狗控制、中断控制器、复位管理、存储模块、I/O以及其他外设(UART、CAN、SPI等)模块。这些模块与DSP核之间通过AXI总线连接,进行数据通信。AMBA AXI的总线协议具有高性能、支持高频传输、高速亚微型系统互连的特征,为主从结构,一切触发都由主设备发起。核间通信总线采用SoC系统中应用最多的AXI总线结构,比较灵活,可满足对带宽需求不同的各种IP。

基于DSP的SoC系统结构框图如图1所示。

图1 基于DSP的SoC系统结构框图

2SoC系统的FPGA验证平台

FPGA验证平台用于SoC芯片验证,可以对大规模SoC系统的设计进行快速准确的实时验证,根据不同SoC规模容量,采用不同的FPGA硬件资源,硬件平台建设也有所不同。由于FPGA具有静态可编程和在线动态重构特性,能够使硬件功能电路同软件程序一样方便修改,使得FPGA验证修改十分方便、实时性好,还可以缩短开发周期、降低开发成本。FPGA具有的这些特点使其成为通用的SoC功能验证的器件,为SoC的系统原型验证提供了一个非常合适的平台。目前FPGA已经从系统集成、系统存储、系统时钟和系统接口4个方面满足了SoC芯片验证的要求,为快速系统原型验证提供了一个非常合适的平台。本文的FPGA验证平台采用Xilinx Virtex-6 LX760器件,是建立在Xilinx Virtex6 FPGA板上的软硬件联合验证系统,并用ISE13.3进行综合和布局布线。另外,此FPGA硬件验证平台包括支持DSP程序下载的JTAG接口。

2.1FPGA硬件平台搭建

硬件平台搭建主要使用了两个Xilinx Virtex-6 LX760 FPGA器件,具有15.2M个逻辑门。Virtex-6 LX760面向高端应用,具有更多的时钟和存储资源,而且能够支持更快的速度。通过分析,所选择FPAG能够满足此SoC验证使用,为了实现通用性,该FPGA硬件验证平台采用了子板和母板相结合的方式。在母板上设置有通用的FPGA芯片、相应的PROM、系统全局时钟的选择和配置模块、系统复位逻辑、FPGA芯片下载接口、与子板连接的connector接口等模块。子板根据验证需求,配置了JTAG调试子板,以提供DSP仿真器连接的调试接口。另外还设计配置了验证EMIF访问外部存储设备通路的SRAM存储器子板。为了方便测试和验证EMIF接口功能,在这两类测试子板上,都设有关键信号的测试探测点,以方便测试一些基础的时钟、复位信号以及其他探测信号。

2.2FPGA软件环境搭建

在SoC 设计中,经常会使用一些硬IP 核(如PLL、SRAM、ADC、USB transceiver 等),而在采用FPGA验证技术验证ASIC及SoC设计的过程中,需要做ASIC设计原码的转换,所以首先需要对SoC进行修改,以适合FPGA的开发环境。如门控的处理,添加PLL对所需要的时钟进行适当的分/倍频,存储单元RAM、FIFO的替换,修改子模块配置,特殊单元的处理等。还要根据特定的硬件平台增加FPGA 相关时序Timing的约束和I/O引脚的指定约束,并搭建一个能够自动仿真和验证的环境。在FPGA验证过程中主要使用ISE13.3内置综合工具或专用综合工具对RTL进行编译、综合,生成网表。生成的网表可以生成bit文件,包括优化、适配、bit文件生成等。进行静态时序分析,检查是否满足预定的时钟频率要求,若不能满足,则重新进行综合编译优化。如果多次进行优化仍不能满足时序要求,则根据违反时序信息查找关键路径,对RTL设计代码进行修改优化。

FPGA验证软件除了需要上述提到的综合布局布线的软件环境ISE13.3外,还需要FPGA内部信号在线调试工具Chipscope,即时抓取一些内部逻辑信号,分析内部逻辑正确与否。在验证调试阶段,还需要DSP核下载调试软件CCS3.3,以编写控制处理器核DSP运行软件的测试程序。

2.3软硬件协同验证系统

FPGA验证SoC系统方法是软硬件协同仿真和验证,并搭建软硬件协同验证平台系统。实现的基础条件是能够满足工作要求的FPGA硬件平台,以及有力的设计描述及编译工具等软件环境。而基于DSP控制的SoC验证系统还需要DSP软件程序开发环境及下载通路等。

2.3.1FPGA软硬件协同验证架构

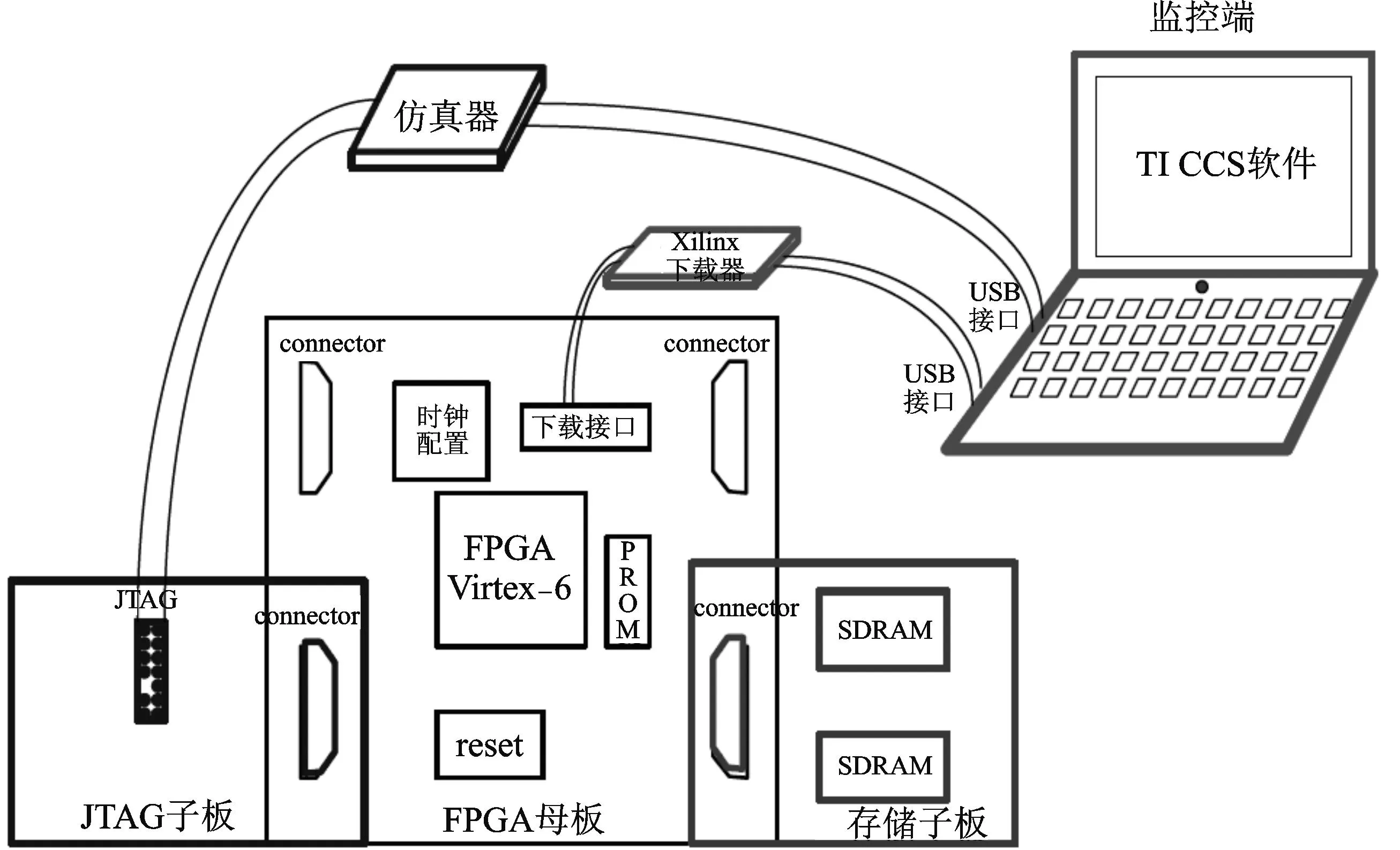

FPGA验证是为了实现和验证SoC芯片在实际硬件环境下的功能和运行工作情况。针对本文提出的基于DSP的SoC系统,搭建能够实现和验证其DSP程序指令及内部电路工作的软硬件协同验证系统平台。建立的FPGA软硬件协同验证系统的基本架构如图2所示。

其中包括FPGA原型验证需要的Xilinx Virtex-6芯片的FPGA验证母板、支持下载bit文件及验证调试过程中需要的Xilinx FPGA编程器及下载线、能够支持正确下载DSP激励测试程序的DSP-JTAG调试子板、支持DSP芯片的仿真器、安装有TI CCS软件和 ISE13.3,以软件及支持DSP芯片驱动的计算机。

图2 FPGA软硬件协同验证系统的基本架构

2.3.2验证过程

软硬件协同验证过程分以下几个步骤:

① 首先把要验证的SoC系统由ISE13.3自动综合及布局布线实现后生成相应的FPGA位流文件,经JTAG下载至构建的FPGA验证系统中的FPGA芯片或对应的PROM中。

② 通过微机CCS开发界面编写控制内部DSP核运行的程序,完成程序启动初始化、测试激励程序编译、开发验证IP及系统需要的程序。

③ 通过DSP仿真器以实时的方式进行软硬件协同验证过程中的管理控制,通过编写及测试程序的加载、运行、调试,实现对DSP核单步操作、连续运行等;通过设置正确中断服务程序、设置断点、观测DSP核内部寄存器及SoC配置寄存器值等分析DSP核运行及操作IP情况。

④ 通过不同的控制程序驱动运行相应功能IP模块及整个系统工作运行,验证IP功能及不同IP之间的交互和总线竞争。

在验证过程中可以根据IP功能及SoC系统特性使用示波器观测引脚信号,利用Chipscope软件抓取内部信号来判断逻辑关系及系统运行的准确性,验证DSP核、SoC系统及相应IP功能;验证系统各模块间的相互操作、片上系统内的数据相互流通功能;验证所有IP集合协同运行情况;验证整个系统的正确性。具体验证流程图可参见图3。

3SoC系统及IP模块功能验证

对SoC系统及内部IP功能模块进行验证,需要首先验证FPGA软件平台及硬件平台的正确性,才能在CCS环境下编写控制DSP的程序以验证SoC系统设计及各个功能模块的正确性。CCS编程器与FPGA硬件平台连接正确后,可通过下载编写控制DSP内核的程序,验证DSP运行正确性,并通过编写控制其他IP逻辑模块验证SoC系统内部交互及IP逻辑设计。其中主要进行了下面几种功能模块划分及其验证,通过验证功能模块也进一步验证了SoC系统及片上总线等设计的正确性。

3.1DSP核的验证

通过CCS开发界面对DSP内部寄存器进行读写操作并观测DSP内部寄存器的变化以实现验证DSP的功能,分别对DSP内部的Timer、GPIO、中断寄存器等进行读写及功能验证,并通过DSP控制其他各类寄存器以验证DSP核的正确性。

3.2EMIF及片上储存设备的验证

利用DSP能够正确读写片上存储器设备及支持各类读写操作,对片上存储设备进行验证。为了验证EMIF接口,在FPGA工程里对EMIF I/O口进行绑定约束使其与SRAM存储器子板进行正确的连接,通过DSP对EMIF空间寄存器的控制,使DSP能够正确地对连接在EMIF外的SRAM进行各类型的读写操作,可验证EMIF接口设计。

图3 基于DSP的SoC系统的FPGA验证流程图

本SoC系统中设计的EMFI接口模块可以连接4个外部存储空间CE0~CE3。通过ISE工具使用Xilinx Virtex-6芯片的FPGA IP core例化4个宽度为32位、深度为64位的SRAM,并且将它们连接到CE0~CE3空间接口上。在CCS中,初始化CE0~CE3空间接口,对各空间前16个地址写数据,之后对这些地址进行读操作。执行单步调试命令,可以成功读取CE0~CE3空间地址里面写入的数据。DSP核指令代码,首先配置全局控制寄存器,选择DSP提供的系统时钟,指令代码写全局控制寄存器:

*(int*)0x4000a000 = 0x00000000

配置CE0~CE3时钟寄存器和空间寄存器:

*(int*)0x4000a004=0x00000004;*(int*)0x4000a008=0x00000006;

*(int*)0x4000a00C=0x00000008;*(int*)0x4000a010=0x0000000a;

*(int*)0x4000a014=0xffffffe6;*(int*)0x4000a018=0x1091c226;

*(int*)0x4000a01c=0x30d5c846;*(int*)0x4000a020=0x2251c736;

对各空间前16个地址写数据,之后对这些地址进行读操作的DSP核指令代码:

for(i=0;i<16;i++){

*(int*)(0xC0060000+4*i) = (0x00000600+i);

*(int*)(0xD0060000+4*i) = (0x00000700+i);

*(int*)(0xE0060000+4*i) = (0x00000800+i);

*(int*)(0xF0060000+4*i) = (0x00000900+i);

}

for(i=0;i<16;i++)

{

temp_data = *(int*)(0xC0060000+4*i);

temp_data = *(int*)(0xD0060000+4*i);

temp_data = *(int*)(0xE0060000+4*i);

temp_data = *(int*)(0xF0060000+4*i);

}

运行DSP核指令代码,观察CE0~CE3寄存器的值,能够成功进行读写,验证了EMIF的正确性。

3.3事件捕获、看门狗等功能模块的验证

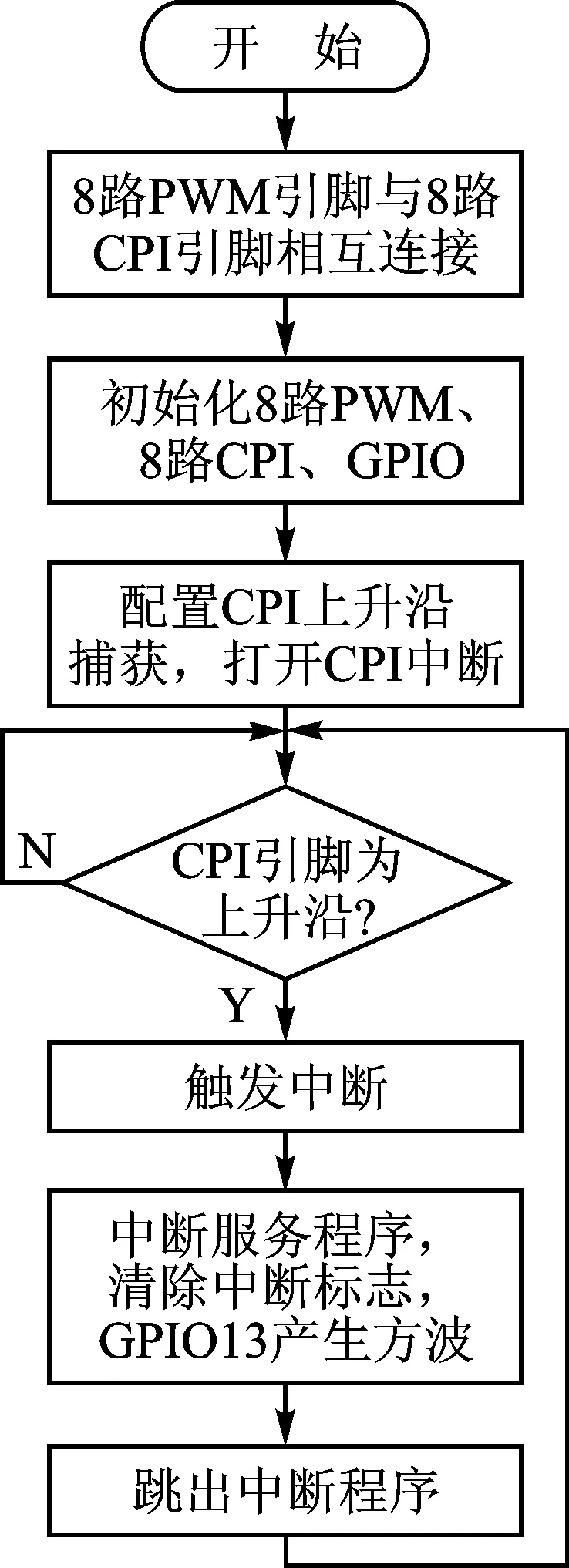

图4 验证CPI模块原理框图

通过DSP操作控制看门狗逻辑模块寄存器,看门狗能够正确运行,并能够正确影响复位模块以验证看门狗IP模块。通过DSP正确操作CPI等寄存器,使CPI模块产生中断并发送至DSP,DSP能够正确响应中断信号进行及时处理。为了方便验证CPI功能,此SoC验证CPI模块把PWM产生波输入到CPI模块,配置CPI捕获模式,当CPI模块输入有变化时,进行捕获产生中断。当发生中断时,CPI_INT为高电平,当DSP处理后会变为低电平信号。验证方法原理如图4所示。

在Chipscope中正确设置触发条件并通过FPGA编程器及JTAG传送到PC主机,可观察其逻辑波形的正确性。CPI中断事件图略——编者注,可以看出,CPI_INT6从高电平到低电平的转换,可说明DSP对CPI中断事件进行了处理,并正确响应外部中断。可验证正确设置CCS配置IP模块寄存器后,IP硬件模块能够正常运行。

3.4PWM、SPI、CAN、UART等外设模块

通过控制内部寄存器,能够产生正确的PWM波,分别在示波器及Chipscope上对一些信号进行采集及观测分析,验证其正确性,验证方法和验证CPI、EMIF相同。测试验证结果表明其功能正确。其中结合示波器测试PWM波,验证PWM设计的正确性,另外还使用相同方法验证SPI、CAN、UART等各IP功能的正确性。

结语

本文以一个DSP处理器控制的SoC芯片的开发与验证项目为例,介绍了关于FPGA的软硬件协同验证方法及过程,搭建FPGA验证硬件平台及软件平台环境, 并通过软硬件协同验证, 在线验证调试SoC系统中逻辑及功能设计, 并对每个功能模块进行了验证分析。通过CCS输入控制DSP程序进而控制SoC系统及内部IP模块,具有可观测性及实时性,实验结果表明,通过FPGA软硬件协同验证系统可以对目标SoC芯片进行功能验证及性能评估,缩短了基于SoC芯片的应用系统的开发时间,提高了流片成功率,整个验证平台及方法具有较高的可靠性。

编者注:本文为期刊缩略版,全文见本刊网站www.mesnet.com.cn。

参考文献

[1] 李辉,李平.一种嵌入式DSP 核的设计及FPGA验证[J].微电子学,2008,38(2):302-305.

[2] 王国章,须自明,刘战,等.SoC芯片验证技术的研究[J].微计算机信息,2007,23(23):132-133.

[3] 丰玉田,付宇卓,赵峰.大规模SoC 设计中的高效FPGA验证技术的研究与实现[J].电子技术应用,2006,32(2):110-113.

[4] 李建昌,赵博生,鲍胜荣.基于ARM7TDMI 的SoC 芯片的FPGA 验证平台设计[J].电子工程师,2004,30(9):6-9.

[5] 虞致国,魏敬和.基于FPGA的ARM SoC原型验证平台设计[J].电子与封装,2007,7(5):25-28.

[6] 刘朝,万培元,于忠臣.基于ARM7TDMI的SoC芯片的原型验证[J].数字技术与应用,2013(12):73-75.

张跃玲(设计师),主要从事数字集成电路设计。

(责任编辑:薛士然收修改稿日期:2015-10-09)

Zhang Yueling1,Zhang Lei2,Wang Jian1,Wang Zhen1

(1.R&D Center in Suzhou,Northern General Electronics Group Co., Ltd.,Suzhou 215163,China;2.63963 Troops)

Abstract:A FPGA verification platform is designed and an effective verification way of SoC is introduced.The basic scheme of the FPGA verification system is shown,and the software and hardware verification platform is introduced.The verification process and method are discussed.Due to the software and hardware co-verification technique,it can verify the SoC system design,the DSP statement,the hardware IP and etc.The experiment results show that the verification platform can verify the SoC design and improve the design efficiency.

Key words:DSP;SoC system;FPGA platform;verification technique

中图分类号:TN492

文献标识码:A