基于FPGA的雷达脉冲信号发生器的设计

伊志勇,刘 雨(哈尔滨工程大学 信息与通信工程学院,哈尔滨 150001)

基于FPGA的雷达脉冲信号发生器的设计

伊志勇,刘雨(哈尔滨工程大学 信息与通信工程学院,哈尔滨 150001)

摘要:随着电子对抗技术的发展,雷达的多样化对雷达信号分选设备的功能和性能提出了更高的要求,雷达脉冲信号发生器作为雷达系统的重要组成部分也同样面临着挑战.介绍了几种常见的雷达脉冲信号,并提出了一种基于FPGA的雷达多脉冲信号发生器设计方案.该脉冲发生器可以同时模拟多部非相参雷达脉冲信号,能够给分选设备提供更加真实的信号参数.采用FPGA技术不但能够大大缩短设计周期,便于硬件实现,而且系统的稳定性也比较高.本系统具有运行速度快、实现简单、体积小、成本低等优点,能够很好解决雷达多脉冲信号产生的技术难题.

关键词:信号分选;雷达脉冲信号发生器;现场可编程逻辑器件(FPGA)

作为数字系统实验及测试的信号来源,信号发生器[1]在数字系统中占有特别重要的地位.虽然市场上出现了许多性能较好的信号发生器,但是由于系统设计之间有很大的差别,往往需要自行设计满足工程需要的信号发生器[2].市面上常见的雷达脉冲发生器只能产生一部雷达脉冲信号,能够同时产生多部雷达信号的脉冲发生器价格却十分昂贵,因此,本文以雷达脉冲信号发生器为例,通过FPGA设计一部能够同时模拟多部雷达的复杂雷达脉冲信号发生器[3].该雷达脉冲产生器能够同时输出16部雷达视频信号,并且这16部雷达都是非相参的.本设计通过上位机与该信号发生器进行通信,能够产生参差、捷变频[2]等复杂雷达脉冲信号,并将这些脉冲信号进行复合输出,供雷达信号分选设备使用.

1雷达脉冲信号的种类

本次设计需要雷达脉冲发生器能够同时产生常规雷达、参差雷达、捷变频雷达、复杂雷达的脉冲信号,并将这些脉冲信号复合成一路复杂脉冲信号输出[4].

常规雷达的脉冲重复周期tPRI是固定的,如式(1)所示.

tPRIi=Mi=1,2,…,n

(1)

参差雷达的脉冲重复周期成周期tPRI性变化,式(2)中,k为参差雷达的重频周期数[1].即:

(2)

捷变频雷达的脉冲重复频率是不变的,但是捷变频雷达的载频(RF)是成周期性变化的,式(3)中,k为捷变频雷达的载频周期数[5].即:

(3)

2雷达脉冲信号发生器主要功能及性能指标

雷达脉冲信号发生器接收到上位机的指令后同时产生16部雷达脉冲信号,并将这些脉冲信号复合成一路复杂脉冲信号输出,供分选设备测试使用[4].其中脉冲宽度(PW)和脉冲重复频率(PRI)的输出形式为脉冲波形,信号带宽(BW)和载频(RF)以数据值的方式在脉宽高电平处输出.复杂雷达的每种参数可以设置8个,即四组参数的值为32个.

性能指标:

1) 雷达种类:复杂雷达、参差雷达、捷变频雷达、常规雷达;

2) 雷达参数:脉冲宽度(PW)、脉冲重复频率(PRI)、信号带宽(BW)、载频(RF);

3) 脉冲宽度的范围:1~500 μs;

4) 脉冲重复周期范围:1~300 ms;

5) 载频范围:1~20 GHz;

6) 带宽范围:10~1 000 MHz;

7) 雷达数量:复杂雷达1部,参差雷达1部,捷变频雷达2部,常规雷达12部.

3雷达脉冲信号发生器的设计与实现

3.1雷达脉冲信号发生器的总体设计

本次设计的雷达脉冲信号发生器的总体框图如图1所示,上位机通过串口与FPGA相连接,FPGA根据上位机给出的指令产生相应的脉冲波形与参数值,这些数据与信号分选设备相连接供信号分选设备调试使用.

图1 雷达脉冲信号发生器总体框图

3.2FPGA与上位机程序设计

本设计由FPGA来实现雷达脉冲信号发生器.FPGA采用ALTERA公司的Cyclone III芯片,型号为EP3C25E144C8.设计中使用了16个时钟晶振来产生多部非相参雷达脉冲信号,时钟周期为50 MHz.采用Verilog HDL语言来编写相应的程序.程序中,主要编写的模块有时钟分频模块、串口接收模块、单部雷达信号产生模块、总信号脉冲产生模块[5-7].

本设计中,上位机需要提供相应的参数命令给雷达脉冲发生器.在上位机界面的设计中,采用了Microsoft Visual C++ 2008软件来实现.界面中需要有16部雷达参数信息的输入选项,四种参数分别为雷达信号的脉冲宽度(PW)、脉冲重复频率(PRI)、信号带宽(BW)和载频(RF).该上位机有相应的串口识别功能,数据传送的波特率为9 600 B/s.

3.3上位机的实现

图2为配合雷达脉冲发生器的上位机界面,该上位机能够将每部雷达的参数指令传送到FPGA中,并产生需要的雷达脉冲波形.

图2 上位机界面

3.4雷达脉冲信号发生器的FPGA实现

信号发生器的FPGA程序模块包括串口模块、时钟分频模块、单部雷达信号产生模块、总信号脉冲产生模块.其中通过FPGA的时钟频率和串口数据传输的波特率能够设计出相应的时钟分频模块,此模块用于调整串口接收模块的时钟,使FPGA接收到的数据不丢失.串口接收模块的输出端连接每部雷达信号产生模块,单部雷达脉冲产生模块可以输出相应的单部雷达脉冲波形.

总脉冲产生模块可以将输入的16部雷达脉冲信号复合成一路复杂脉冲信号输出,输出的脉冲信号供雷达信号分选设备测试使用.

图3为FPGA的顶层模块图,图3中clk为时钟周期输入端,rx_data为接收的串行数据端,reset为程序复位键.bw[15..0]和fre[15..0]分别为带宽和载频的输出端,out为脉冲信号的输出端口.

图3 FPGA程序的顶层模块图

4成果验证及分析

为了验证设计方案的正确性,利用测试平台对本次硬件设计进行验证.

图4为Signal Tap II捕捉到的雷达脉冲信号,雷达的类型为参差雷达,该雷达信号的带宽(BW)和载频(RF)的参数值在脉宽高电平处输出.

图4 Signal Tap II捕捉的参差雷达脉冲信号

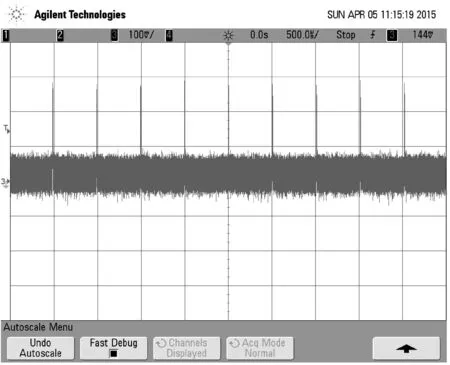

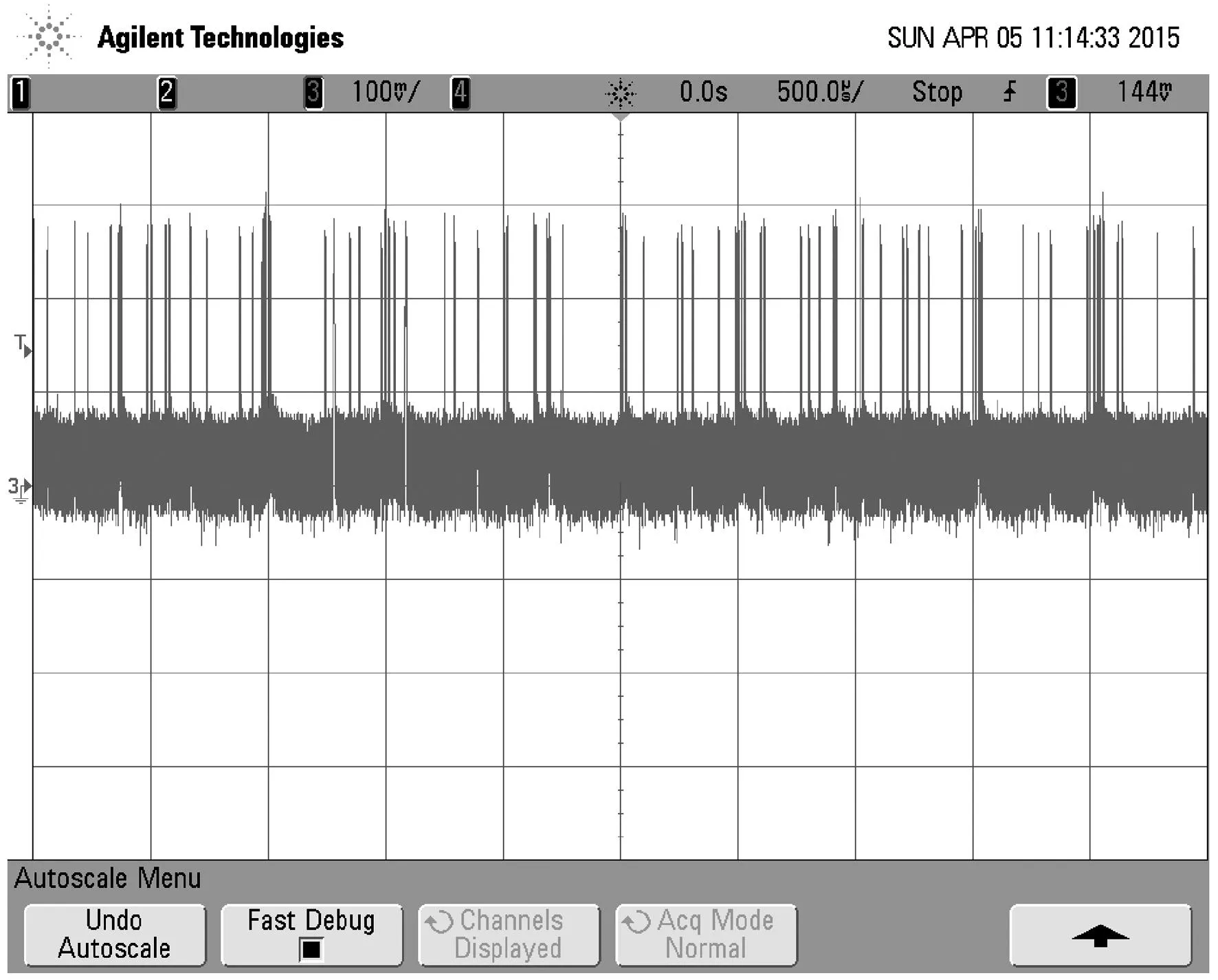

为了更加直观地验证方案,采用示波器测量输出的雷达脉冲波形.图5、6为示波器显示的脉冲信号波形.

图5为常规雷达脉冲波形,设置的参数为脉冲宽度为4 ,脉冲重复周期为504 .图6为多部雷达经过复合后的脉冲波形,雷达的数量为16部,雷达类型有复杂雷达、参差雷达、捷变频雷达和常规雷达.

此雷达脉冲发生器由FPGA来实现,成本比市面上大多数的多脉冲雷达发生器要低,并且易于实现,满足方案设计要求.

图5 常规雷达脉冲信号波形

图6 多部雷达脉冲信号波形

5结语

雷达信号发生器是雷达对抗领域中十分重要的一部分,为了测试雷达对抗系统的性能指标,往往需要设计一个满足工程需要的雷达脉冲发生器.传统的脉冲发生器只能够模拟单部雷达脉冲信号,能够同时模拟多部雷达信号的发生器价格则比较昂贵.本文针对传统雷达脉冲信号发生器的不足,采用基于FPGA的设计方法完成了非相参多雷达信号产生器.该雷达脉冲产生器能够同时输出16部雷达视频信号,且16部雷达信号都是非相参的.硬件测试验证了本次方案设计的正确性,为雷达分选设备提供了多样化的、可靠的、稳定的输入脉冲信号和相关数据信息.

参考文献:

[1]王娜. 基于FPGA的雷达脉冲信号模拟器设计[C]//北京: 中国仪器仪表学会, 2010.

[2]何彩分. 宽带捷变频频率合成器的研究与设计[D].成都: 电子科技大学, 2006.

[3]姜勤波, 马红光, 杨利锋. 一种新的雷达脉冲信号的非匹配检测算法[J]. 现代雷达, 2006, 11: 36-40.

[4]苗旺. 基于FPGA的雷达信号模拟器设计[D]. 北京: 北京理工大学, 2008.

[5]章欣. 基于FPGA的脉冲信号发生器设计[J]. 气象水文海洋仪器, 2014(2): 69-73.

[6]陈真,董丹丹.基于PMF的伪码捕获改进算法[J].哈尔滨商业大学学报:自然科学版,2015,31(4):477-480,485.

[7]于淼,朱丽伟,尹龙承.液晶光学相控阵激光雷达系统设计及边缘效应对其边瓣影响的研究[J].哈尔滨师范大学自然科学学报,2014,30(1):30-32.

Design of radar pulse signal generator based on FPGA

YI Zhi-yong,LIU Yu

(School of Information and Communication Engineering, Harbin Engineering University, Harbin 150001, China)

Abstract:With the rapid development of electronic countermeasures, many different kinds of radars put forward higher requirements on the functions and performance of radar signal sorting equipments, radar pulse signal generators which is an important part in radar system are also facing the same challenge at the same time.This paper introduced several common radar pulse signals and proposes a radar multi-pulse signal generator’s scheme based on FPGA.The multi-pulse signal generator could simulate several different kinds of radars at the same time and provide some more realistic signal parameters to radar signal sorting equipments.Using FPGA design can not only greatly shorten the design cycle and easily achieve the hardware design, but also the system’s stability was relatively high.This system had some advantages such as fast running speed,easy to implement,small size,low price. It can solve some technical problems of the radar pulse signal.

Key words:radar signal sorting;radar pulse signal generator;FPGA

中图分类号:TN972

文献标识码:A

文章编号:1672-0946(2016)01-0077-03

作者简介:伊志勇(1993-),男,硕士,研究方向:宽带信号的检测与识别.

基金项目:中央高校基本科研费专项基金(HEUCF140803).

收稿日期:2015-04-10.