基于NIOS的绝对光栅编解码系统设计*

刘 斌,陈 新,陈新度,杜 雪,蔡 念,吕元俊,王 晗

(广东工业大学 机电工程学院 广东省微纳加工技术与装备重点实验室 ,广州 510006)

基于NIOS的绝对光栅编解码系统设计*

刘斌,陈新,陈新度,杜雪,蔡念,吕元俊,王晗

(广东工业大学 机电工程学院 广东省微纳加工技术与装备重点实验室 ,广州 510006)

摘要:为了实现绝对光栅尺的快速解码,提高绝对光栅解码的实时性,建立了片上Nios绝对光栅编解码系统。首先,使用Verilog hdl语言编写了光栅编码采集的前端CCD和AD驱动。接着,将转换后的数据送到后端,以EP2C5T144C8为核心处理器的FPGA上的硬件加速模块,获得光栅条纹编码信息。然后,利用sopc技术,在实现Avalon数据接口ip核的基础上,搭建绝对光栅编码采集和处理平台,最后,在NIOS II IDE软件开发环境中,编写生成伪随机码绝对位置查询数据库和解码程序。实验结果表明:此编解码系统,在解码速度为2000帧/s条件下,精度为7μm,基本解决面阵做采集帧速不够的问题,并有较好的实时性,有效地降低了开发成本,为绝对光栅的开发提供了一个新的途径。

关键词:NIOS ;驱动采集;绝对光栅尺;解码

0引言

在现代数控自动加工行业中,精密电移平台的精确定位,多数采用光栅尺作为其位移位置反馈的核心部件,绝对光栅尺因在数控机床上电后得到的就是绝对位置,与采用增量光栅尺作为反馈部件的数控机床相比,简化了操作,提高了效率,因此应用前景更广[1]。

绝对光栅尺把高精度位移量反馈给数控系统,其关键是:光栅读数采集到绝对编码条纹信息,数据可靠,实时性高,采用面阵作为前端采集部件,因数据量庞大,帧速难于达到应用需求,而且还需专用数字信号处理芯片DSP完成大量的图像处理运算,实时性难于有效控制,成本也较高[2]。

因此本文提出基于Nios的绝对光栅编解码系统设计,具体如下:

(1)充分利用FPGA的并行处理的优势,完成前端光栅数据采集的CCD驱动和AD驱动;并采用硬件加速方法,使软件实现的一些算法用硬件逻辑实现,很好地解决了数据处理速度和存储空间分配的问题,简化了系统软件设计,提高了实时性。

(2)利用FPGA的Sopc系统自由配置所需的资源,灵活性大,使更新或修改更加便捷,缩短了开发周期,提高了集成度。

该设计集软硬开发于一体,降低了成本,同时实时性也达到了应用需求,为绝对光栅尺的开发提供了一个新的思路。

1系统设计原理

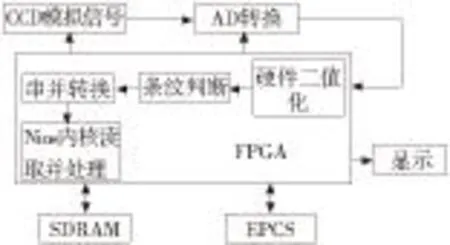

图1 系统原理框图

系统设计原理框图如图1所示,图中的线阵CCD模拟信号由FPGA驱动获得,线阵CCD从刻有绝对编码的玻璃基板上采集编码条纹,其中最小条纹宽度只有10μm,为进一步实现细分,我们采用20倍的光学放大系统进行放大,线阵CCD在FPGA驱动脉冲的驱动下,输出离散的像点模拟信号,再经过AD芯片的模数转换,在这里,AD驱动和CCD驱动采用同一基准时钟,以保证信号的精确采样,然后将转换后的信号,送入FPGA里的硬件加速模块,该模块通过Verilog hdl语言编程实现,由硬件二值化,条纹判断,和串并转换等子模块组成,经过该硬件逻辑后的条纹信号在SOPC架构下,由负责系统处理器和外设之间的内联Avalon总线,送往NIOS II内核处理器,最后在NIOS II IDE中完成绝对位置信息的解码和显示。

2硬件架构的实现

2.1编码采集的实现

2.1.1线阵CCD驱动

编码采集主要是针对绝对光栅编码条纹明暗的采集,条纹采集质量将直接影响绝对光栅的解码精度,而条纹采集质量将受到线阵CCD驱动设计优劣的影响,本文CCD采用 TCD1209D,它是一款典型的高灵敏度,低暗电流的单沟道线阵CCD,内含2088个像素单元,该器件正常工作需要5路驱动信号,其驱动信号为:转移脉冲SH,移位脉冲F1,F2,复位脉冲RS,及其钳位脉冲CP ;并且各路驱动信号必须满足图1所示的时序关系;由图可知CCD信号输出每帧数据的分布情况是:首先是32个哑元像素,接着是2048个有效像素,最后是8个哑元像素[3-4]。SH的周期称为行周期,行周期应大于等于2088个转移脉冲φ1的周期Tφ1。只有行周期大于2088Tφ1,才能保证SH在转移第2帧信号时第1帧信号能全部转移出器件。

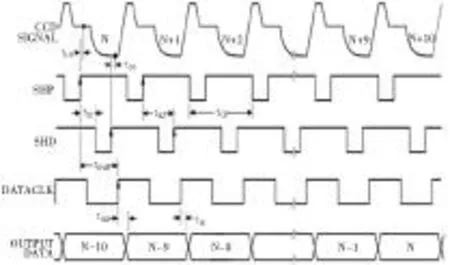

2.1.2AD9804驱动

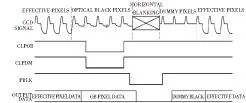

AD9804集相关双采样,自动增益,和A/D转换为一体的10位转换精度的转换芯片;CCD模拟信号进入AD9804以后,首先进行直流重建,输入钳位,相关双采样(CDS),VGA增益放大后进行AD转换,在输出时钟dataclk的控制下输出10位精度的像素数据,图2是CDS时序,图3是线性钳位时序,由时序图可知cds和钳位时序必须保证与ccd输出信号精确同步,与CCD输出信号采用统一的时钟保证输出与采样同步,由输出CCD信号可知,有效范围内的像素输出才是解码需要的输出,为此,重新定义了输出采样时钟fifowclk。

图2 cds时序

图3 线性钳位时序

2.2硬件加速模块

AD转换后的数据在由内核读取之前,需要前期的预处理,才能由内核读取,以解决帧速慢,实时性的问题,所谓硬件加速,就是把用软件解决需要耗费大量时间的一些处理,交给硬件去做,以充分利用FPGA的并行性,提高处理速度。硬件处理主要有三大模块,硬件二值化(levelto_two),条纹判断(strip_judge),串并转换(stringto_parall),硬件二值化主要是把AD转换过来的数字信息进行二值判定,当数据值大于某个阈值时判定为1,代表该像素为亮,反之,为0,代表为暗,而条纹判断主要是明暗条纹的判断,根据ccd像元尺寸14μm,和激光刻蚀栅纹的间距10μm,以及20倍的光学放大系统,得到每条条纹当中所占的像素数至少为14个,我们以大于12个亮的像素数,判断该条纹为明纹,反之为暗纹。解码需要的是16位的解码数据,而串并转换正好是实现16位的编码条纹数据连续读取的模块,负责将单个条纹的数据,缓冲为16个条纹数据供nios内核读取。

2.3Avalon数据接口IP的自定义

Avalon总线为Altera公司为Sopc系统开发的一种专用内部总线,用于连接Nios II软核处理器与外设,是处理器和外设的传输通道,外设依据Avalon总线规范,实现对外设的读写,主要的读写控制信号有:Chipselect片选信号,Byteenable字节对齐信号,read,write读写控制信号和readdata 和 writedata等,为读取解码所需条纹信息,编写定义了read16 ip核,为实现16位编码条纹的解码显示;编写定义用于显示的display ip核,由于NIOS内核是32位的数据总线,与从端口外设进行数据交互时,存在数据宽度的匹配的问题;而Avalon地址对齐分为主,从静态地址对齐,和动态地址对齐两种方式,当主端口对具有静态地址对齐特性的从端口寻址时,所有从端口数据与静态主端口地址边界对齐,动态地址对齐是提供一种动态管理传输数据的服务,当主端口对有动态总线特性的从端口寻址时,所有从端口数据在主端口地址空间按连续字节对齐[5],在这里,我们display Ip核和read16 ip核都采用静态地址对齐的方式,即才用读取低位有效数据高位补0的方式,实现条纹数据的读取。

3SOPC设计

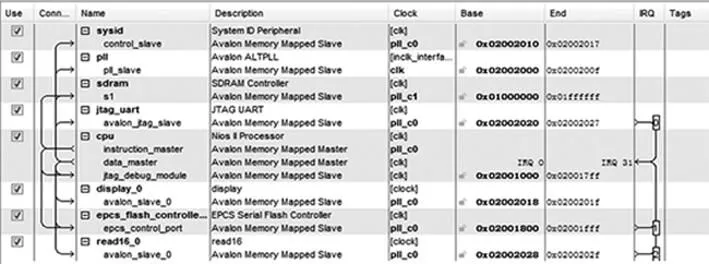

图4 Nios处理平台

利用QUARTUS II SopcBuilder根据采集与解码需求,搭建NIOS II 硬件平台[6-7],该系统SOPC部分主要包括NIOS II 软核处理器,锁相环Pll,及Sdram控制器,Epcs控制器,和自定义的两个ip模块,display,和read16模块;生成NIOS的硬件处理平台,各模块的搭建如图4所示,其中包含CCD和AD芯片驱动模块,和前端硬件加速部分等。

4Niso II程序设计

NIOS II 是Altera特有的基于通用FPGA架构的软CPU内核。具有速度快,高度的灵活性和可配置性及设计流程简单等特点,由于NIOS II处理器有3种可选类型:NIOS/F,NIOS/E,NIOS/S.而 NIOS II/E占FPGA资源最少,但性能低,NIOS/S性能和资源消耗介于NIOS/E型和NIOS/F型之间,而系统硬件资源有限,实时性必须得到保证,故本文选用NIOS/E型完成相应的硬件平台设计。Nios II软件开发环境是NIOS II IDE,内嵌在QUARTUS II设计工具中,该SDK基于GNU C/C++ 编译器和Eclipse IDE,绝对光栅的位置的解码实际上是通过查询编码数据库实现,而编码数据库则是根据玻璃基板上的绝对编码条纹的激光刻蚀方式相应编码生成,在这里我们的刻蚀,以10μm一条编码条纹,按照16位伪随机码的生成原理刻蚀,故我们添入sopcbuilder生成的.ptf文件建立相应工程后,编写相应的伪码生成和显示的应用程序,NIOS II IDE实际上自动建立了2个工程,1个是用户应用程序工程和HAL系统库工程,HAL为NIOS II IDE为用户提供的包含所有与硬件处理相关接口信息的硬件抽象层(HAL),我们通过查阅生成的与目标系统相关的system.h系统描述文件,该文件含有各模块的属性和寄存器地址信息[8-14]。内核Nios II读取相应地址的数据,以供下一步处理。

图5 部分数据处理代码

在系统中NIOS II 程序的任务,除了生成解码数据库外,还要对条纹数据的进行读取和解码操作的显示,NIOS II 软核读取条纹数据有中断和查询方式,实验中,为提高cpu效率,条纹编码数据的采用中断的方式读取,在自编的ip核read 16中,我们已经编写生成了相应中断标志寄存器irq,用于监听内核中断,为实现解码的循环显示,和避免重复数据的错误解码,我们在中断的处理程序中必须及时将中断标志位的清除,图5是主函数处理的相关代码。程序初始化时调用Mint(16)函数,完成数据库的创建,此后在While(1)循环中等待中断的到来,而在read_isr中断处理函数中完成数据的读取,解码和标志位的清除,由于硬件逻辑中处理了软件实现的部分代码,软件处理指令数大大减少,降低了解码处理的时间。提高了绝对光栅编解码系统的实时性。

5实验结果与分析

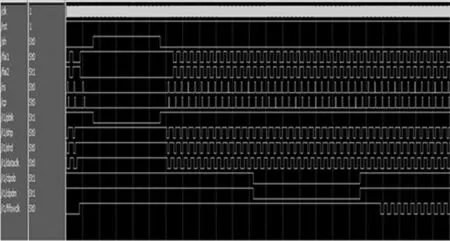

图6 ccd驱动的仿真结果

由于线阵ccd最小光积分时间为1000ns,故我们在QUARTUS II软件开发环境中,在满足最小光积分时间1000ns时,编写Verilog代码,通过计数器的计数和电平变换,生成CCD的驱动,图6 modersim里的仿真结果。与图2和图3比较,时序满足驱动要求。图7是CCD实测输出,满足ccd驱动输出要求,其帧频为2000fps,每帧解码速度为500μs。远高于采用面阵时120fps图像处理的采集帧频。

图7 ccd输出信号

伪随机码的解码基于光栅母尺的编码,实验中玻璃基板刻蚀条纹按照初始相位为0x0001,末相位为0x0000的16级M系列排列,其本原多项我们采用D16+D5+D3+D2+1,由本原多项式和初相生成可供解码查询的数据表如图8所示。

图8 查询数据表

最右边是16位编码,最左边是其实际绝对位置;光栅条纹的实时编码数据的解码由查表完成,由表可知其位置,加上误差修正的像元点数,和采用倍频细分方法,精度可达7μm,不过TCD1209D其像元尺寸为14个μm,为提高测量精度的可靠性和可重复性,采用像元尺寸更小的线阵CCD或CMOS和放大系数更高的光学成像放大系统其精度可以进一步的提高。

6结束语

本文采用线阵CCD作为前端图像采集部件,以FPGA Cyclone II EP2C5T144C8为核心处理器,在对绝对光栅编解码原理研究的基础上,完成了基于NIOS内核的光栅编码采集和解码的软硬件设计,文中通过sopc技术,配置所需要的硬件模块,并添加了用于解码显示和硬件加速的自定义ip核,较好地解决了不同时钟域数据处理模块间的数据流动,编写相应的硬件驱动程序,在帧速达到2000帧/s条件下,精度为7μm,实时性满足应用需求,极大地提高了开发灵活性。

[参考文献]

[1] 卢国纲.绝对光栅尺和编码器是当代位移传感器的发展主流—CIMT2011 精密位移传感器评述[J].世界制造技术装备市场,2011(4):56-60.

[2] 范朝龙,王晗,刘强,等.精密绝对光栅尺的编码采集系统研究[J].组合机床与自动加工技术,2014(11):78-81.

[3] 蒋斐,吴海波,程玉宝.基于相关双采样的线阵CCD信号采集电路的设计[J].光学与光电技术,2010,8(4):60-63.

[4] 李正刚,袁红艳,吴一辉.通用线阵CCD采集系统设计[J].电子设计工程,2009,17(12):18-20.

[5] 林英撑,童晓华. FPGA嵌入式系统设计与开发指南[M].北京:中国电力出版社,2012.

[6] 孟令军,尹维汉,彭晴晴,等,基于Nios II的图像采集系统设计[J].电视技术,2013,37(9):59-60,86.

[7] 王延年,邓毓.基于软核Nios II的Sopc智能温度变送器[J].电子测量技术,2012,35(1):85-88.

[8] 王强,文丰,任勇峰.基于FPGA的高速实时数据采集存储系统[J]. 仪表技术和传感器,2009,45(1):50-52.

[9] Altera Company. Nios2.1 CPU,Data Sheet V1.1[Z], 2002.9.

[10] Hong Lu,Li Yong Tan,Bo Lei,et al. A kand of linear array ccd drive frequency regulation technology [J].Advanced materials research,2010,139-141: 2279-2282.

[11] Wei jun C,Chun kuang T.Design of CCD Acquisition System Based on Nios Ⅱ[J]. Microcontrollers & Embedded Systems, 2012(8): 17.

[12] Lin M O, Tu T A N, Lei W, et al. Design of CCD Spectrum Data Acquisition System Based on SOPC [J]. Journal of Atmospheric and Environmental Optics, 2013(2): 12.

[13] WANG Lei-yang,LI Zheng-sheng,FENG Xiao-wei,et al.Research and development of high-accuracy device measuring clearance based on linear array CCD [J].Electronic Design Engineering ,2011,19(5):67-71.

[14] CHANG Liang-liang,WANG Guang-long,ZHANG Cheng-ji.Design of Image Acquisition and Storage System Based on SOPC[J].Measurement & Control Technology,2012,31(11):11-14

(编辑李秀敏)

Absolute Grating Encoding and Decoding System Design Based on NIOS

LIU Bin,CHEN Xin,CHEN Xin-du,DU Xue, CAI Nian, LV Yuan-jun,WANG Han

(School of Electromechanical Engineering,Guangdong Provincial Key Laborator of Micro-nano Manufacturing Technology and Equipment,Guangdong University of Technology,Guangzhou 510006,China)

Abstract:In order to realize the fast decoding absolute grating ruler, improve the real-time absolute grating decode, we established an on-chip Nios absolute grating encoding and decoding system. First of all, by using Verilog HDL language ,we encoding CCD and AD driver which acquisite front-end grating. Then, we take the converted data to the backend where taking the EP2C5T144C8 FPGA as the core processor of hardware acceleration module, we obtain grating stripe code information. Then, using the SOPC technology, based on the realization of Avalon data interface IP core,we build absolute grating code acquisition and processing platform, finally, in the NIOS II IDE software development environment, we write programs which can generate the database of the pseudorandom code absolute position to query and decode. The experimental results show that: This codec system get the accuracy of the 7μm in the decoding speed of 2000 frame/s conditions, basically solve the problem that the frame speed is inadequate by taking the plane array as the front-end acquisition, and has good real-time performance, effectively reduce the cost of development, provides a new way for the development of absolute grating.

Key words:Nios ; drive acquisition ;absolute grating ruler ;decode

中图分类号:TH164;TG506

文献标识码:A

作者简介:刘斌(1990—),男,江西赣州人,广东工业大学硕士研究生,研究方向为绝对光栅尺编解码,(E-mail)jxndgxylb@163.com;通讯作者:王晗(1980—),男,湖北钟祥人,广东工业大学副教授,博士,研究方向为超精加工与检测技术,光学仪器设计,嵌入式控制系统设计,(E-mail)wanghangood@gdut.edu.cn。

*基金项目:广东省微纳加工技术与装备重点实验室(2011A060901021);省部产学研(2011A090200119)

收稿日期:2015-04-16

文章编号:1001-2265(2016)03-0112-03

DOI:10.13462/j.cnki.mmtamt.2016.03.031