基于CDCE906的频率合成器

北方工业大学电子信息工程学院 李亚舟 张新燕 刘秋平 王恩成

基于CDCE906的频率合成器

北方工业大学电子信息工程学院李亚舟张新燕刘秋平王恩成

【摘要】本文主要是介绍了一种利用单片机控制的频率合成芯片CDCE906。其中芯片的频率变化是通过单片机利用IIC总线技术将控制数据发送到CDCE906芯片寄存器内,进而频率合成芯片输出相对应的频率值。

【关键词】CDCE906;频率合成;单片机

随着通信技术、测量技术、航天航空技术的迅速发展,人们对于振荡信号源的要求不断提高。频率合成技术便是其中的关键技术之一。利用该技术搭建的电路成为频率合成器。频率合成器是利用一个或多个信号,通过各种技术途径产生大量离散频率信号的设备。按照频率产生机理可将其分为:直接模拟合成法、锁相环合成法以及直接数字合成法。直接模拟频率合成法是利用一个或是多个不同晶体振荡器作为基准信号源,经过倍频、分频、混频等方式直接产生多个频率的输出信号。锁相环合成法是通过锁相环进行加、减、乘、除等运算方式,产生所需的频率输出信号。直接数字合成法是直接以离散时间的方式产生信号,通过改变幅度、频率和相位的方式进行频率合成。本文主要利用锁相环合成法来实现频率合成器,通过使用单片机控制可编程时钟乘法器CDCE906产生不同的频率信号。

1 频率合成器的硬件设计

1.1硬件电路部分

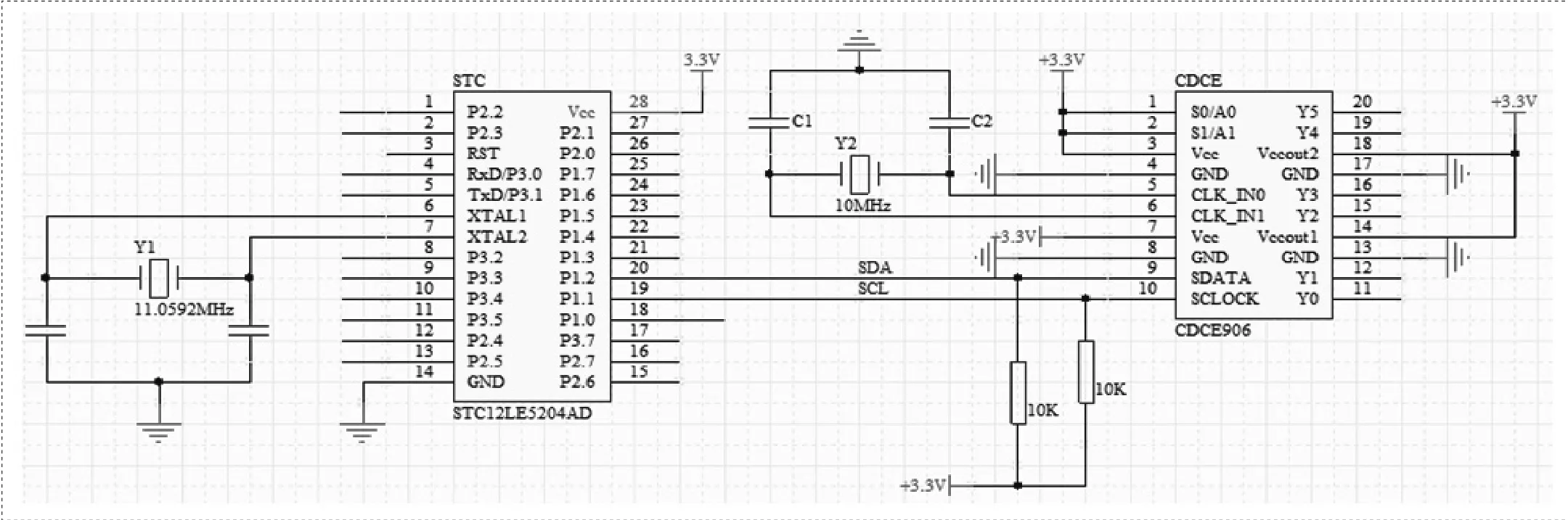

利用STC12LE5204AD单片机控制CDCE906产生频率信号的硬件电路原理图如图1所示。可编程时钟乘法器CDCE906具有IIC接口,便可采用单片机与CDCE906通过IIC总线协议进行通信,不具有SDA、SCL管脚的STC12LE5204AD单片机芯片,可在程序内部对其进行定义,本设计中将单片机的P1.1、P1.2管脚分别定义为SCL、SDA管脚。单片机与CDCE906均采用3.3V电压供电,单片机选择11.0592MHz的晶振,CDCE906则选择10MHz的晶振。

图1 单片机与CDCE906连接的硬件电路原理图

1.2CDCE906简介

可编程时钟乘法器CDCE906是基于锁相环(PLL)模块的频率合成芯片,其内部包含3个PLL模块,只需一个信号源,便可产生6路输出,且每路的输出信号可根据3组PLL在线编程实现,最高输出频率可达167MHz。其输入信号可以是时钟晶振信号、单端LVCMOS信号或是差分输入信号。时钟晶振的频率范围为8MHz到54MHz,而单端LVCMOS号和差分输入信号可达到167MHz。本文中采用的外接晶振时钟信号,而外接晶振时钟信号一般需加负载电容,如图1中的电容C1、C2,为产生稳定的输出频率,C1、C2均取值18pF。

2 软件结构设计

2.1IIC总线协议

单片机与CDCE906通信采用IIC总线协议,IIC总线是由数据线SDA和时钟线两条线构成通信线路,既可发送数据,也可接收数据。在CPU与被控IC之间、IC与IC之间都可以进行双向传送,最高传送速率可达到400kpbs,各种被控器件均并联在这条总线上,单每个被控器件都有唯一的地址。在信息传输过程中,IIC总线上并联的每一个器件既是主控器(或被控器),又是接收器(或发送器),这由其所要完成的功能决定。CPU发出的控制信号分为地址码和数据码两部分,地址码由于选址,即接通需要控制的电路,数据码是通信内容,这样各控制电路虽在同一条总线上,却又彼此独立,互不相干。

IIC总线在传输数据的过程中,共用3中类型信号,分为是:开始信号、应答信号和结束信号。

2.2CDCE906控制指令

利用IIC总线协议控制器件时,每个器件都有自己的控制指令格式,需按照规定的指令格式才能实现正常通讯。

CDCE906包含两种操作方式:字节写(Byte Write)与块写(Block Write)。CDCE906的所有字节均有缺省值,如果只需修改其中的少数几个地址,不连续的字节便可以获得多要的结果,建议使用字节写方式。如果需要改动多数字节,块写方式就更为方便。本文采用的是字节写方式对相应的字节进行修改。

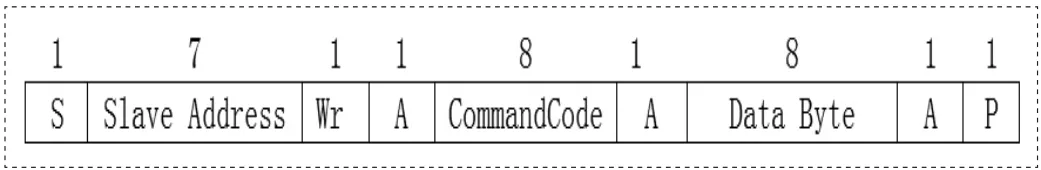

CDCE906字节写方式的通信协议如图2所示。其中S表示开始条件,Slave Address为将要写入芯片的地址, 通过S0、S1控制管脚设置芯片的地址,就可以实现单片机对相对应的CDCE906芯片进行读写操作。Wr=1表示单片机对芯片进行写操作。CommandCode的最高位为0时,芯片通信方式为块读写方式,最高位为1时,芯片通信方式为字节读写方式,CommandCode的低7为读写字节的偏移地址。在对CDCE906进行写操作时,都是从低字节向高字节写,写完之后芯片会回馈一个应答信号ACK,写入为低,未写入高。

图2 CDCE906字节写方式通信协议

CDCE906中控制管脚S0、S1分别控制芯片是否处于休眠状态、输出端是否被禁止,且二者均是低电平有效。而当CDCE906的第10B的低4位全部置为1的时候,S0、S1就成为了芯片的地址选择管脚。本文中只是对单个CDCE906的应用,所以第10B的低4位使用默认缺省值0000,Slave Address使用缺省值11010010,将S0、S1管脚置高,即在图1电路中所显示的,将S0、S1均接3.3V电压,以保证其始终为高电平。

2.3控制寄存器值的计算

在给定输入频率(本文采用的是CDCE906芯片的晶振的频率),CDCD906芯片的输出频率可通过公式(1)计算得:

其中M、N是PLL的乘法器/除法器的值;P是锁相环输出的分频因子,并且。M、N、P的取值范围分别是1~511、0~4095、1~127。

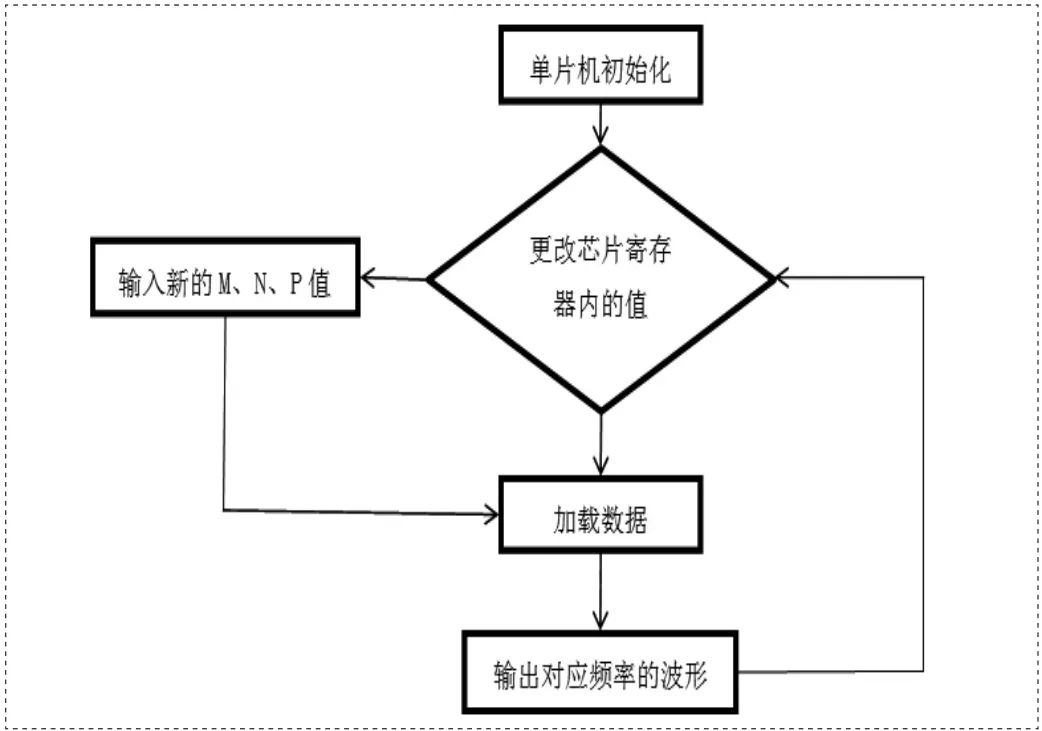

图3 单片机控制CDCE906芯片的程序流程图

2.4控制程序的设计

单片机控制CDCE906芯片(如图3所示)的程序流程图如图3所示,单片机与CDCE906芯片是通过IIC协议实现通信的,可以利用单片机控制CDCE906内部PLL的M、N、P的值,得到不同频率的方波信号。

由于本文中选用的STC12LE5204AD单片机芯片没有IIC接口,所以需要自定义,

即sbit SDA = P1^2; sbit SCL = P1^1。

3 结束语

将程序下载到单片机之后,再给单片机和CDCE906同时供电,通过示波器就可以观察大清晰的输出波形——方波,利用单片机改变CDCE906寄存器内的M、N、P值,就可以得到相对应的输出频率,也可以将M、N、P设置为变量,使CDCE906输出频率扫描信号。

参考文献

[1]王子剑,徐钊,房咪咪,等.基于电驻波的锚杆长度测量仪设计[J].煤矿安全,2012,43(9):111-113.

[2]徐钊,房咪咪,周红伟,等.基于电驻波的锚杆长度无损测方法[J].工矿自动化,2013,39(9):112-115.

[3]赵博,李林,姬红兵.CDCE906倍频性能分析[A].西安电子科技大学,2011.

[4]杨立永,杨日杰,董云龙.基于CDCE949的可控频率源设计与实现[J].电子设计工程,vol.9,no.5,2011.

[5]杨勇,张东方,王运生.锚杆锚固质量无损检测理论研究与应用[J].工程地球物理学报,2010(3).

[6]任雷,林岩,张干沫阳.基于CPLD的OMAP-L137 与ADS1178数据通信设计[J].单片机与嵌入式系统应用,2009,8:26-28.

[7]张厥盛,曹丽娜.锁相与频率合成技术[M].成都:电子科技大学出版社,1995.