基于DDS和DSP提高跳频频率合成器的幅度稳定性研究

孟祥军(沈阳斯达特电子科技有限公司,辽宁沈阳,110122)

基于DDS和DSP提高跳频频率合成器的幅度稳定性研究

孟祥军

(沈阳斯达特电子科技有限公司,辽宁沈阳,110122)

摘要:针对于传统的通信系统中跳频速度慢、分辨率不足的问题,设计了基于DSP+DDS的高速度、高分辨率的跳频器。通过DSP 对DDS的制产生调频序列,同时通过自学习产生频率幅度曲线,对产生的信号进行闭环控制产生高稳定频率和幅度输出。

关键词:自学习;DDS;幅度稳定性

0 引言

通信系统在民用、商用、军事上承担着语音、图像等重要数据信息的传输作用;尤其是涉及到国家安全的信息传递设计到国家安全和国家利益的问题;信息传送的安全成为重中之重。作为无线传输设备的发射接收开放性,往往存在容易被截获、侦听、干扰的问题;而跳频通信的方式可以极大的降低信息泄漏的风险;而跳频的核心部件跳频频率合成器,决定了一个跳频通信系统的关键性能指标。近年来低功耗DDS的出现对设备终端的小型化和低功耗化起到了很好的作用,而文献[4]的功耗较大和信号稳定性控制没有起到闭环控制,导致在整个频带范围内信号幅度变化较大。本设计就是设计一套基于DSP+DDS的低功耗跳频系统。

1 系统硬件设计

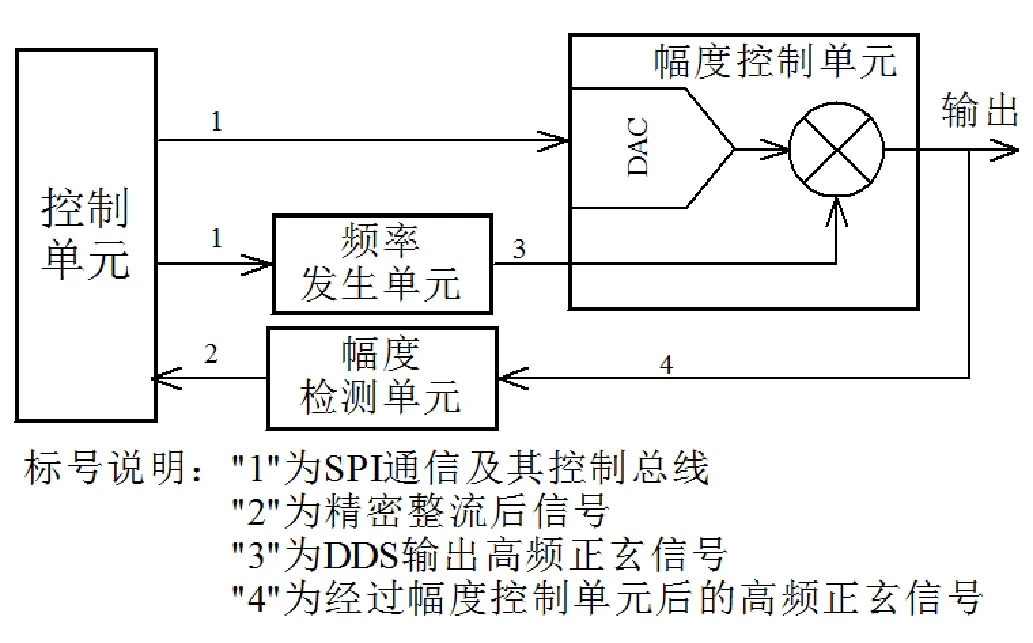

本设跳频系统计采用TI的TMS320VC5509A的数字信号处理芯片(DSP)作为控制单元,以直接数字频率合成芯片(DDS) AD9953作为频率发生单元;以高速运放AD8037和高速开关二极管IN4148构成了精密整理电流,作为幅度检测单元;以高速乘法器AD834和数模转换器MAX532ACWE构成了幅度控制单元;系统主要有上述的4个单元共同构成一个高速频率捷变、频率分辨率高、频率稳定性高、幅度稳定性高的跳频频率合成器单元。系统构成如图1系统结构图所示。

图1:系统结构图

本系统的采用的控制芯片TMS320VC5509A的工作时钟最高达到200M;而该芯片另一个特性是低功耗,本设计采用了TQFP封装144脚的芯片,最高工作频率可以达到144M;本系统采用100M工作主频,外部采用25M高稳定度的有源时钟信号,为控制芯片提供时钟频率,DSP采用4倍频,使系统工作在100M主频。控制芯片电源采用了TPS767D301PWP高稳定双电源为DSP提供1.8V内核电源和3.3V外部IO单元电源。该芯片内部有128Kx16bit的RAM,可以完成代码加载和复杂算法计算所需要的RAM空间;芯片采用Boot Loader方式加载代码。

使用芯片自带的ADC进行对幅度检测单元进行信号幅度采集。采用芯片自带的高速SPI口控制DDS和幅度控制单元的芯片工作。实践中TMS320VC5509A与DDS和DAC的通信速度可以达到10Mbit/S。可以轻松实现对其进行1M/S的控制速度。

采用的DDS芯片为AD9953,该芯片最高工作主频为400M,而时钟源信号频率为25M;因此DDS采用内部的倍频电路,使外部低频信号16倍频后变为400M,变为DDS时钟信号。由于DDS自身的性能限制其输出最高频率在应小于时钟信号的40%,因此本系统定位最高频率为150M,使得输出信号平滑,信噪比较高。

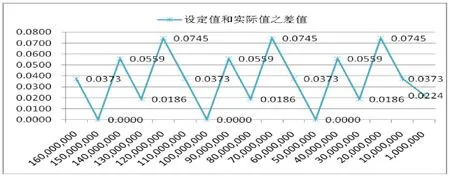

图2:DDS输出的设定值和实际值之差

图3 精密整理滤波电路

2 DDS频率输出控制分析

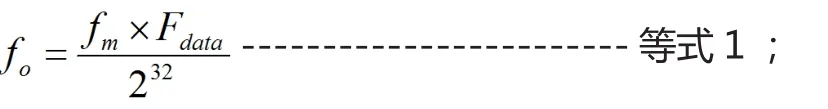

DDS芯片工作主要是对倍频器设置、相位寄存器、频率寄存器、工作模式寄存器等的设置来完成;设置较为简单;根据被系统的性能要求,设定为输出信号初始相位为0。在本系统中主要是关心的指标为频率的输出稳定性文体。而DDS的频率控制32bit的频率寄存器来完成;其目的输出频率与DDS时钟频率和频率寄存设置数据成线性关系。关系如等式1:

由等式2知由于fm为固定数据,为了提高数据的计算精度和DSP的计算速度,可以得到一个频率与频率设定寄存器的系数,其数据位等式3:

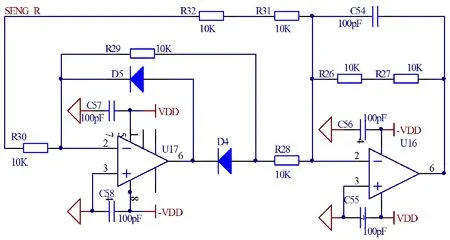

3 幅度检测与计算

幅度检测部分采用了标准的全波精密整流放大电路,完成对正弦信号转化为直流信号的过程;该电路在工程应用中已经很成熟本设计放大器采用了高速AD8037和高速开关二极管IN4148构成。如图3所示精密整流滤波电路:

该电路实现了对正玄信号的精密整理转化为0-3.3v的直流电压信号过程。其计算模型可以等效为如等式5所示:为ADC采集到电压,为信号放大系数;为幅度单元输出信号的峰峰值。由于采用的ADC为10bit的分辨率,对信号分辨能力为3.3mv。当系数信号为峰峰值1v的信号时,由于可以取值为3倍放大,经过处理后可以完成对输出信号幅度1mv的采集分辨率;可以很好的控制变频输出信号的输出幅度。

每天我们都会面对着无数的选择,有些事芝麻小事不值得一提,但有些对于我们人生却又较大的影响。我们不断受到无数选择的轰炸,这使我们无法每次都能够做出最恰当的选择。但有个非常有效的技巧——批判性思维。要做到批判性思维有许多方式,但以下四步可以帮助你更好的建立你的批判性思维。

4 输出幅度控制原理

对于信号的输出幅度控制,由于采用的高速乘法器AD834和数模转换器MAX532ACWE设计,AD834的信号计算速度为500M的四象限乘法器;而MAX532ACWE为响应速度在1M以上的DAC输出;可以快速实现对信号幅度的调整功能。MAX532ACWE双路12位数模转换器,一路配置为正常输出方式,另一路采用分压方式,分压比例为1000:1;然后采用两路模拟信号相加的的方式;即可以实现DAC输出控制幅度控制电压分辨率在50uV以内;通过AD834对和进行乘法计算,得到幅度可控的高稳频率、幅度的输出信号。根据AD834的计算模型可以进行如下计算得到等式7;为AD834输出负载的系数;由于AD834芯片特性要求和的绝对值必须小于1v的信号。

5 软件实现

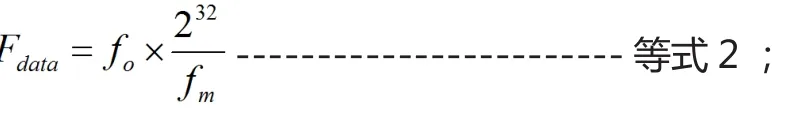

系统控制部分采用TMS320VC5509A完成;上电后,DSP首先根据预定模式进行代码从外部存储器中加载到片内RAM,然后进行DSP初始化,然后调用根据系统的模式加载参数,初始化DDS和根据输出频率初始化幅度控制单的DAC,同时检测输入信号。检测完毕加载设置调频部分进行工作。系统上电时序图如图4所示。

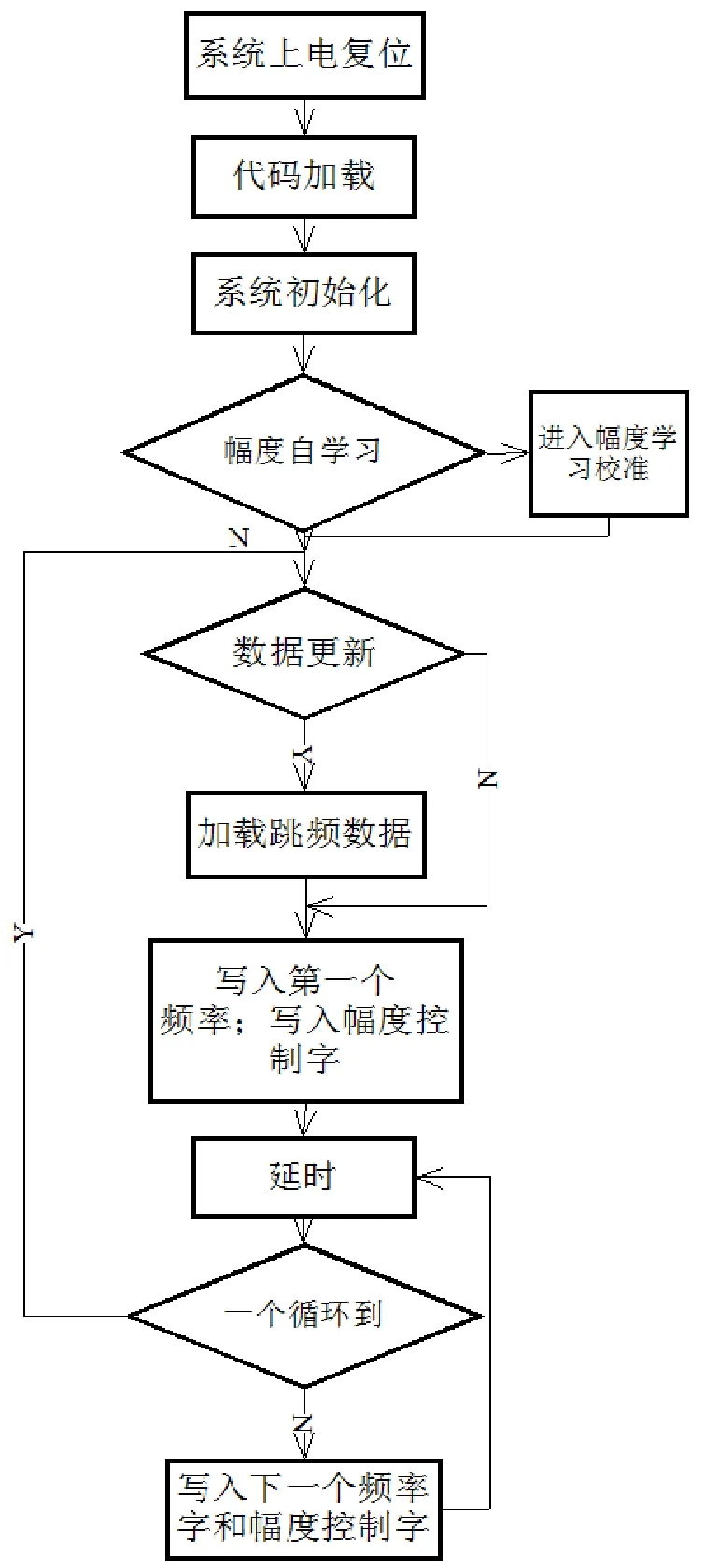

当幅度信号在10-160M之间幅度具有衰减的时候,启用幅度自学习代码,进行自学习校准功能。其校准的工作方法主要是根据输出频率,检测对应的幅度值,当幅度超过误差允许范围时,通过设定DAC参数使输出幅度可以进行放大和缩小的控制,构成闭环幅度控制系统,而校准后,可以得到一个频率点和其幅度差值的控制表;当每次发生频率变化的时候就计算出一个对应的DAC的输出电压来校准输出幅度。幅度控制自学习的控制流程图如图5所示。

图5 幅度控制自学习的控制流程图

6 输出数据测试

(1)系统工作频率范围:10M到110M赫兹时系统能够输出良好的调频幅度波形。根据奈奎斯特定力,由于主频在400M,系统最高能达到200M赫兹,但是实际测试中发现当信号超过140M以后,噪声明显增加,系统没有达到理论极限之。

(2)测试得到的结果,由于频率范围从10M到110M赫兹之间变化时,当不采用幅度控制时,信号的幅度下降回答道30%,采用幅度控制后,信号的幅度能稳定在峰峰值为1v误差在5mv以内;达到了预期的幅度稳定功能。

(3)当采用幅度自学习控制后,然后再进行调频测试时发现信号能够在跳频速度为1000跳/秒 的速度下稳定工作,良好的控制幅度,但是如果调频速度到10000跳/秒,由于DAC补偿的信号产生的噪声明显加强,如果更高速度调频方式则难以达到幅度良好的跟踪效果。

(4)调频信道间隔:100-1000Hz可以通过软件设定间隔。

(5)调频信道数:可以进行最大5000个,其使用方式可以根据实际需要的方案制定。

(6)信号幅度稳定度:幅度差小于5mV。幅度误差小于2%。

(7)信号输出幅度:Vpp=500mv.

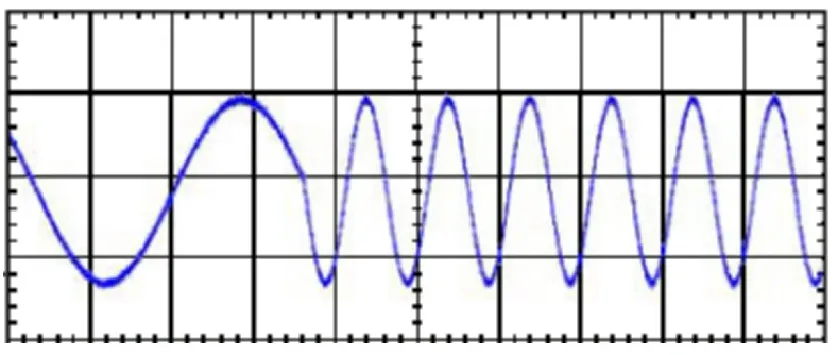

跳频过程中,示波器扑捉的信号测试如图6所示:

图6 在10M到30M之间调频测试捕捉效果

7 结论

该设计有效的解决了DDS在宽频带范围内输出信号幅度不相等的问题。实现了自学习方式对DDS输出不同频点进行补偿曲线的学习。而本系统采用了跟随技术和对幅度控制的软件工作量较大,而且系统的数据验证需要大量的时间。又由于本系统工作频率较高,尤其DDS输出部分的信号使工作在10-150M之间,设计PCB时必须注意高频干扰文体;而且本设计中采用了高频乘法器和高速模拟放大器,这些器件设计和使用一定要注意高频性能。PCB设计必须要采用手动布线结合软件的仿真进行设计。经过测试该系统工作稳定性良好,可以很好的完成跳频中幅度稳定性控制;可以应用到实际系统中。

参考文献

[1](美)比斯利(Beasley),等 著;吴利民,等 译.现代电子通信(第9版)[M].清华大学出版社,2009.11.

[2]童诗白 。模拟电子技术基础(第四版)[M]. 高等教育出版社, 2010.

[3]梅文华,等.跳频通信[M].北京:国防工业出版社,2005.

[4]李鹏,等.基于DSP的短波跳频频率合成器的设计[J].计算机测量与控制.2009.17.10.2036-2054

孟祥军(1982.9-),男,山东郓城人,大专,助理工程师,主要从事涡流检测设备研究。沈阳斯达特电子科技有限公司研发部部长。

Research on amplitude stability of frequency synthesizer based on DDS and DSP

Meng Xiangjun

(Shenyang Strarter Electronic Technology Co; Ltd, Liaoning Shenyang, 110122)

Abstract:Aiming at the problem of slow frequency hopping and low resolution in traditional communication systems, a high speed and high resolution frequency hopping device based on DSP+DDS is designed. Through the DDS to produce the DSP frequency modulation sequence, while the frequency amplitude generated by selflearning curve, the signal generated by the closed-loop control of high frequency and amplitude output.

Keywords:self-learning;DDS;amplitude stability.

作者简介