基于FPGA的高速峰值检测模块设计

大连东软信息学院电子工程系 高锦阳 谢 浩 杨云棋

基于FPGA的高速峰值检测模块设计

大连东软信息学院电子工程系 高锦阳 谢 浩 杨云棋

本文是根据2016年集创北方企业杯赛题要求所设计的高速峰值检测模块,可以在 640个16位宽的有符号数里,快速找到最高的5个峰值的位置,并将5个峰值点的行坐标及列坐标作为模块的输出。

高速 FPGA ;定位; 比较 ;排序

1 引言

高速峰值检测技术(PDK, Peak Detector)一直都是数字采集卡与数字存储示波器中的关键技术之一。在日常生产实践中,对最大峰值的检测与定位也一直是众多领域的需求之一。峰值检测用来实现对尖峰干扰脉冲信号的捕捉或高占空比信号的检测,以及类似发生在采样周期内极大的冲击信号的检测。

峰值检测的分模拟与数字两种实现方法,模拟峰值检测电路就是一个特殊的硬件电路,用电容电压的方法来存储信号的峰值,采集速度很慢。相比来说围绕ADC构成的数字式峰值检测器就可以按照一个更高采样速度对信号进行采样,通过检测模块测量出极大、极小值存入RAM等待排序与筛选,就此可以实现高频信号的检测。

2 赛题分析

2.1 设计要求:在640个16位宽的有符号数里,快速找到最高的5个峰值的位置,并将5个峰值点的行坐标及列坐标作为模块的输出。640个数据是按照32行20列的方式存储于单口RAM里。峰值是指该数据的绝对值大于自己周围的8个数据的绝对值。

2.2 设计指标:时钟频率:不能低于30Mhz;时长:需要的时间越短越好。

2.3 实现方式:硬件选用Xilinx公司的V5系列FPGA,软件使用ISE(www.xilinx.com)

3 高速峰值检测模块的硬件电路设计

现场可编程逻辑器件(Field Programmable Gate Array, 简称FPGA)是目前被广泛采用的用于高速及复杂数字电路设计的大规模可编程逻辑器件,是一种纯硬件电路,门级延时仅仅是纳秒单位,可工作在高达200MHz频率。而其内部逻辑设计可采用类似高级语言的硬件描述语言,给硬件设计提供了极大的灵活性。

图3.1 模块图

3.1 模块说明

3.1.1 添加行列信息模块:Ram本身为线性储存结构,并且本身不含有行列信息,本模块用来取ram中的数,并且为每个提取出来的数据添加行列信息。

3.1.2 缓存模块:从前一个模块输出的串行数据本身依旧是线性的,本模块将线性的数据储存为矩阵的形式,该模块本身也充当缓存的作用,提高数据读取效率,每一个数据都会比较多次,这样可以避免数据重复读取。

3.1.3 比较模块:从前一个模块输出的并行数据参与比较,判断当前数据的绝对值是否大于周围8个数据的绝对值,如果为真,则输出数据,否则输出为0。

3.1.4 排序模块:从前一个模块输出的数据进行排序,只保留最大的5个数据。

3.1.5 储存模块:储存640个数据的线性储存器。

3.1.6 7段数码管显示模块:显示系统找到最大的五个数据以及对应数据的行列信息。

3.1.7 二进制数转BCD码模块:用于7段数码管的显示译码。

3.1.8 顶层模块:例化其他子模块,并且增加按键消抖功能(本项目有开始键)。

3.2 运行原理分析

3.2.1 Ram中的数据本身不含有行列信息,利用计数器读取储存器中的数据,同时同步运行行列计数器,在读取数据时,需将数据本身和计数器的值(行列值)合并存入缓存模块,这样就得到了含有行列信息的数据。

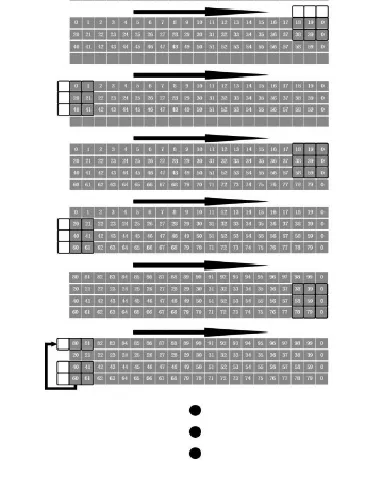

3.2.2 缓存模块由4个寄存器组组成,每个寄存器组储存21个数据,最后一列0用于数据隔离(因为比较模块利用3x3九宫格形式,周围的数据地址是以正中间的数据的地址为基准的偏移地址,例如扫描模块当中间扫描到19、39、59这样的行末尾时,右边的数据本应该为空,但是偏移地址会跳到当前行的下一行,这样就会出错),数据从第一行依次存入缓存模块,当前两行存满时,比较模块开始从第一列0地址逐行扫描比较。四行都储存满时,重新从第一行存入,覆盖原来的数据。

图3.2 缓存模块

3.2.3 比较模块为3x3九宫格形式,周围的数据地址是以正中间的地址为基准的偏移地址,同时从缓存模块取数,利用中间的值和周围8个数据的值进行比较,当缓存模块两行数据储存满时,比较模块开始运行,流程演示如下:

图3.3 比较模块

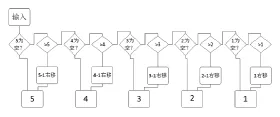

3.2.4 由比较模块挑选出中间值大于周围8个值得数据,这些数据随即进入排序模块进行排序,使用的原理为流程图如下:

图3.3 流程图

该模块将5个排序的数合并为一个高位的数,从左往右依次从大到小排列,一个数据进入首先判断位置“5”是否为空,是的话将数据存入位置“5”,否则判断是否大于位置“5”,是的话除位置“5”以外的部分整体右移后再将数据存入位置“5”否则以此类推判断位置“4”直至最后。

3.2.5 找到最大的5个数据时,数据通过二进制转BCD码模块转换为BCD码,采用左移加3的算法实现转换,步骤:(1)左移要转换的二进制数1位。(2)左移之后,BCD码分别在个十百千万位。(3)如果移位后所在的BCD码大于等于5,则对该值加3。(4)继续左移直到全部位移完成。转码之后再通过数码管显示模块显示出来,先显示行列信息,然后显示数据本身

3.2.6 按键消抖当按键按下后,会出现电平抖动,当低电平维持10ms确认按键被触发,使用计数器实现

原理图:

图3.4 原理图

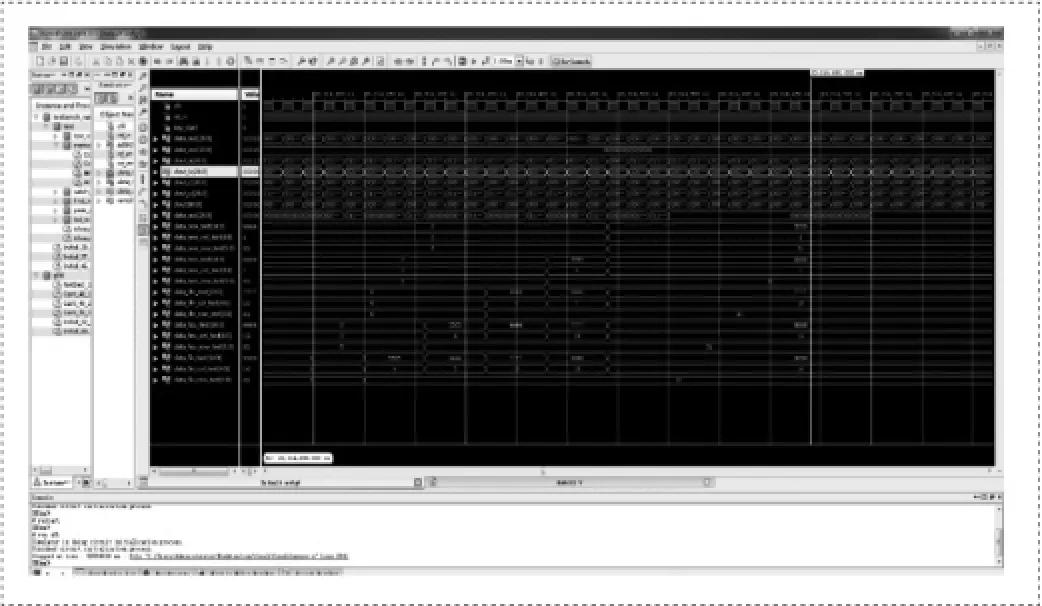

4 高速峰值检测模块的设计仿真

设计仿真图如下:

图4.1 仿真图一

放大后的图如下:输出的数据本身还含有行列信息,此结果专门用于测试,将数据位、行列信息单独抽取出来显示。

图4.2 仿真图二

5 高速峰值检测模块的内部资源报告以及时序报告

5.1 内部资源5.2 时序报告

图5.1 内部资源

图5.2 时序模块

6 结束语

首先考虑如何实现系统功能,然后进行模块划分以及模块内部算法实现,接着进行模块内部设计并且考虑每个模块需要哪些IO以及前后模块IO的时序衔接,完毕后每个模块单独仿真调试,之后进行整体仿真调试,最后下载到开发板进行测试对比是否和仿真结果相同。

本项目下载到开发板采用默认50MH时钟,运行正常,所以不需要使用在线逻辑分析仪再进行测试。该项目本身在功能实现上并没有用到特别难的算法,难点在与如何在耗费一定资源尽可能的提升系统速度,我们仔细研究每个模块的时序,尽可能不浪费每一个时钟周期,提升系统运算效率。

[1]阎石.数字电子技术基础. 高等教育出版社,2014.

[2]夏宇闻.Verilog数字系统设计教程[M].北京航空航天大学出版社,2008.

[3]易先军,叶春生.基于FPGA的高速数字峰值保持器设计[M].华中科技大学 塑性成形模拟与模具技术国家重点实验室.湖北 武汉.

高锦阳(1993-),男,内蒙古呼和浩特人,大学本科,现就读于大连东软信息学院电子工程系集成电路设计与集成系统专业。

谢浩(1994-),男,山西阳泉人,大学本科,现就读于大连东软信息学院电子工程系集成电路设计与集成系统专业。

杨云棋 (1996-) ,男,辽宁法库人, 大学本科,现就读于大连东软信息学院电子工程系集成电路设计与集成系统专业。