基于QT的数字逻辑虚拟实验平台设计

徐睿++韦璐

摘要:虚拟元件库是数字逻辑虚拟实验平台最重要的组成部分之一,良好的数字元件模型有助于提升虚拟元件库的可扩展性、易维护和易操作性等。本文在抽象和形式化表示数字元件的基础上,采用Qt MVC架构设计和开发了一个数字逻辑虚拟实验平台。该平台全局一致的数字元件模型能有效提升虚拟元件库的可用性和开放性,为建立统一的虚拟实验教学环境提供依据和保障,使用者和研究者可依需进行二次开发,节省时间,提高绩效。

关键词:QT;MVC;虚拟元件;虚拟实验平台;建模

中图分类号:TP391.41

文献标识码:A

DOI: 10.3969/j.issn.1003-6970.2016.01.022

0 引言

计算机等信息与电子工程等专业的教学不仅注重理论教学,更强调实验与实践教学,提高学生的知识应用能力。传统实验室和实验设备能够给学生提供真实的实验场景,但建设资金高昂、资源损耗较大,且存在仪器与设备落后,实验教学形式单一等诸多问题。虚拟实验室利用计算机来模拟实验环境以及实验过成,学生无需进入实验室,只需要通过计算机登录实验平台既可以选择实验。虚拟数字实验平台通过虚拟化数字元件和实验的方式,具有投入成本低廉、无损耗、维护简单、更新快等优点,易于保证数据采集的实时性,以及数据处理、显示、存储的完整性和连续性等优势,为解决传统实验室存在的问题提供了一种有效的解决途径。2015年1月,我国教育部批准了100个国家级的虚拟仿真实验教学中心,必定进一步推动和提高我国实验教学管理信息化和支持服务信息化水平。

虚拟实验平台已经成为诸多工程和学术领域的重要实验手段,各种新型的架构和设计方法不断涌现,如MVC架构下基于B/S的网络实验室架构、基于MVC设计模式的虚拟实验平台模块化的设计方法等等。基于LabView、Proteus等EDA软件也常被用作模拟和数字电路的虚拟实验平台。这些商用软件功能强大,注重于电子元器件和板级电路的物理特性和功能特性的仿真,但由于版权等问题,并不适于课堂教学和学生自主实验等方面的应用。中南大学的数字电路虚拟实验室系统[X]在实验运行的过程中,能够实时展示芯片的状态信息,并构建了教学节点的测试实验库。高翔等基于Qt[X]的场景视图模式开发和设计了虚拟实验构件建模设计软件。张婧采用输入输出缓冲接口说明(I/OBuffer Information Specifica-tion,IBIS)设计了虚拟实验的数字芯片的建模方式,通过简单的文本数据来描述数字模型的行为。

然而,按传统实验进行“虚拟化”的处理方式,不仅功能有限、开发工作量大,易于造成资源浪费和重复开发;而且缺乏系统性的研究,也使得关于虚拟实验教学的教学设计和教学模式严重滞后。因此,本文从数字逻辑元件的特性入手,首先对数字逻辑器件进行抽象和形式化描述,以构建通用的虚拟元件模型。然后,在此基础上采用Qt MVC架构,设计和实现了一个数字逻辑虚拟实验平台来验证模型的可用性。

l 虚拟数字逻辑元件模型

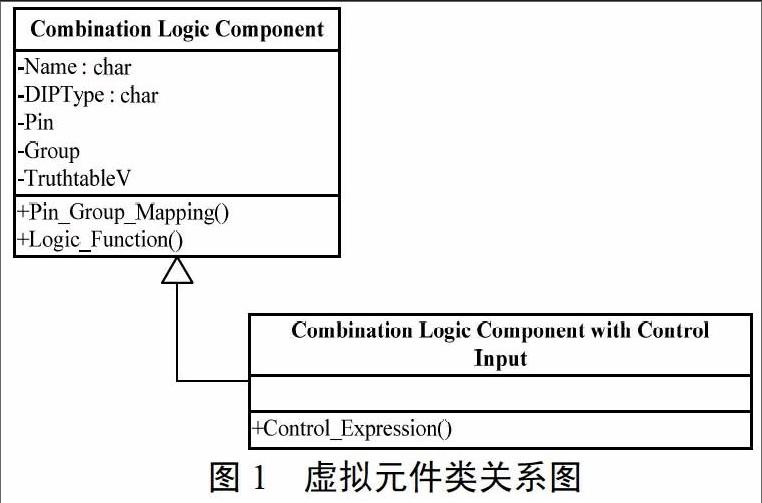

虚拟元件库的可护展性直接受制于虚拟元件模型的一致性。数字逻辑芯片通常由其内部特性和外部特性两个方面来描述。其中,外部特性主要不同封装形式的引脚排列顺序等;内部特性则是芯片的逻辑功能。相对于芯片封装形式的多变性,芯片的内部特性则具有强不变性。由此,本文虚拟元件模型的重点是表示数字逻辑芯片的功能特性,并通过其与封装模型的关系建立来构造虚拟元件。本文将数字逻辑芯片划分为组合逻辑芯片与带控制的组合逻辑芯片等两种类别,以简化元件模型的表示和提升元件模型的一致性。

定义1 组合逻辑元件模型C,由六元组(A,I,G,Ω,F,V)表示。其中,属性组A由芯片的名字等静态属性组成;Ω:I—G,是信号集I与信号组集G之间的映射,对任意的i∈I,有且仅有一个g∈G,使得i∈g。F:I{V}I是元件的逻辑函数,完成以输入信号查阅真值表V获得有效输出信号的处理过程。

定义2 带控制的组合逻辑元件模型Cctrl,是在组合逻辑元件模型C的基础上,增加控制表达式成员E而构成的七元组(A,I,G,Ω,F,V,E)。同时,F被重定义为P{VIE}P,表示仅在控制表达式E运算结果为真时,才能通过真值表V获得输入信号对应的输出信号。表达式E是由给定的一组输入信号gE(gE∈G,gE p,|p|-|gE|>2)参与运算的逻辑表达式。

上述定义中的信号组G是为更好地按功能划分信号而引入的,与元件信号的功能分组对应,如输入信号集和输出信号集等,但并非是必要的。对象的构成模型是从对象的内部结构的角度出发,从对象范型来看,定义2从定义1继承而来是有利于模型的程序化实现的,如图1所示。

2 虚拟数字逻辑元件库

虚拟数字逻辑元件库主要是管理虚拟元件模型和维护元件及其封装形式间的关系。但封装形式可以展示芯片外观,却不能展示芯片内部的功能部件。

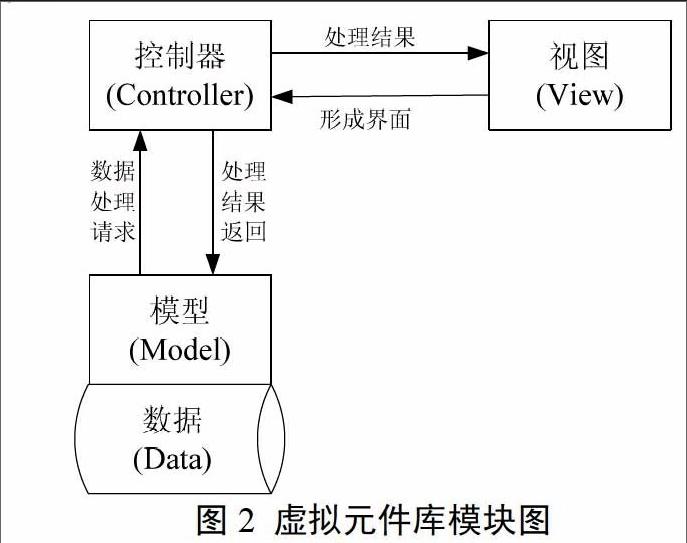

MVC (Model View Controller)设计模式以模型(M)、视图(V)、控制(C)分离模型与界面的代码,使得同一个模型可有多种不同的表现形式,以控制确保模型数据与界面的同步。从而使系统各模块相对独立,既提高了代码重用性和扩展性,也能让开发者在一个时间内专注于一个方面而不依赖其他业务逻辑,明显提高开发的效率。

基于元件模型的定义,本文采用MVC设计模式分离元件的封装形式与其功能部件,并将部件作为封装形式的子视图来构建可视化的虚拟数字元件,如图2所示。

定义3 虚拟数字逻辑元件VC,由四元组(s,c,t,£)表示。其中,s是如DIP40等封装形式;c是元件模型;t是元件逻辑视图;£:CPIG→SS是元件信号集或信号组集与封装形式引脚序号的映射,即将元件模型的信号映射到封装形式的一个引脚或一组引脚上。

定义4 虚拟数字逻辑元件库L是带引脚映射£约束的元件模型集C、封装形式集S和元件逻辑视图集T的笛卡尔集。

基于上述定义,虚拟数字逻辑元件模型可以使用不同的封装形式、元件视图来表示的同时,也有利于简化元件的描述和存储方式,增加元件库的易用性和扩展性。使用者在可配置的基础上,针对不同的环境条件应用需求,设计不同的元件,完成相应的功能。

3 虚拟数字逻辑实验平台

如图3所示,数字逻辑虚拟实验平台主要包括虚拟元件库的管理模块和实验平台两个模块。虚拟元件库管理模块包括虚拟元件模型、封装形式和元件逻辑视图的添加、编辑、删除以及引脚配置等管理功能。实验平台以虚拟电路板的形式,除提供既定的教学实验外,也允许用户自主选择元件、构建实验电路,并仿真实验的运行过程,包括新建/打开实验、保存实验、运行实验等功能。

为了降低演示平台的开发难度和缩短开发周期,采用Qt MVC模式,将元件视图独立设计,而将元件模型与控制整合在一起,而没有涉及元件模型、封装形式、元件视图和引脚配置的用户自主管理等功能。

基于Qt平台开发的数字逻辑虚拟实验平台,其虚拟元件的数据模型是独立于视图和控制器的,模型的本身并不用关心自身如何显示或者如何被控制,但是模型中所存储的数据一旦发生了变化便会通过QT平台的信号与槽的机制进行刷新。信号和槽是QT自行定义的一种通信机制,独立于标准的C/C++语言,它可以让对象之间彼此并不了解的情况下将它们的行为联系起来。在QT中,信号和槽均作为类的成员函数,当槽和信号相连接时,每当信号发射,槽函数就会被调用,信号和槽通过connect函数连接。当某个信号对其对象或所有者发生的内部的状态发生改变,信号被虚拟元件发射。当这个信号被发射时,与其相关联的槽将被立刻执行。其中槽是普通的成员函数,执行槽就等于函数正常调用,它的特殊性在于很多信号可以与其相关联。当与其关联的信号被发射时,这个槽就会被调用。在数字逻辑虚拟实验平台中,虚拟元件模型均绑定了一个信号,其中的数据一旦发生变化,便会发射信号导致相关的函数,刷新视图和触发该模型的控制器。

实际操作中,实验开发者只需给定元件的真值表、引脚、封装形式等信息,以及带控制的逻辑元件的控制表达式,即可完成实验元件自定义和或是扩展系统的元件库。

4 应用实例

数字逻辑虚拟实验平台构建了虚拟元件库,提供了典型教学与实验系统的逻辑工作过程演示程序。用户可以直接使用该虚拟元件库中的元件为教师的教学及学生的学习提供理想的教学演示。跑马灯原理演示效果见图4。

在工作电路上,我们看不到芯片的内部逻辑,只看到实验程序的结果,即导线颜色和LED灯的变化。该平台的实验展示,可以很清晰地看到整个电路的结果变化。学习者不仅可以观察到元件的实际作用,也可以看到实验的工作过程,从而使得他们可以从实验电路的整体工作过程,加深对基础知识的理解和掌握元件的应用方法。

5 总结

虚拟实验具有成本低,效率高,范围广,可重用性和可操作性强的特点,已贯穿到了工程类专业的课程教育中。数字逻辑虚拟实验平台的基础是模型元件以及元件库。本文研究通过对数字逻辑芯片的结构分层,采用基于QMVC框架对数字逻辑芯片的模型进行设计。这种体系结构避免了编程的复杂性,由于虚拟元件的相互独立型有助于实现虚拟实验平台的开放性,只需对元件进行简单的配置便可作为新的虚拟元件使用,而不用修改相应的程序。