用于植入式医疗装置的逐次逼近式模数转换器

张鸿,张牡丹,张杰,赵阳,张瑞智

(西安交通大学电子与信息工程学院,710049,西安)

用于植入式医疗装置的逐次逼近式模数转换器

张鸿,张牡丹,张杰,赵阳,张瑞智

(西安交通大学电子与信息工程学院,710049,西安)

针对植入式医疗装置对模数转换器(ADC)的超低功耗和高精度要求,提出了一种共模恒定型分段混合编码结构的逐次逼近式模数转换器(SAR-ADC)。该SAR-ADC的电容数模转换器DAC中采用分段混合编码结构,兼具了分段二进制编码的低功耗优势和分段温度计编码的高线性度优势。共模恒定型控制方式具有极低的动态功耗。采用HHNEC 0.35 μm CMOS工艺完成了10位共模恒定型分段混合编码SAR-ADC的电路和版图设计。后仿真结果表明:所设计的SAR-ADC的电源电压范围为1.8~3 V;在采样率为103s-1的条件下,其有效位数为9.4位;整个SAR-ADC所消耗的电流仅为60 nA,在同等工艺条件下具有更低的功耗;所设计的转换器能够满足心脏起搏器等植入式医疗装置的需求。

医疗装置;植入式;超低功耗;逐次逼近型;模数转换器

近年来,在微电子技术的推动下,人工耳蜗、心脏起搏器等植入式医疗装置已在临床中得到广泛应用,脑机接口等技术也在逐渐走向成熟。模数转换器(ADC)是植入式医疗装置中的关键电路,它将生物电信号转换成数字形式。植入式ADC处理的生物信号频率一般在几十kHz以下,转换精度要求在10 bit以上。为了延长植入式装置的使用寿命,需要尽可能降低植入式ADC的功耗。在各种结构的ADC[1-3]中,逐次逼近式ADC(SAR-ADC)具有功耗低、面积小的优点,是目前植入式ADC的主要实现形式。

通常,SAR-ADC包括数字控制逻辑,数模转换器(DAC)和比较器3部分。其中,仅有比较器消耗一定的静态电流,ADC的大部分功耗为控制逻辑以及开关电容DAC中开关动作引起的动态功耗[4]。因此,为了达到植入式医疗装置要求的极低功耗,国内外的研究者们对进一步优化开关控制逻辑进行了深入研究,以有效降低整个ADC的动态功耗。目前已有的SAR-ADC开关控制时序有传统型[4]、节能型[5]、单调型[6]和共模恒定型[7]等。在相同的采样速度和精度条件下,节能型、单调型和共模恒定型的功耗分别约为传统型功耗的1/2、1/5和1/8。因此,采用共模恒定型开关控制逻辑的SAR-ADC在植入式医疗应用中具有明显的低功耗优势。然而,文献[7]中共模恒定型SAR-ADC的电容DAC(CDAC)采用了二进制电容阵列,使得总电容值随ADC位数的增加呈指数增加。另外,其电容阵列中最大电容与最小电容的比值高达2N-2(N为ADC的位宽),电容失配和寄生电容的影响将显著增加ADC的微分非线性误差(DNL)和积分非线性误差(INL)[8]。在CDAC中采用分段式电容阵列可有效降低最大电容与最小电容的比值[9],从而在一定程度上提高ADC的线性度。然而,若分段式CDAC中每一段采用二进制阵列[10],制造误差导致的电容失配仍然会制约整个ADC的精度和线性度。虽然温度计编码的CDAC能够有效地降低ADC的DNL和INL[11],然而若对CDAC的电容阵列全部采用温度计码控制,则对于N位精度,其DAC需要2N-1对子电容和相应的开关控制逻辑,这将显著地增加控制逻辑的复杂性和开关动态功耗。

本文在共模恒定型开关控制逻辑的基础上,提出了一种分段混合编码结构的SAR-ADC,其中CDAC的高段位电容阵列,采用温度计编码,低段位电容阵列,采用二进制编码的混合编码电容阵列,可以在较低的电路复杂度和功耗条件下获得较高的线性度。本文采用HHNEC 0.35 μm工艺,设计了一款采用分段混合编码结构的10位SAR-ADC。后仿真结果表明,本文ADC具有较高的线性度和极低的功耗,可完全满足心脏起搏器等植入式医疗装置的需求。

1 共模恒定型SAR-ADC功耗分析

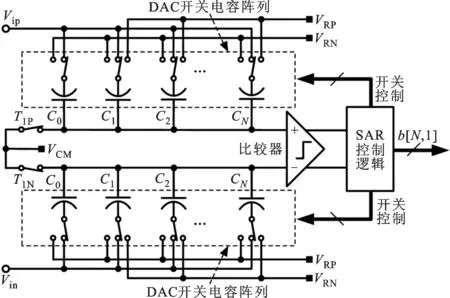

图1 传统型SAR-ADC结构

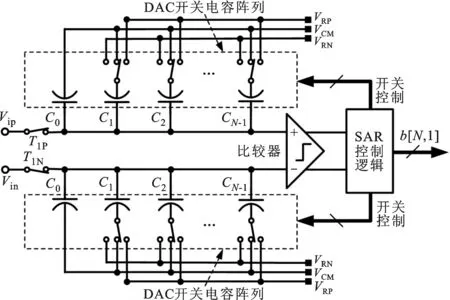

图2 共模恒定型SAR-ADC结构

N位传统开关电容型SAR-ADC的电容阵列中共有N+1对电容,Vip和Vin为差动输入信号,VRP、VRN和VCM分别为DAC的差动基准信号和共模信号,C0=Cu(Cu为单位电容),其余电容为Ci=2i-1Cu(i=1,2,…,N),b[N-1]为ADC输出的N位数字码。传统型SAR-ADC的结构如图1所示。在采样阶段,输入信号通过采样开关T1P和T1N接到电容的下极板。完成采样后,控制逻辑按照预设输出值、判断和确定输出值的顺序,从高到低逐次确定ADC的每一位转换结果,整个过程将引起大量的开关动作,从而导致较高的动态功耗。针对这一问题,共模恒定型结构对传统的SAR-ADC结构进行了改进,将输入信号从电容的上极板接入,电容的下极板在采样时接共模信号VCM,如图2所示。在位数相同的情况下,共模恒定型结构的电容比传统结构少1对,总电容值为传统结构的1/2。

为了说明共模恒定型SAR-ADC在动态功耗方面的优势,本文以3位ADC输出全为0时的情况为例,对比分析两种结构SAR-ADC的电容控制过程。

(1)

(2)

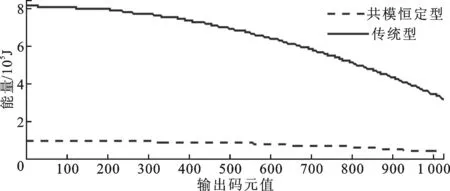

对比式(1)、式(2)可知,由于共模恒定型结构不需要预设操作,因此可以大大降低动态功耗。按照上述分析方法,本文分别对以上两种类型的10位SAR-ADC输出所有码值时的开关电容能耗进行了Matlab建模。两种ADC的单位电容Cu都为120fF,差动基准电压VR都为2V,开关电容能耗对比结果在图3中给出。可以看出,共模恒定型结构具有明显的低功耗优势。

图3 传统型与共模恒定型开关逻辑的能耗对比

2 CDAC的线性度分析

DAC的线性度决定了SAR-ADC的线性度指标。在一定的工艺条件下,CDAC的线性度取决于其电容阵列结构。以下对几种DAC电容阵列结构的线性度进行分析,进而给出本文所用的电容阵列结构。

2.1 纯二进制CDAC的线性度分析

制造误差使得电容很难满足精确的二进制比例关系,电容失配与电容的面积之比有关[4]。若两个相同面积的电容比例失配系数为ε,则面积比例为2i的电容的失配系数通常为iε。所以,对于一个N位的二进制电容阵列,考虑失配后的各电容值可表示为[4]

Ci=2i-1Cu[1+(i-1)ε],i=1,2,…,N

(3)

根据式(3)可知,若采用纯二进制电容阵列,则位数越高,比例误差就越大,由此引起的非线性误差也将越大。

2.2 分段二进制编码CDAC的线性度分析

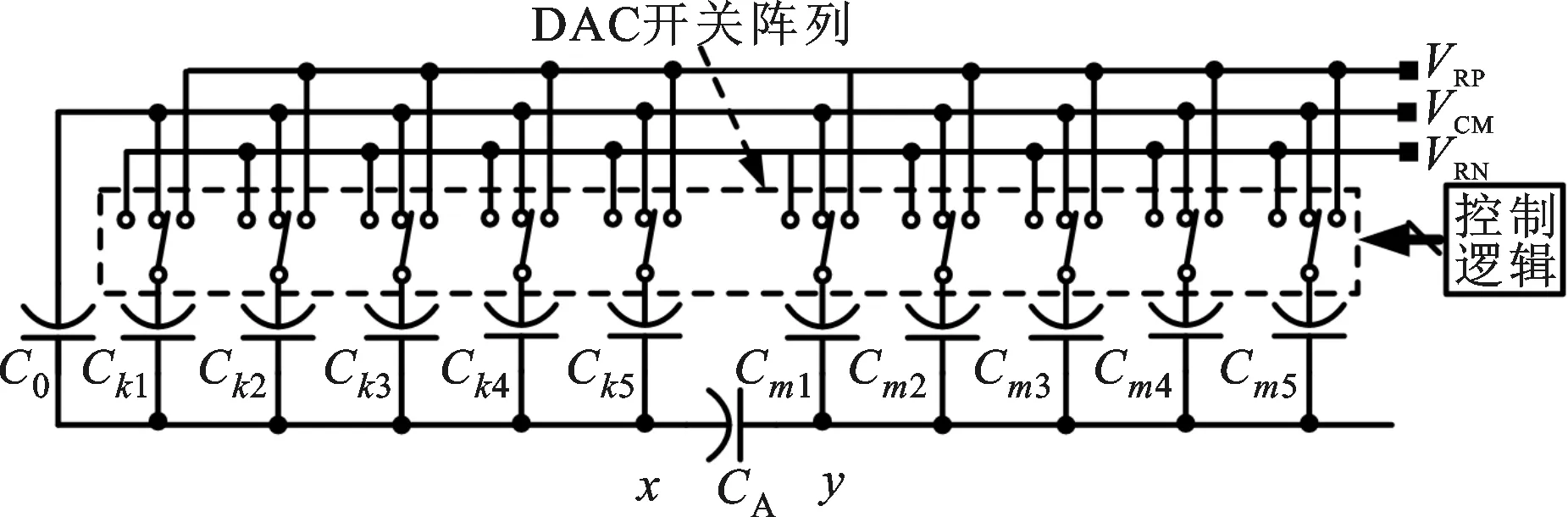

分段二进制电容阵列可大大减小最大电容与最小电容的比值,因此可以显著提升SAR-ADC的线性度[9]。其主要特点是将DAC的数字码按高低分为包含m位和k位的两组。相应地,电容阵列也分为m对和k对电容的两段。两段之间用一个跨接电容连接,各段内仍采用二进制编码。以10位DAC为例,若将电容阵列分为各包含5对电容的阵列,即m=k=5,则其差动结构的半边电容阵列如图4所示。

理想二进制情况下,Cki=Cmi=2(i-1)Cu,(i=1,2,…,5)。为了使低段电容和跨接电容CA的总电容等效为Cu,CA电容值应为(16/15)Cu。此时,高、低两段电容的最大电容与最小电容之比降低为16,可大大降低DAC的非线性误差。

图4 10位分段二进制编码DAC的半边电路结构

为了定量分析CDAC的非线性误差,需要求出DAC输出电压与输入数字码的关系。分段二进制DAC转换完一组数字码后,x和y节点的电压Vx和Vy可通过电荷守恒方程来求解

(4)

Vy=

(5)

考虑电容失配后,将实际电容值带入式(5),即可求出每组输入数字码所对应的DAC转换结果。由于存在电容失配,该结果必然存在非线性误差。若给定的输入数字码所对应的十进制表示为K,则该码的微分非线性误差可表示为

(6)

式中:Δ为DAC的最小分辨率电压值,即Δ=VR/2N。

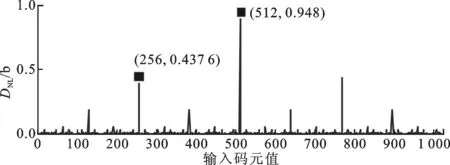

在电容失配系数ε=0.001的情况下,由式(5)和式(6)得出的10位分段二进制DAC的DNL曲线如图5所示。可见,输入码为512时DNL值最大,约为0.95b。这是因为输入数字码元从511切换到512过程中,所有开关都翻转,最大电容与最小电容的失配必然导致大的DNL。

图5 10位分段二进制码CDAC的DNL曲线

2.3 分段温度计编码CDAC的线性度分析

由上述分析可知,分段二进制电容DAC减小了最大电容与最小电容的比值,从而可以降低电容失配的非线性。然而,段内的二进制电容阵列的电容失配仍然会导致较大的DNL。为了进一步降低电容失配,可用温度计编码电容阵列来替代二进制电容阵列。

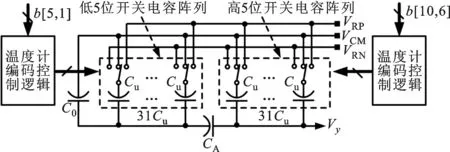

在温度计编码电容阵列DAC中,用一个温度计编码模块将输入的N位二进制码转换为2N-1位的温度计码。相应地,电容阵列也拆分为2N-1个等值的单位电容。由于所有电容面积相等,所以比例失配大大降低。另一方面,温度计编码结构中,输入数字码增加1或减少1时仅引起一个最小单位电容的开关切换,因此可以获得最小的DNL值。然而,如果N位DAC的电容阵列全部采用温度计编码结构,则需要2N-1个单位电容和相应的控制开关。这一方面使得控制逻辑非常复杂,另一方面过多的开关也会引起额外的开关功耗和芯片面积。解决这一问题的方案是在分段式结构中,分别对两段电容进行温度计编码。以10位分段式DAC为例,将高5位和低5位的输入数字码分别进行温度计编码,并分别控制高段和低段的31个单位电容,如图6所示。

在电容失配系数ε=0.001的情况下,参照2.2节的方法对温度计码的DNL进行数学建模,得到图7所示的DNL曲线。对比图5与图7可知,分段温度计编码的DNL大大降低。

图6 10位分段温度计编码CDAC的半边电路结构

图7 10位分段温度计编码CDAC的DNL曲线

2.4 分段混合编码CDAC的线性度分析

对比图4与图6可知,分段二进制编码与分段温度计编码CDAC的总电容值相等,但是在性能方面,前者编码电路更简单,芯片面积和开关动态功耗更小,但其最大电容与最小电容之比较大,因此线性度较差;后者因为所有电容相等,而且温度计编码的单调性使其具有极高的线性度,但是所需的电容和开关个数较多,由此引起的面积和动态功耗开销更大。

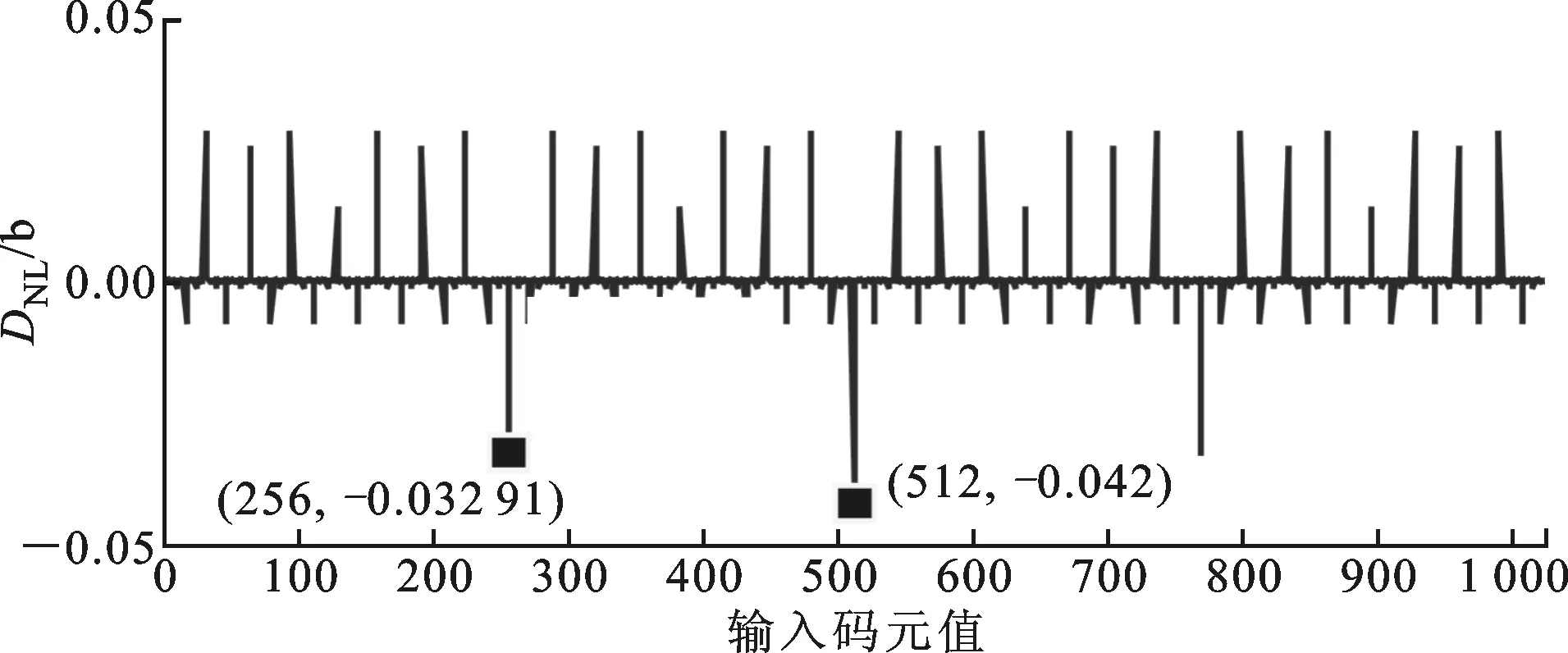

为了兼顾两者的优势,可以将两者结合形成分段混合编码型CDAC结构,在略微牺牲线性度的条件下,获得更小的动态功耗和芯片面积开销。由于分段结构中,高位数字编码的权重更大,因此将高段电容设计为温度计编码有助于提高线性度。为了对比分段混合编码结构与上述两种结构的非线性特性,本文在相同的电容失配条件下,对一个10位的分段混合编码CDAC进行了数学建模,在高5位采用温度计编码,低5位采用二进制编码。该DAC的DNL曲线如图8所示。可见,分段混合编码结构DAC的最大DNL也出现在512码处,约为-0.3b,其绝对值略高于分段温度计编码结构的最大值,但仍小于常规要求的0.5b。

图8 10位分段混合编码CDAC的DNL曲线

3 分段混合编码SAR-ADC设计

3.1 总体结构

在前述分析的基础上,为了满足植入式医疗装置对ADC的超低功耗和中等精度要求,同时使ADC具有较小的芯片面积,本文采用共模恒定型结构设计了1个10位的SAR-ADC。综合考虑ADC的线性度、功耗和面积指标,ADC中的CDAC采用分段混合编码电容阵列结构。根据图2所示,10位共模恒定型SAR-ADC中的CDAC仅需要9位控制码。为了使整个ADC具有足够高的线性度,高5位电容阵列采用温度计编码结构,而低4位电容阵列采用二进制结构。

3.2 SAR-ADC控制逻辑电路

本文SAR-ADC的控制逻辑电路包括一个4位计数器和译码控制逻辑电路。在输入时钟信号CK16K、控制逻辑使能信号EN和比较器输出指示信号VALID的控制下,产生DAC开关阵列和比较器所需要的多个控制信号。输出端的CKR、CKS和CKC分别为复位、采样控制和锁存比较器锁存信号;CKi为与ADC第i位结果相对应的DAC开关阵列的控制信号;CKL为ADC输出结果的锁存控制信号,各输出信号的时序如图9所示。由图9可见,SAR-ADC每16个时钟周期完成1次A/D转换,有效的采样率为103s-1。ADC在前5个周期完成信号采样,在最后一个周期,CKL的上升沿将10位结果锁存到结果寄存器中。

图9 本文SAR-ADC控制逻辑图

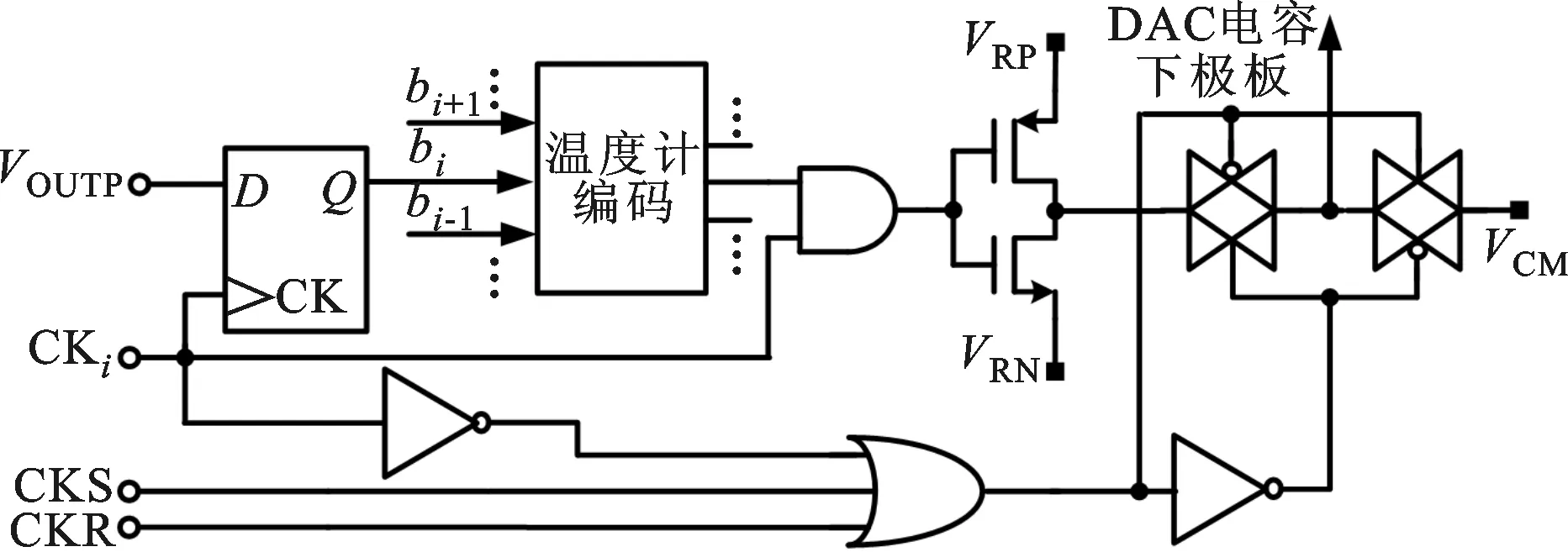

DAC电容阵列中的每一个电容都需要一个开关控制电路,利用CKi、CKR、CKS以及比较器输出结果VOUTP或VOUTN(VOUTP、VOUTN分别为比较器的正、负输出信号),控制电容阵列中相应的开关电路,产生正确的电容下极板电压,实现DAC转换,如图10所示。结合图9可知,CKi的上升沿将比较器输出的第i位数字码锁存到寄存器的输出端,与其他位一起进行温度计编码后,通过2选1选择器选择相应的基准电压(VRP或VRN)接至相应电容的下极板。在复位和采样期间,电容的下极板都接共模电压VCM。二进制阵列中电容的开关控制电路与图10相似,但不需要温度计编码,因此结构更简单。

图10 温度计编码电容阵列中单个电容的开关控制电路

3.3 比较器电路设计

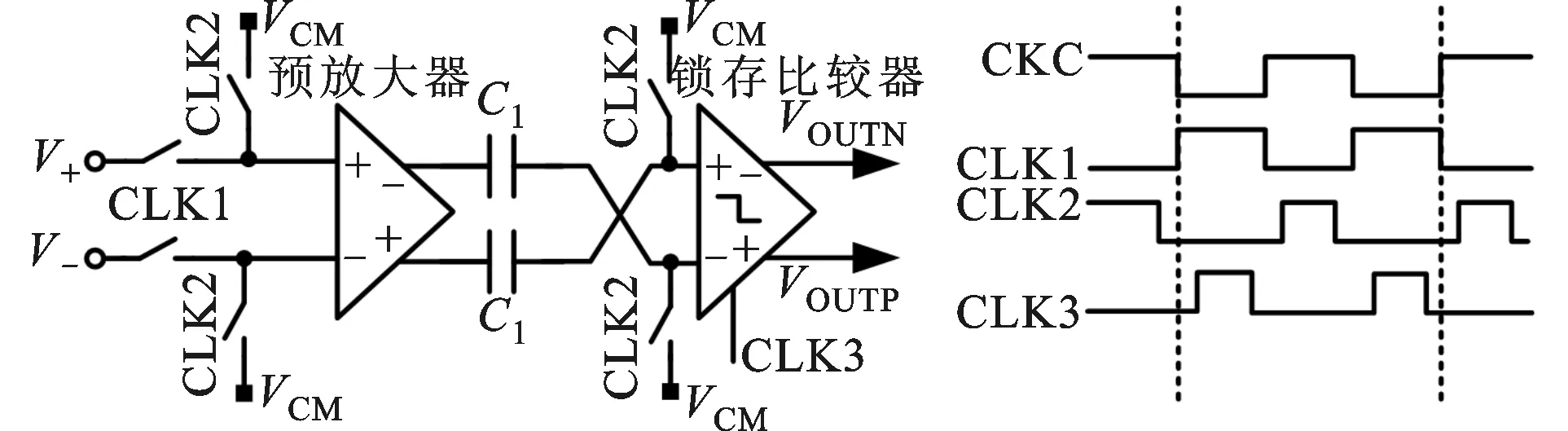

作为SAR-ADC中唯一的模拟电路,比较器的失调电压将会直接影响到整个ADC的性能。为了减小比较器的失调电压,本文采用了预放大锁存的比较器结构,并采用开关电容结构利用比较器的开关时序实现失调存储和抵消。其中,C1和C2为失调存储电容,CLK1、CLK2和CLK3都是在比较器使能时钟CKC基础上产生的控制时钟,其电路结构和相应的控制时序如图11所示。CLK2为高时,预放大器和锁存比较器的失调存储在电容C1、C2中。CLK1为高电平期间,比较器完成失调抵消和输入信号的比较。

图11 失调预存储抵消比较器结构和控制时序

4 仿真结果

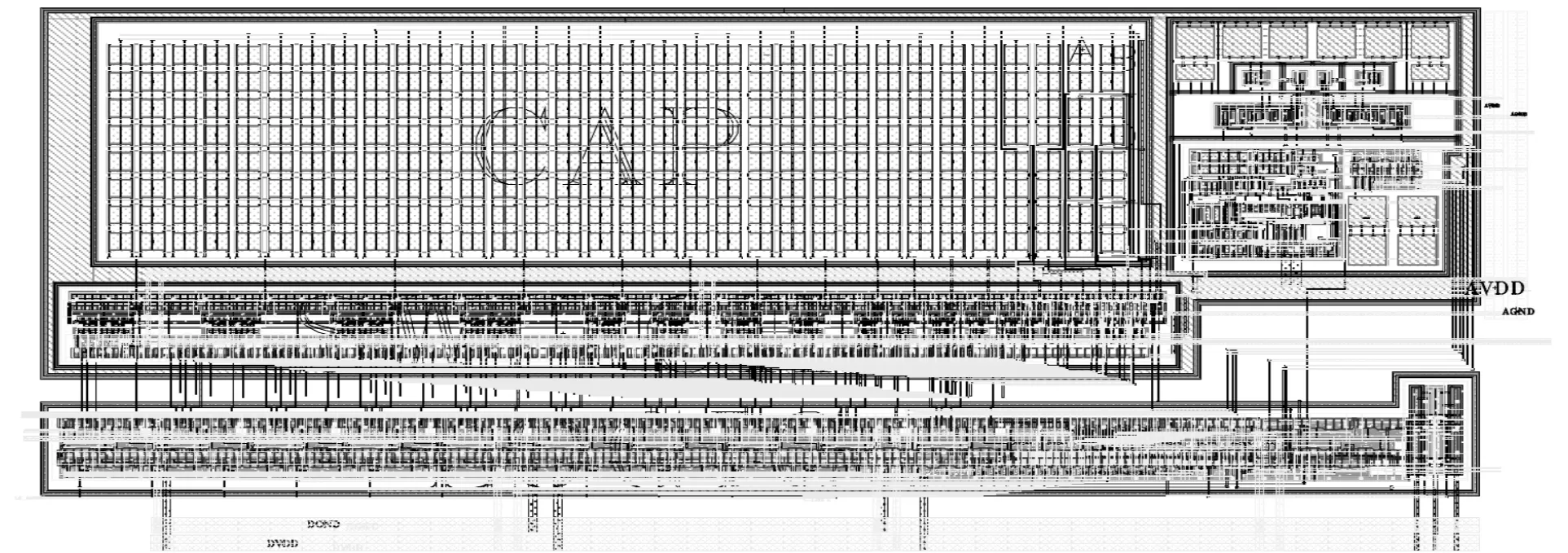

本文的10位共模恒定型分段混合编码SAR-ADC采用HHNEC 0.35 μm工艺设计。为了适应植入式装置电池供电的特点,本ADC的电源电压范围设计为1.8~3 V。ADC的版图面积为299 μm×356 μm,如图12所示。

图12 本文SAR-ADC的版图

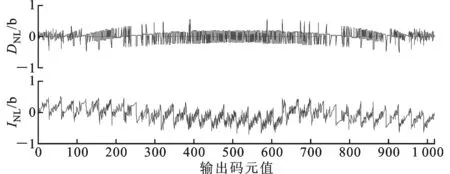

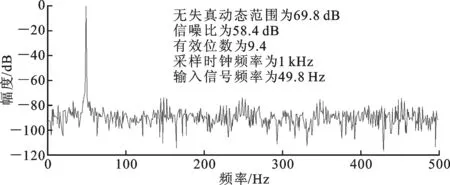

本文进行了版图寄生参数提取和后仿真,得到DNL的绝对值最大为0.55 b,INL的绝对值最大为0.71 b,如图13所示。在采样时钟频率为1 Hz、输入正弦信号约为50 Hz的条件下,ADC的信号噪声失真比为58.4 dB,有效位数为9.4位,如图14所示。ADC工作时的平均电流消耗约为60 nA,其中控制逻辑的电流为48 nA,比较器所消耗的平均电流为12 nA。

图13 后仿真的DNL和INL结果图

图14 ADC的动态性能后仿真结果

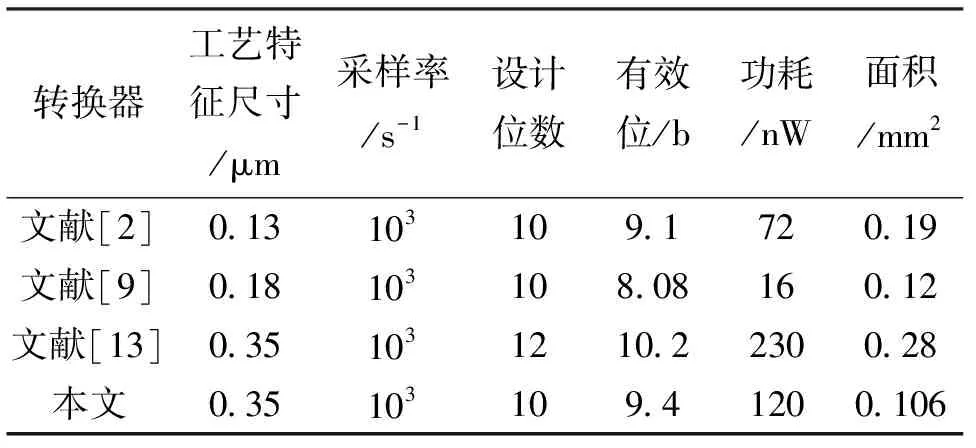

本文SAR-ADC的后仿真详细性能参数在表1中进行了总结,并与近年来的一些相关文献进行了对比(相关文献均为测试结果),可见本文ADC实现了较高的有效位数和较低的芯片面积。考虑工艺条件对功耗的影响,本文的功耗更低。

表1 4种SAR-ADC的性能对比

5 总 结

本文提出了一种应用于植入式医疗装置的10位低功耗共模恒定型分段混合编码结构的SAR-ADC。本文的ADC在共模恒定型控制逻辑的基础上,对CDAC进行分段混合编码,在保证ADC低功耗的同时,实现较高的线性度和有效位数。本文的ADC电路采用HHNEC 0.35 μm CMOS工艺设计,版图面积为299 μm×356 μm。后仿真结果表明,ADC的电源电压范围为1.8~3 V,在采样率为103s-1的条件下,ADC的有效位数为9.4,仅消耗60 nA的电流。

[1] 贾华宇, 陈贵灿, 程军, 等. 流水线模数转换器的一种数字校准技术 [J]. 西安交通大学学报, 2008, 42(8): 991-995. JIA Huayu, CHEN Guican, CHENG Jun, et al. A digital calibration technique of pipelined analog to digital converter [J]. Journal of Xi’an Jiaotong University, 2008, 42(8): 991-995.

[2] ZHANG Dai, BHIDE A, ALVANDPOUR A. A 53-nW 9. 1-ENOB 1-Ks/s SAR ADC in 0. 13-μm CMOS for medical implant devices [J]. IEEE Journal of Solid-State Circuits, 2012, 47(7): 1585-1593.

[3] 张鸿, 陈贵灿, 程军, 等. 流水线模数转换器中高速低功耗开环余量放大器的设计 [J]. 西安交通大学学报, 2008, 42(6): 751-755. ZHANG Hong, CHEN Guican, CHENG Jun, et al. Low power and high speed open-loop residue amplifier for pipelined analog-to-digital converters [J]. Journal of Xi’an Jiaotong University, 2008, 42(6): 751-755.

[4] MCCREARY J L, GRAY P R. All-MOS charge redistribution analog-to-digital conversion techniques I [J]. IEEE Journal of Solid-State Circuits, 1975, 10(6): 371-379.

[5] HUANG Guanying, CHANG Soonjyh, LIU Chuncheng, et al. 10-bit 30Ms/s SAR ADC using a switchback switching method [J]. IEEE Transactions on Very Large Scale Integration Systems, 2013, 21(3): 584-588.

[6] LIU Chuncheng, CHANG Soonjyh, HUANG Guanying, et al. A 10-bit 50-Ms/s SAR ADC with a monotonic capacitor switching procedure [J]. IEEE Journal of Solid-State Circuits, 2010, 45(4): 731-740.

[7] TANG H, SUN Zhuochao, CHEW K W R, et al. A 5.8 nW 9.1-ENOB 1-Ks/s local asynchronous successive approximation register ADC for implantable medical device [J]. IEEE Circuits and Systems Society, 2013, 22(10): 2220-2224.

[8] SUN Lei, DAI Qinyuan, LEE C C, et al. Analysis on capacitor mismatch and parasitic capacitors effect of improved segmented-capacitor array in SAR ADC [C]∥ Proceedings of the Third International Symposium on Intelligent Information Technology Application. Piscataway, NJ, USA: IEEE, 2009: 280-283.

[9] GINSBURG B P, CHANDRAKASAN A P. 500-Ms/s 5-bit ADC in 65-nm CMOS with spilt capacitor array DAC [J]. IEEE Journal of Solid-State Circuits, 2007, 42(4): 739-747.

[10]ZHU Yan, CHAN Chihang, CHIO U F, et al. Split-SAR ADCs: improved linearity with power and speed optimization [J]. IEEE Transactions on Very Large Scale Integration Systems, 2013, 22(2): 362- 383.

[11]LIN Chihung, BULT K. A 10-b 500-M sample/s CMOS CDAC in 0.6 mm2[J]. IEEE Journal of Solid-State Circuits, 1998, 33(12): 1948-1958.

[12]YANG Yongkui, LIU Xin, ZHOU Jun, et al. A 0.5V 16nW 8.08-ENOB SAR ADC for ultra-low power sensor applications [C]∥ Proceedings of 2013 IEEE MTT-S International Microwave Workshop Series on RF and Wireless Technologies for Biomedical and Healthcare Applications. Piscataway, NJ, USA: IEEE, 2013: 1-3.

[13]ZOU Xiaodan, XU Xiaoyuan, YAO Libin, et al. A 1-V 450-nW fully integrated programmable biomedical sensor interface chip [J]. IEEE Journal of Solid-State Circuits, 2009, 44(4): 1067-1077.

(编辑 刘杨)

A Successive Approximation Register Analog-to-Digital Converter for Implantable Biomedical Devices

ZHANG Hong,ZHANG Mudan,ZHANG Jie,ZHAO Yang,ZHANG Ruizhi

(School of Electronics and Information Engineering, Xi’an Jiaotong University, Xi’an 710049, China)

A hybrid encoded successive approximation register (SAR) analog-to-digital converter (ADC) with constant common-mode control logic is presented to meet the requirements of ultra low power consumption and high resolution for implantable biomedical devices. The hybrid encoded structure of the split capacitive digital to analog converter (CDAC) employed in the SAR-ADC combines the low-power feature of binary encoded CDAC and the high-linearity advantage of thermometer encoded CDAC. The constant common-mode control logic has the advantage of ultra low dynamic power dissipation. The schematic and layout of a 10 bit SAR ADC are designed using the HHNEC 0.35 μm CMOS technology. Simulation results after layout parasitic extraction show that the proposed SAR-ADC operates under a power supply range of 1.8-3 V, and achieves an effective bit of 9.4 under a sampling rate of 103s-1. The current consumption is only 60 nA, which is lower than those recently reported SAR ADCs with similar fabrication technologies. It can be concluded that the proposed converter is suitable for implantable devices such as cardiac pace makers.

biomedical devices; implantable; ultra low power; successive approximation register; analog-to-digital converter

2014-08-27。

张鸿(1978—),男,副教授;张瑞智(通信作者),男,教授。

国家自然科学基金资助项目(61474092);陕西省科技计划资助项目(2014K05-14);中央高校基本科研业务费专项资金资助项目(xjj2013088)。

时间:2014-13-30

10.7652/xjtuxb201502008

TN432

A

0253-987X(2015)02-0043-06

网络出版地址:http:∥www.cnki.net/kcms/detail/61.1069.T.20141230.0823.002.html